# 大規模ボリュームデータの 並列可視化環境の構築

-- 専用ハードウェアを用いた実装--

森、中田、高山、丸山、生雲、 津邑、五島、中島、富田 京都大学

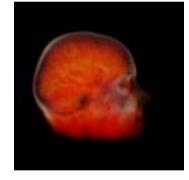

# [背景1]ボリュームレンダリング処理

3次元空間上の数値データを色c,透明度tに対応づけて可視化する。

具体的には、視線上のボクセルの値を 視点に近い順に $v_0, v_1, v_2$  とすると

データ提供: (株)KGT

$$C_k = \sum_{i=0}^k (i - t(v_i)) \cdot c(v_i) \cdot \prod_{j=0}^{i-1} t(v_i)$$

$$T_k = \prod_{i=0}^k t(v_i)$$

畳み込み演算

$t(v_i)$ ,  $c(v_i)$ はそれぞれボクセル値 $v_i$ の透明度、色を表す

出展:

http://www.volvis.org/ の

サンプルデータ

ピクセル値の計算.... 色(RGB)と透明度の累積加算

## [背景2] ボリュームレンダリング専用 並列計算機 ReVolver/C40

#### ReVolver/C40の目標

512³のボリュームデータの 実時間可視化

#### ReVolver/C40の特徴

- レイキャスティング法

- サンプリング方法の単純化

- 3次元メモリ構成(三重化)

### ReVolver/C40でのボリュームレンダリング

- パイプライン化が容易

- メモリアクセスが速度を支配

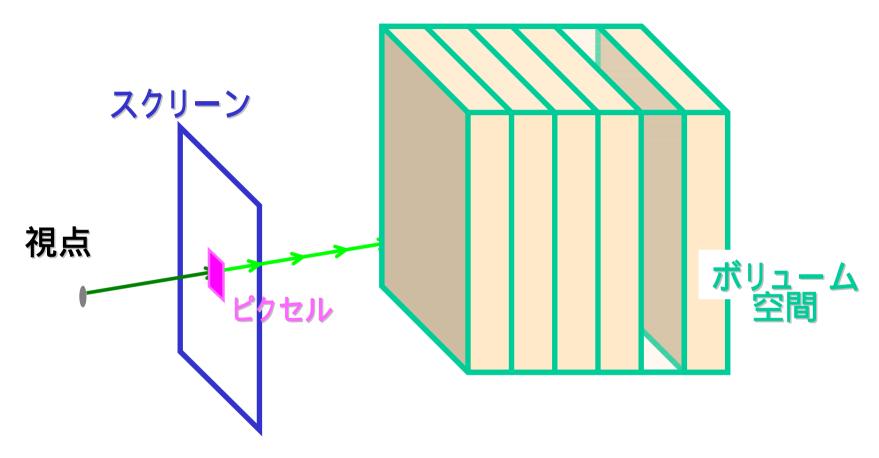

### 並列化手法(基本方針)

- ボリュームデータを複数のサブボリュームに分割し計算/ード に分散配置

- 各ノードでサブボリューム毎に畳み込み演算

- 各ノードで得られた画像と画素毎の透明度を、視点からの距離の順番に従って順次パイプライン的に合成

#### 大規模ボリュームデータの並列可視化

- データサイズ4096<sup>3</sup>のボリュームデータ

- 6 4GB (8bit voxel)

- 2048<sup>2</sup>クラスのスクリーン

- 16Gsample/frame (補間なし、外部光源なし) 480Gsample/s (秒間30枚) メモリバンド幅480GB/s

- ・可視化処理に対する3つのアプローチ

- 専用ハードウェアの開発

- 汎用PCグラフィックスカードを用いた実装

- » ブレンディング + テクスチャマッピング (SWoPP2003で発表予定)

- ソフトウェアのみで実装……非構造格子等への対応

#### 可視化専用ハードウェアを用いた実装

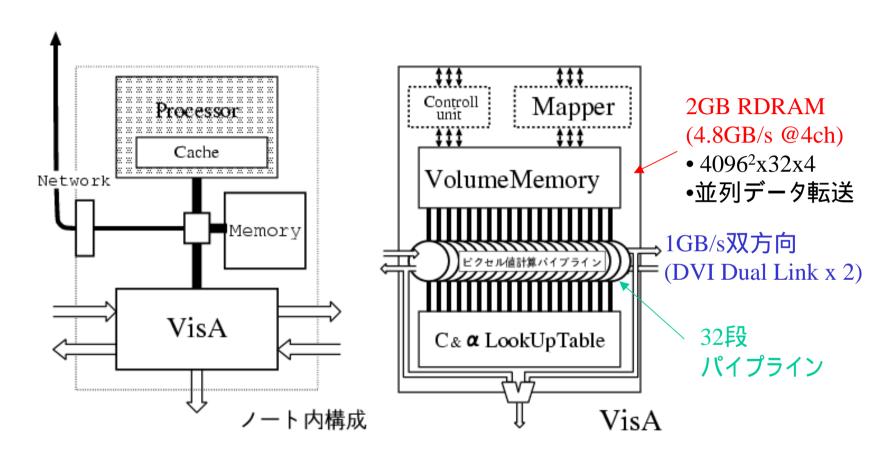

- Visualization Accelerator (VisA)

- ReVolver/C40のアーキテクチャをベースにする

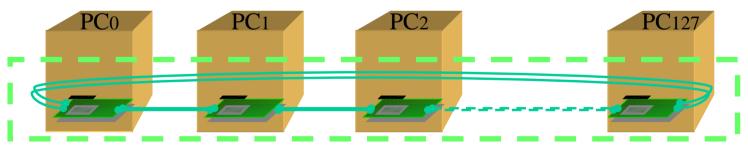

- 128ノードのクラスタでパイプライン処理を行う

- 各ノード内では32段パイプライン構造

- ボリュームデータは、スライスの集合体である「サブボ リューム」に分割して格納

#### VisAの構成

## VisAの主な機能ユニット

- 1. ピクセル値計算パイプライン

- A) 1ノードあたり32段の畳み込み演算パイプライン

- B) RGB 各16bitの固定小数点演 算@128MHz

- 2. Look Up Table(C & LUT)

- A) 8bitのボクセル値をRGB に変換 (伝達関数表)

- B) 畳み込み演算器毎にLUTを配置

- 3. ボリュームメモリ1ノード辺り2GB

- A) 512MB PC600 RDRAM module 16bit 4ch で実現(4.8GB/s)

- B) 4096<sup>3</sup>x32のsubvolumeを4set 三重化 + バックグランド処理 8192x8192x4096 への対応 32bit float ボクセルへの対応 減衰を考慮した光源光による シェーディング

- 4. プリフェッチ機構

- A) Subvolumeへの入射位置と視線 ベクトルに基づきボクセル値を先 読み

- B) メモリユニット1ch辺り8個の量み 込み演算器へのデータ供給(分配)

- 5. VisA間リンク

- A) 1GB/s 双方向リンク

- B) DVI-D Dual Link ケーブル使用

- C) 出力を液晶ディスプレイに直結可

- D) リング構造にすれば早期視線終端(Early Ray Termination)も可能

- 6. Mapper

- A) 主記憶からのデータ転送時にonthe-fly でデータ形式を変換

### VisA プロトタイプ

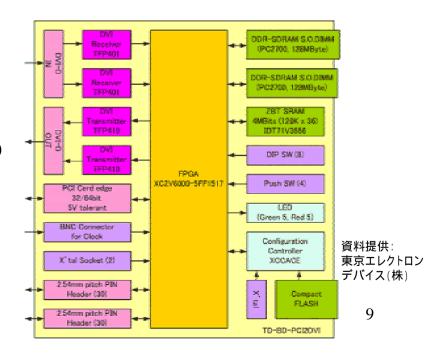

#### VisAの基本性能の約半分の能力を持ったプロトタイプボード

Xilinx VirtexII FPGA, DDR-SDRAM 2ch, DVI-D Dual Link In/Out を備えた評価用PCIボードとして東京エレクトロンデバイス(株)と共同開発

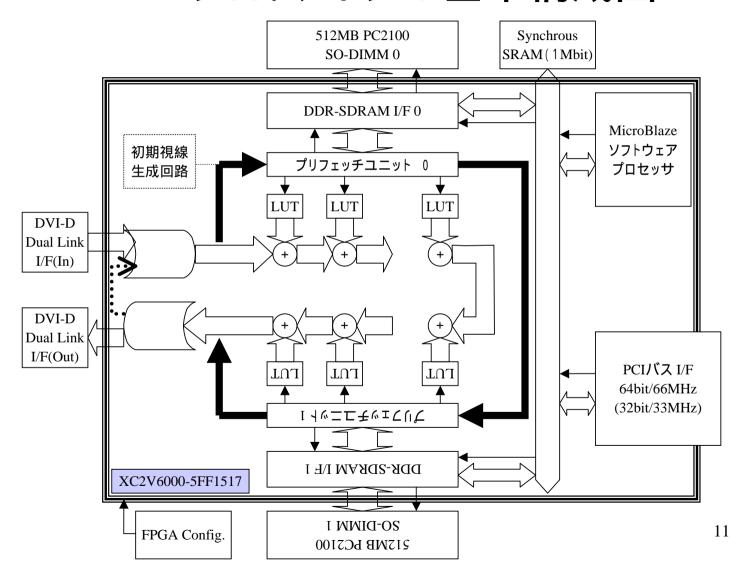

- 512MB DDR-SDRAM (PC2100) を2ch実装

- 合計で 4.2GB/s のメモリバンド幅 (PC2700 でも動作可能??)

- 各ch毎に独立動作可能

- Xilinx社製 FPGA Virtex-II 6000-5 搭載

- •600万システムゲート

- 144個の組み込み乗算器(18bit x 18bit) 畳み込み演算器に利用

- 144個の18Kbit SlectRAM Block (Dual Port Memory やFIFO構成が可能) LUT や Prefetch Buffer に利用

- MicroBlaze ソフトウェアプロセッサコア

- Compact Flashカードによる 高速コンフィギュレーション

- 64bit / 66MHz PCI インタフェース (PCI32/33もOK)

- •DVI-D Dual LinkインタフェースをIn/Out各1ch装備

- 入出力それぞれ990MB/s (理論最大)のリンクスピード

- 液晶ディスプレイに直結可

# VisA プロトタイプボード

資料提供:東京エレクトロンデバイス(株)

### VisA プロトタイプの基本構成図

## まとめ

#### 現状

- 1. ピクセル値演算回路(単体)が133MHz で動作することをCAD上で確認 組み込み乗算器やSelectRAMに関しては明示的にレイアウト指定

- 2. ボリュームデータを三重化する場合の、ボリュームメモリ上のデータレイア ウトとプリフェッチアルゴリズムの検討

- 3. 評価ボードを5/23に入手

#### 今後の予定

- 1. 軸並行投影モードでのボリュームレンダリング処理の実装 (評価ボード単体試験)

- 2. DVI-D Dual Link を VisA間リンクとして使った通信実験

- 3. 各部の詳細設計と実装

- 4. ピクセル並列処理とボクセル並列処理を併用してデータの三重化を不要にするアルゴリズムに対応したプリフェッチアルゴリズムと演算回路構成の検討

- 5. 評価ボードの他のアプリケーションへの応用検討(分散共有メモリボード、数値計算アクセラレータ等) 12