# 計算機アーキテクチャ

京都大学情報学研究科

教授 富田眞治

## 用語知識調査（，，，×で記入）

M e g a   G i g a   T e r a

フォン ノイマン

機械命令セット

プログラムカウンタ

レジスタ

スタックマシン

アドレッシングモード

手続き（関数）呼出し

再帰呼出し

浮動小数点数

2の補数

C I S C と R I S C

プロセススイッチ

割込みと例外

排他的論理和

S R A MとD R A M

キャッシュメモリ

仮想記憶

連想メモリ

共有メモリ

命令パイプライン

分岐予測

投機実行

スーパスカラ

V L I W

アウトオブオーダ実行

コンパイラ

並列処理

富田眞治

略歴

1945 出雲大社生まれ

1968 京大・工・電子工学科卒

1973 同工学研究科電気工学専攻

博士課程修了, 工学博士

合成音声多重出力システムの開発

1973 京大・工・情報工学科助手

1978 同助教授

低レベル並列計算機:

QA - 1, QA - 2 の開発

グラフィックス用並列計算機

EXPERTS の開発

1986 九州大学教授

可変構造型並列計算機の開発

スーパースカラ計算機の開発

レイトレーシングマシンの開発

ベクトル計算機の開発

1991 京都大学教授(情報工学科)

超並列処理マシンの開発

超並列処理応用の研究

ボリュームレンダリングマシン

プロセッサ・アーキテクチャの研究

1998 京都大学情報学研究科教授

2006 同研究科長

## 著書

- VLSIコンピュータ, 岩波, 1984

- 並列計算機構成論, 昭晃堂, 1986

- 計算機システム工学, 昭晃堂, 1988

- 並列処理マシン, オーム社, 1989

- 並列処理機構, 丸善, 1989

- コンピューターアーキテクチャ I, 丸善, 1994

- 並列コンピュータ工学, 昭晃堂, 1996

- コンピューターアーキテクチャ, 第2版, 丸善,

2000

- 情報社会とコンピュータ、昭晃堂、2005

- : 単著

## 学会

情報処理学会理事(平成7, 8, 10, 11年度)

同関西支部長(平成13, 14年度)

電子情報通信学会フェロー(平成12年度)

情報処理学会フェロー(平成13年度)

情報処理学会功績賞(平成18年度)

# コンピュータの動作原理

理解の深さのレベル

| 車       | コンピュータ    |          |

|---------|-----------|----------|

| 利用 交通手段 | 文書作成、数値計算 | アプリケーション |

| 操作 運転   | プログラム作成   | プログラミング  |

原理、構成要素と相互関連

|                      |                                      |         |

|----------------------|--------------------------------------|---------|

| エンジン、ハンドル<br>ブレーキ、車軸 | 演算装置、制御装置<br>記憶装置、入出力装置<br>プログラム制御方式 | アーキテクチャ |

|----------------------|--------------------------------------|---------|

構成要素の詳細構造

|                     |                  |              |

|---------------------|------------------|--------------|

| エンジンの構造<br>材料 チタン合金 | 演算器の構造<br>トランジスタ | 論理設計<br>デバイス |

|---------------------|------------------|--------------|

# 講義内容

- 基本構造: ノイマン型コンピュータ

- 演算装置の構成

- コンピュータの設計

- 記憶装置の構成

- 制御装置の構成とCISC / RISC

- 命令レベル並列処理とコンパイラ

- 並列コンピュータ概論

入門的

特論的

地球シミュレータ: 5120台のプロセッサ

40 TFLOPS

京速コンピュータ: 10 PFLOPS

# 1 基本単位

1.1 ビットとは: binary digit

2進数1桁の数字: 0, 1

ビット: b, 8ビット: バイトB,

IBMでは

16ビット: 半語HW, 32ビット: 語W,

64ビット: 倍長語DW, 128ビット: 拡張語EW

Intelでは

16ビット: ワード, 32ビット: ダブルワード,

64ビット: クワッドワード(Quad Word),

128ビット: ダブルクワッドワード

コンピュータ

電子回路: 2つの安定

状態 ONまたはOFF

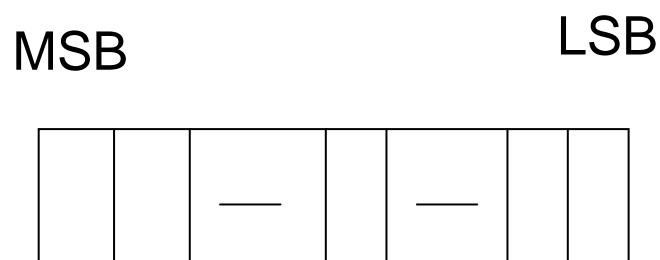

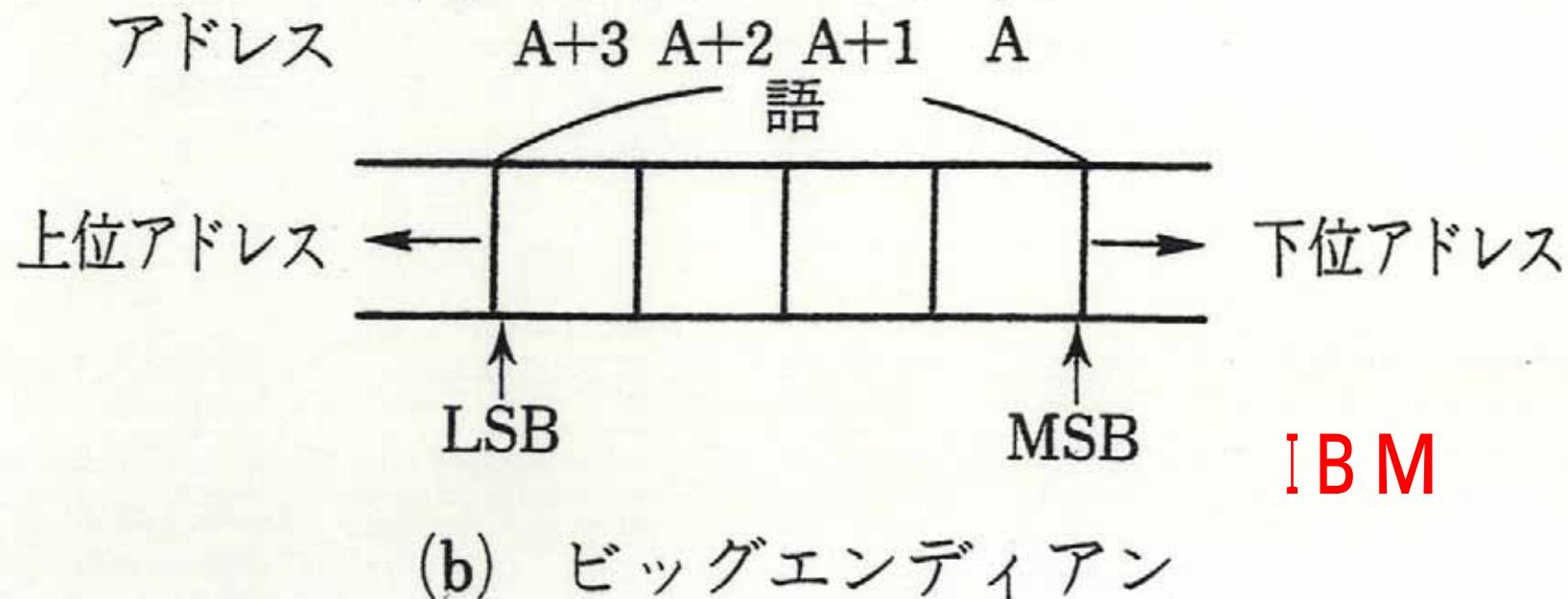

## MSBとLSB

MSB:最上位桁

LSB:最下位

# ビット列で表現できるもの

## 2進数

r進数  $(a_{n-1}a_{n-2}\dots a_0)_r = a_{n-1}r^{n-1} + a_{n-2}r^{n-2} + \dots + a_0r^0$

0  $a_i < r$

10進数 :  $r=10$

$$(253)_{10} = 2^2 * 10^2 + 5 * 10^1 + 3 * 10^0$$

2進数 :  $r=2$

$$(01011010)_2 = 2^6 + 2^4 + 2^3 + 2^1 = (90)_{10}$$

8ビットの2進数

$$(00000000)_2 = (0)_{10} \sim (11111111)_2 = (255)_{10}$$

## 2進数

### r進数との相互変換

$$(a_{n-1}a_{n-2}\dots a_0)_r = a_{n-1}r^{n-1} + a_{n-2}r^{n-2} + \dots + a_0r^0$$

### 2進数, 8進数の相互変換: 例 $(90)_{10}$

$$(1011010)_2 \quad (1011010)_2 \quad (132)_8$$

$$(a_{n-1}a_{n-2}\dots a_0)_2 = a_{n-1}2^{n-1} + a_{n-2}2^{n-2} + \dots + a_02^0 = \quad 0 \quad a_i < r$$

.....

$$(a_82^2 + a_72^1 + a_62^0)2^6 + \quad 8^2$$

$$(1011010)_2 = 2^6 + 2^4 + 2^3 + 2^1 = 90$$

$$(a_52^2 + a_42^1 + a_32^0)2^3 + \quad 8^1$$

$$(a_22^2 + a_12^1 + a_02^0) \quad 8^0$$

## 2進数と16進数の相互変換

### 16進数

$$(a_{n-1}a_{n-2}\dots a_0)_{16} = a_{n-1}16^{n-1} + a_{n-2}16^{n-2} + \dots + a_016^0$$

$$0 \leq a_i < 16$$

16進数の1~9、10~15の表現: 1,2,3,...,9,A,B,C,D,E,F

2進数との対応: 1010:A, 1011:B, 1100:C, 1101:D, 1110:E, 1111:F

2進数, 16進数の相互変換: 例  $(90)_{10}$

$$(01011010)_2 \quad (0101\ 1010)_2 \quad (5A)_{16}$$

$$(a_{n-1}a_{n-2}\dots a_0)_2 = a_{n-1}2^{n-1} + a_{n-2}2^{n-2} + \dots + a_02^0 =$$

.....

$$(a_{11}2^3 + a_{10}2^2 + a_92^1 + a_82^0)2^8 + 16^2$$

$$(a_72^3 + a_62^2 + a_52^1 + a_42^0)2^4 + 16^1$$

$$(a_32^3 + a_22^2 + a_12^1 + a_02^0) + 16^0$$

## 2進数と10進数

2進数 10進数

$$(a_{n-1}a_{n-2}\dots a_0)_r =$$

$$a_{n-1}r^{n-1} + a_{n-2}r^{n-2} + \dots + a_0r^0$$

$$(1011010)_2 = 2^6 + 2^4 + 2^3 + 2^1 = 90$$

# 10進整数 2進数

$$\begin{aligned}

(N)_{10} &= (a_{n-1}a_{n-2}\dots a_0)_2 \\

&= (a_{n-1}a_{n-2}\dots a_1) * 2 + a_0 \\

&= (a_{n-1}a_{n-2}\dots a_2) * 2 + a_1) * 2 + a_0

\end{aligned}$$

$$10\text{進数} / 2 = \text{商}_0 + \text{余り}_0$$

$$\text{商}_i / 2 = \text{商}_{i+1} + \text{余り}_{i+1}$$

商      余り

$$90 \div 2 \quad 45 \qquad \qquad 0 \qquad a_0$$

$$45 \div 2 \quad 22 \qquad \qquad 1 \qquad a_1$$

$$22 \div 2 \quad 11 \qquad \qquad 0 \qquad a_2$$

$$11 \div 2 \quad 5 \qquad \qquad 1 \qquad a_3$$

$$5 \div 2 \quad 2 \qquad a_6 \qquad 1 \qquad a_4$$

$$2 \div 2 \quad 1 \qquad \qquad \qquad 0 \qquad a_5$$

## 10進小数 2進小数

$$(0.N)_{10} = (0.a_{-1}a_{-2}\dots a_{-m})_2$$

$$2 * (0.N)_{10} = a_{-1} + (0.a_{-2}\dots a_{-m})_2$$

$$2 * (10\text{進数}) = \text{整数部}_{-1} + \text{小数部}_{-1}$$

$$2 * \text{小数部}_{-i} = \text{整数部}_{-(i+1)} + \text{小数部}_{-(i+1)}$$

(0.1)<sub>10</sub>は？

$$2 * 0.1 = 0.2$$

$$2 * 0.2 = 0.4$$

$$2 * 0.4 = 0.8$$

$$2 * 0.8 = 1.6$$

$$2 * 0.6 = 1.2$$

$$2 * 0.2 = 0.4$$

$$2 * 0.4 = 0.8$$

$$2 * 0.8 = 1.6$$

$$2 * 0.6 = 1.2$$

整数部 0

整数部 0

整数部 0

整数部 1

整数部 1

整数部 0

整数部 0

整数部 1

整数部 1

繰り返し

循環小数

0.00011

0.00011

有限桁の問題  $(10 / 3) * 3$  を電卓

で計算すると？

## その他ビット列で表されるもの：符号

漢字： 2バイト符号(16進4桁)

漢字：第1，2水準

富:4959, 田:4544,

真:3F3F, 眞:6243, 治:3C23

パターン

プリンタでパターン用意

プロセッサ

2バイトデータ

4 5 4 4

24 × 24

ビット

表示

**情報理論での情報量の「ビット」**

確率  $p$  で生起する事象が起こったことにより

得られる情報量  $-\log_2 p$  ビット

**N個の事象からなる情報源の情報量**

$$-\sum p_i \log_2 p_i$$

**4つの事象 0 , 1 , 2 , 3 の生起確率**

1/4 , 1/4 , 1/4 , 1/4 のとき

**情報量: 2 ビット**

**符号化: 0 00 , 1 01 , 2 10 , 3 11**

**2 ビット**

4つの事象  $0, 1, 2, 3$  の生起確率

$1/2, 1/4, 1/8, 1/8$  のとき

情報量: 1.75 ビット

符号化: 0 00, 1 01, 2 10, 3 11

2 ビット

符号化: 0 0, 1 10, 2 110, 3 111

1.75 ビット

事象列 03201

↓ 符号化 ↑

符号列 011110010

## 1.1.2 各種の量

K:キロ  $2^{10}$ ,  $10^3$

M:メガ  $2^{20}$ ,  $10^6$

G:ギガ  $2^{30}$ ,  $10^9$

T:テラ  $2^{40}$ ,  $10^{12}$

P:ペタ  $2^{50}$ ,  $10^{15}$

キャッシュメモリ:64KB

メインメモリ:512MB

パソコン周波数:2GHz

ディスク容量:100GB

地球シミュレータ性能:40TFLOPS

近未来のスーパコン:1PFLOPS

FLOPS:Floating Point Operations / sec

m:ミリ  $10^{-3}$

$\mu$ :マイクロ  $10^{-6}$

n:ナノ  $10^{-9}$

p:ピコ  $10^{-12}$

f:フェムト  $10^{-15}$

ディスク速度:10msec

LSI設計寸法: $0.065\ \mu m$

光の伝播速度:3.3nsec/m

クロックサイクルタイム:1nsec

ゲート遅延時間:30psec

DRAMのコンデンサ容量:50fF

# 単位の表現

| 記号    | 読み方  | SI接頭語  | 日本語     | 備考                     |

|-------|------|--------|---------|------------------------|

| a     | アト   | atto-  | 指 (シ)   | $10^{-18}$             |

| f     | フェムト | femto- | 須 (シュユ) | $10^{-15}$             |

| p     | ピコ   | pico-  | 漠 (バク)  | $10^{-12}$             |

| n     | ナノ   | nano-  | 塵 (ジン)  | $10^{-9}$              |

| $\mu$ | マイクロ | micro- | 微 (ビ)   | $10^{-6}$              |

| m     | ミリ   | milli- | 毛 (モウ)  | $10^{-3}$              |

| c     | センチ  | centi- | 厘 (リン)  | $10^{-2}$              |

| d     | デシ   | deci-  | 分 (ブ)   | $10^{-1}$              |

| da    | デカ   | deca-  | 十 (ジュウ) | $10^1$                 |

| h     | ヘクト  | hecto- | 百 (ヒャク) | $10^2$                 |

| k     | キロ   | kilo-  | 千 (セン)  | $10^3$ ( $2^{10}$ )    |

| M     | メガ   | mega-  | 百万 (マン) | $10^6$ ( $2^{20}$ )    |

| G     | ギガ   | giga-  | 十億 (オク) | $10^9$ ( $2^{30}$ )    |

| T     | テラ   | tera-  | 兆 (チョウ) | $10^{12}$ ( $2^{40}$ ) |

| P     | ペタ   | peta-  | 千兆      | $10^{15}$ ( $2^{50}$ ) |

| E     | エクサ  | exa-   | 百京 (ケイ) | $10^{18}$ ( $2^{60}$ ) |

[備考] のカッコ内は、コンピュータのアドレスで用いた場合。

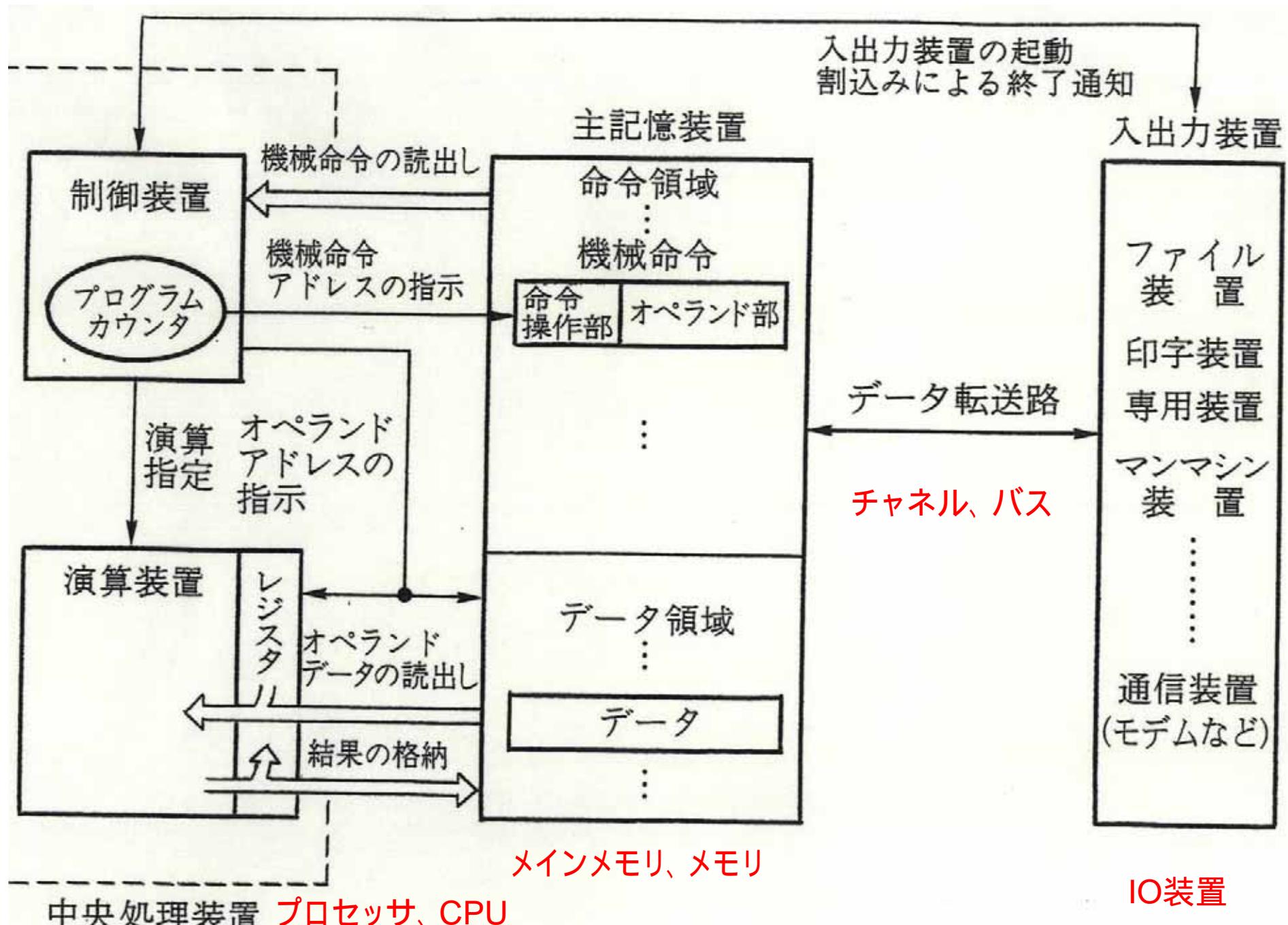

# 1 . 2 動作原理

## 1 . 2 . 1 基本原理

( 1 ) 演算装置

( 2 ) 主記憶装置

( 3 ) 制御装置

( 4 ) 入出力装置

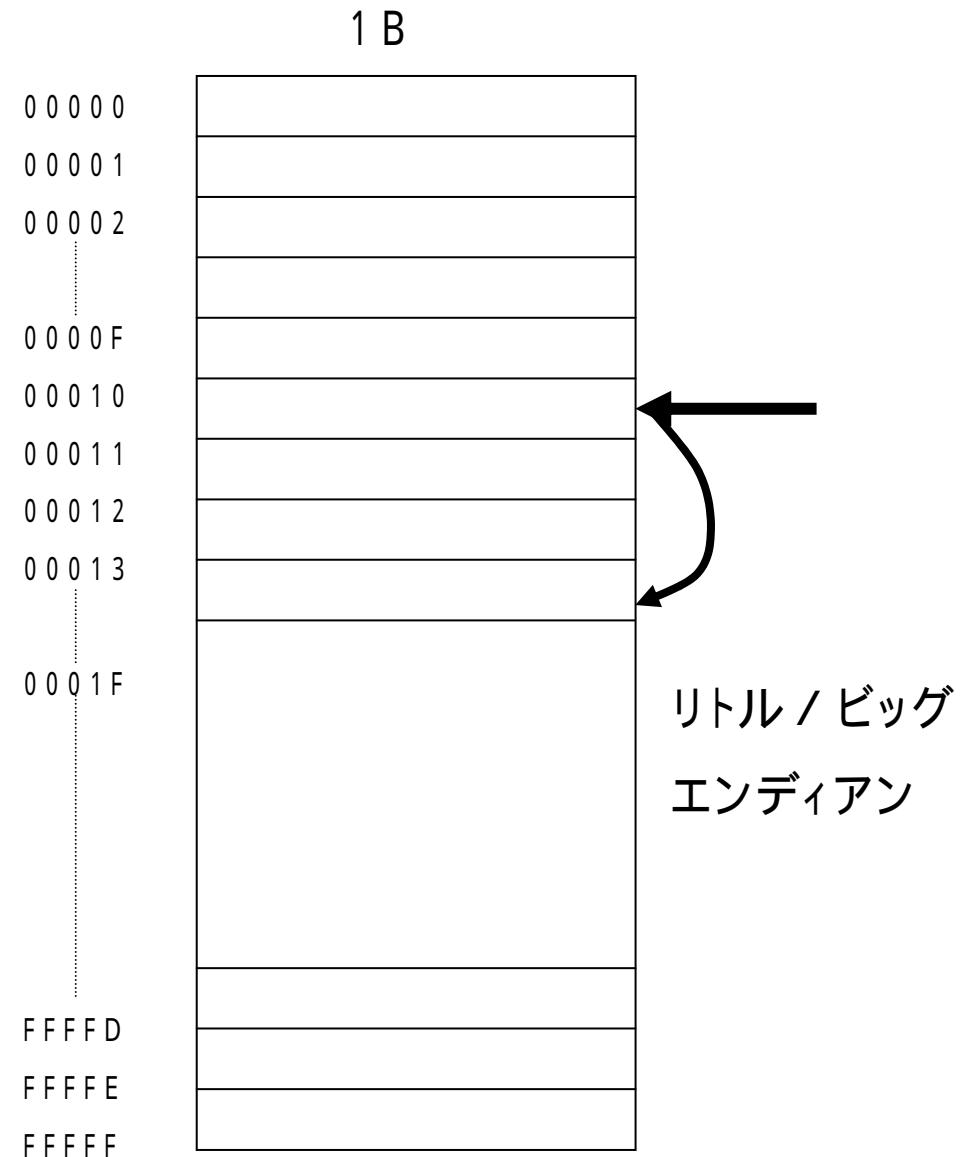

**主記憶装置(メインメモリ, メモリ)**

**バイトアドレッシング**

**リトル / ビッグエンディアン**

**プログラムの格納**

**命令列**

**データ**

1 MBのメモリ

20ビットアドレス →

16進5桁アドレス

00000 ~ FFFFF

R / W →

バイト数 →

Read: Load ←

Write: Store →

図 1.2 リトル/ビッグエンディアン

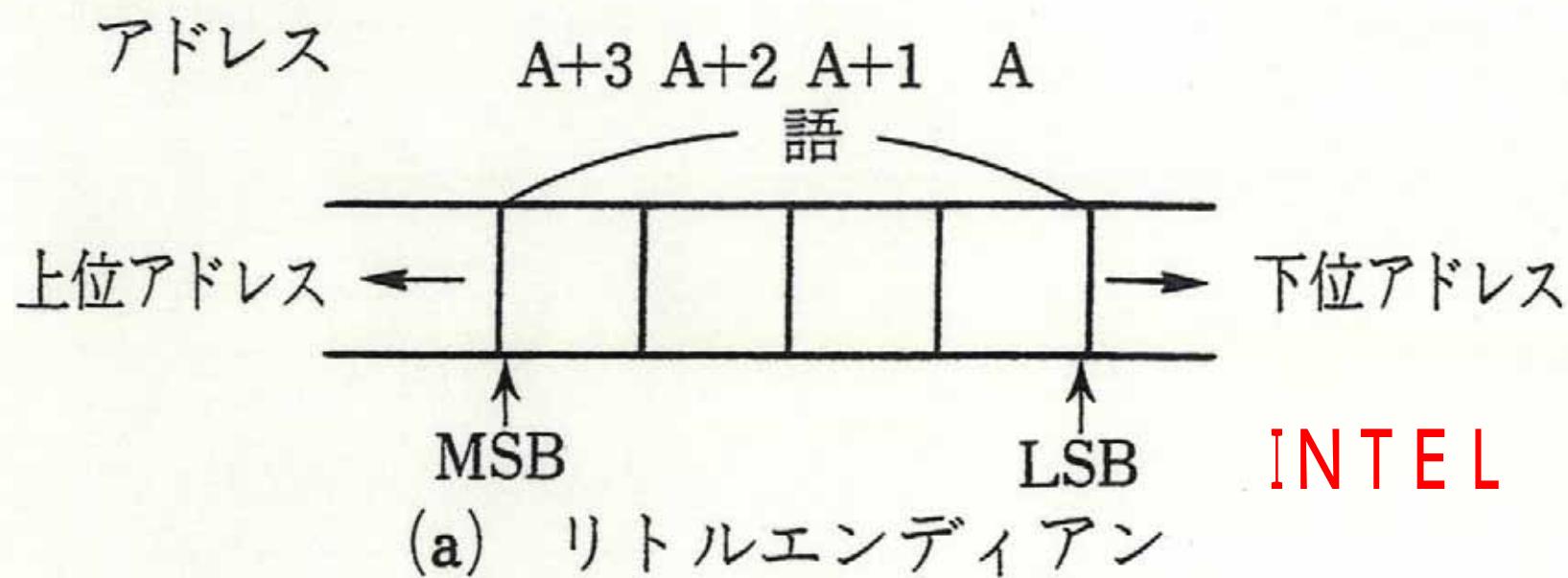

**実際の主記憶装置**

**記憶階層方式**

**例:頭の中,メモ帳,机上,引出し,本箱,倉庫**

**キャッシュメモリ**

**仮想記憶方式**

**線形記憶と連想記憶**

**アドレス 内容:線形記憶**

**内容 アドレス:連想記憶**

図 4.5 記憶階層方式

# DRAMについての私の経験

## 1Kb DRAM

- 1974に購入(東光株式会社)

- アクセスタイム 350nsec

- 容量 256KB

- 価格 1000万円

## 256Mb DRAM

- 2001年にパソコンのアドオンメモリとして購入

- アクセスタイム 70nsec

- 容量 128MB

- 価格 5000円

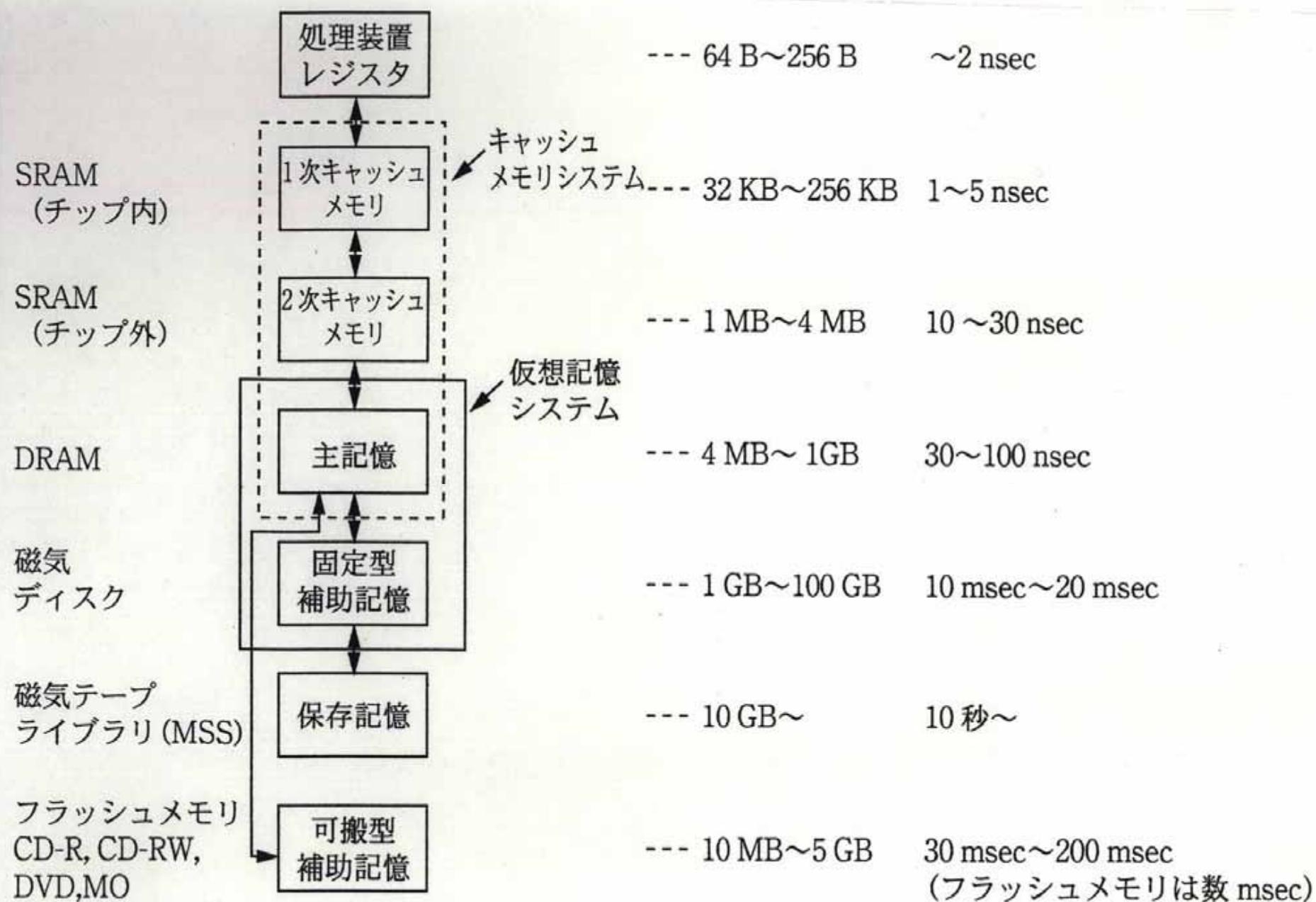

# Power4 Processor Design

- ▶ Power4 Floor Plan and Images of the Instruction Fetch (IFU) & L2 Cache Control Units

- ▶ Power4 Processor Chip Features

- ▶ Two microprocessors, 3-level cache hierarchy

- ▶ >30 GB/s (>500 MHz) interconnection fabric

- ▶ 2200 signal I/O; 170M transistors

- ▶ Configured for 8-way system on MCM

- ▶ CMOS 8S2-SOI technology & copper wiring

- ▶ Microprocessor core

- ▶ > 1GHz clock frequency; 64KB L1 instruction cache

- ▶ 64-bit PowerPC for RS6000 & AS400 systems

- ▶ Out-of-order, speculative, 8-issue superscalar design

- ▶ Memory sub-system

- ▶ 1.5 MB shared L2 caches

- ▶ 32 MB off-chip L3 (on-chip control); Bandwidth > 10GB/s

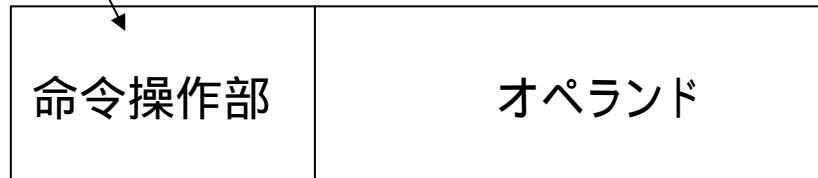

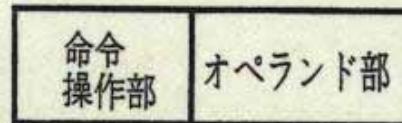

# 機械命令

オペコード

レジスタ: 16個 (4ビット指定)

メモリ: 1 MB (20ビットアドレス)

命令操作部: 加算などの操作指定

オペランド: レジスタやメモリなど演算をされるデータを指定, 0 ~ 3個

2バイト命令

Rd Rd OP Rs

例 MUL R0 R1

4バイト命令

Rd Rd OP Ms

例 ADD R0 A

LOAD:00, STORE:01, ADD:02, MUL:03

dデスティネーション

Sソース

データはすべて4 B長

- ・ 2 オペランド命令

|    |    |    |

|----|----|----|

| OP | Rd | Rs |

|----|----|----|

$$Rd \leftarrow Rd \quad op \quad Rs$$

Rd の内容書き換えられる

- ・ 3 オペランド命令

|    |    |     |     |

|----|----|-----|-----|

| OP | Rd | Rs1 | Rs2 |

|----|----|-----|-----|

$$Rd \leftarrow Rs1 \quad op \quad Rs2$$

Rs1, Rs2 : 内容そのまま

|       |                               |

|-------|-------------------------------|

| 記号表現  | MUL R0 R1                     |

| 16進表現 | 03 01                         |

| 記号表現  | ADD R0 A                      |

| 16進表現 | 02 00020                      |

|       | ↑                             |

|       | データAはメモリの<br>00020アドレスに<br>記憶 |

| 命令番号                    | 命 令         |       | バイトアドレス<br>(16進) | 主記憶内での表現<br>(16進) |

|-------------------------|-------------|-------|------------------|-------------------|

| 1                       | <u>LOAD</u> | R1 A  | 00000            | <u>00100020</u>   |

| 2                       | ADD         | R1 B  | 00004            | 02100024          |

| 3                       | LOAD        | R2 C  | 00008            | 00200028          |

| 4                       | ADD         | R2 D  | 0000C            | 0220002C          |

| 5                       | MUL         | R1 R2 | 00010            | 0312              |

| 6                       | STORE       | E R1  | 00012            | 01100030          |

|                         |             | データ名  |                  | (1.5)             |

| $E = (A + B) * (C + D)$ |             | A     | <u>00020</u>     | 00000010          |

| A ~ E: 4B データ           |             | B     | 00024            | 00000003          |

|                         |             | C     | 00028            | 0000000A          |

|                         |             | D     | 0002C            | 00000011          |

|                         |             | E     | 00030            | ?                 |

アセンブリプログラム

目的プログラム

### ( 3 ) 制御装置

プログラムカウンタ:PC

逐次制御

コントロール駆動 VS データ駆動

プログラムカウンタで指された命令のみ実行

実行可能であっても指されなからら X

## 1.2.2 ノイマンモデル

基本モデル: 1945年、John von Neumann

プログラム内蔵: Stored Program

プログラムの電子的速度での呼び出しと変更

逐次制御: 一つ一つ

低機能命令: 鈍臭いが超速く、八方美人で汎用

線形記憶: 逐次制御と相性極めてよし

存続理由

プログラムの継続利用: 互換性

IBM 360: 1964, Intel IA-32, 8086: 1978

デバイス技術の発展

シンプルな構造: 人間の思考方法と一致

| Date | Inventor: machine                            | Capability                                            | Technical innovations                                           |

|------|----------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------|

| 1642 | Pascal                                       | Addition, subtraction                                 | Automatic carry transfer;<br>complements number representation  |

| 1671 | Leibniz                                      | Addition, subtraction<br>multiplication, division     | "Stepped reckoner" mechanism<br>for multiplication and division |

| 1827 | Babbage: Difference Engine                   | Polynomial evaluation by method of finite differences | Automatic multistep operation                                   |

| 1834 | Babbage: Analytical Engine (never completed) | General-purpose computation                           | Automatic sequence control mechanism (program)                  |

| 1941 | Zuse: Z3                                     | General-purpose computation                           | The first operational general-purpose computers                 |

| 1944 | Aiken: Harvard Mark I                        |                                                       |                                                                 |

**Figure 1.10** Milestones in the development of mechanical computers.

J.P.Hays: Computer Architecture and Organization, McGraw-Hill, 1978

| Generation          | Technologies                                              | Hardware features                                         | Software features                                                             | Representative computers |

|---------------------|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------|

| First<br>(1946–54)  | Vacuum tubes;<br>acoustic memories;<br>CRT memories       | Fixed-point arithmetic                                    | Machine language;<br>assembly language                                        | IAS;<br>UNIVAC           |

| Second<br>(1955–64) | Discrete transistors;<br>ferrite cores;<br>magnetic disks | Floating-point arithmetic; index registers; IO processors | High-level languages;<br>subroutine libraries;<br>batch monitors              | IBM 7094;<br>CDC 1604    |

| Third<br>(1965–74)  | Integrated circuits<br>(SSI and MSI)                      | Microprogramming;<br>pipelining; cache memory             | Multiprogramming;<br>multiprocessing;<br>operating systems;<br>virtual memory | IBM S/360;<br>DEC PDP-8  |

| Fourth?<br>(1975–)  | LSI circuits;<br>semiconductor memories                   |                                                           |                                                                               | Amdahl 470<br>Intel 8748 |

Figure 1.41 Milestones in the development of electronic computers.

J.P.Hays: Computer Architecture and Organization, McGraw-Hill, 1978

表 1.1 デバイス技術の発展<sup>15)</sup>

1946～1958：真空管

ENIAC (1946)

1958～1964：トランジスタ

Philco 社 Transacs-2000 (1958)

1964～1970：SSI/MSI (Small/Medium Scale Integration  $\sim 10^3$  個/チップ<sup>o</sup>)

IBM 360 (1964)

1970～1980：LSI (Large Scale Integration  $10^3 \sim 10^5$  個/チップ<sup>o</sup>)

IBM 370 (1970), Intel 4004 (1971), 1 KbDRAM (1970)

1980～1990：VLSI (Very Large Scale Integration  $10^5 \sim 10^7$  個/チップ<sup>o</sup>)

1990～　　：ULSI (Ultra Large Scale Integration  $10^7 \sim$  個/チップ<sup>o</sup>)

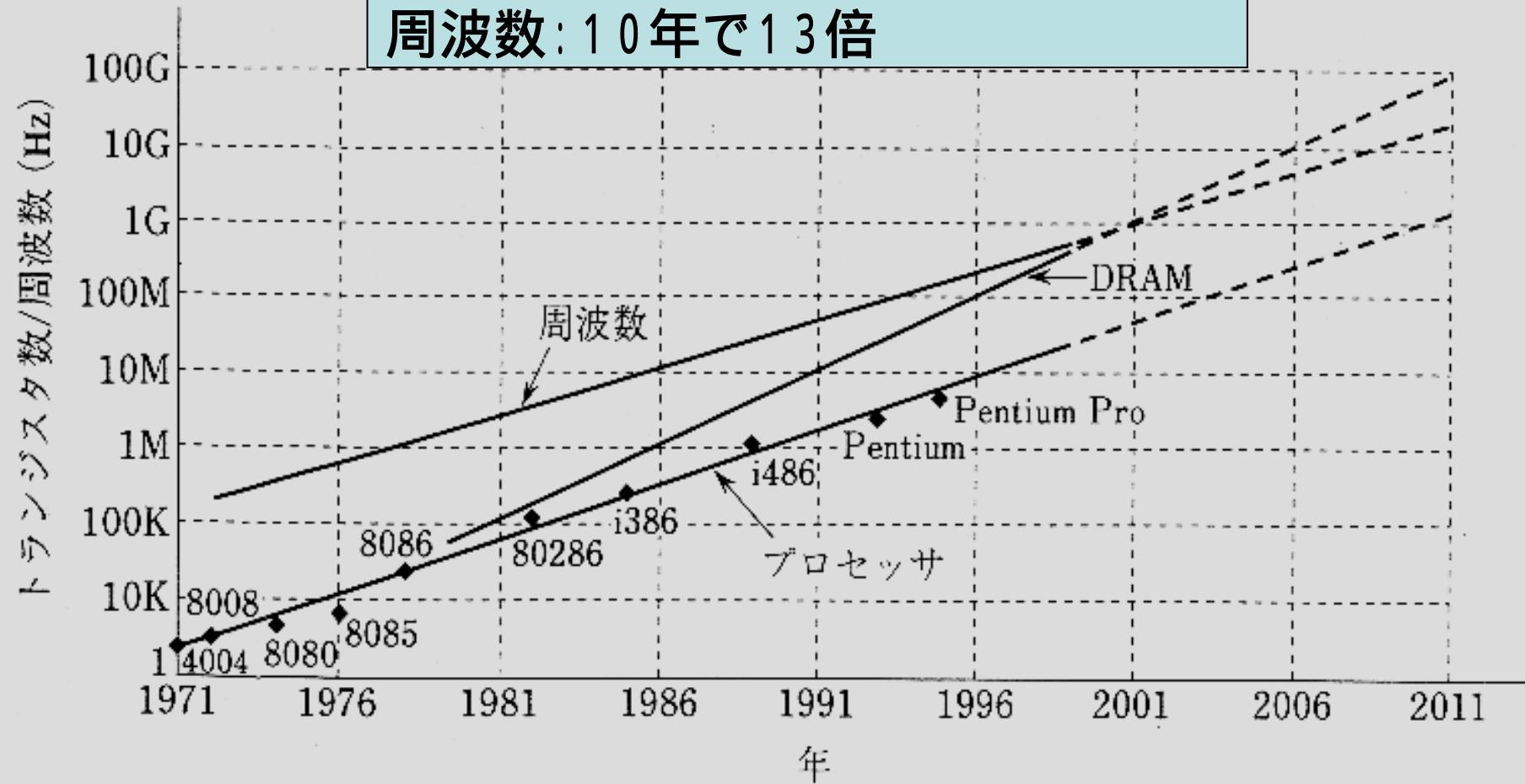

メモリ容量: 10年で100倍

(ムーアの法則: 3年で4倍)

周波数: 10年で13倍

VLSI ロードマップ

# Intelのマイクロプロセッサの 発展過程

| <b>Intel Processor</b>                      | <b>Date Introduced</b> | <b>Max. Clock Frequency at Introduction</b> | <b>Transistors</b> | <b>Register Sizes<sup>1</sup></b>    | <b>Ext. Data Bus Size<sup>2</sup></b> | <b>Max. Extern. Addr. Space</b> | <b>Caches</b>                     |

|---------------------------------------------|------------------------|---------------------------------------------|--------------------|--------------------------------------|---------------------------------------|---------------------------------|-----------------------------------|

| 8086                                        | 1978                   | 8 MHz                                       | 29 K               | 16 GP                                | 16                                    | 1 MB                            | None                              |

| Intel 286                                   | 1982                   | 12.5 MHz                                    | 134 K              | 16 GP                                | 16                                    | 16 MB                           | Note 3                            |

| Intel386 DX Processor                       | 1985                   | 20 MHz                                      | 275 K              | 32 GP                                | 32                                    | 4 GB                            | Note 3                            |

| Intel486 DX Processor                       | 1989                   | 25 MHz                                      | 1.2 M              | 32 GP<br>80 FPU                      | 32                                    | 4 GB                            | L1: 8 KB                          |

| Pentium Processor                           | 1993                   | 60 MHz                                      | 3.1 M              | 32 GP<br>80 FPU                      | 64                                    | 4 GB                            | L1:16 KB                          |

| Pentium Pro Processor                       | 1995                   | 200 MHz                                     | 5.5 M              | 32 GP<br>80 FPU                      | 64                                    | 64 GB                           | L1: 16 KB<br>L2: 256 KB or 512 KB |

| Pentium II Processor                        | 1997                   | 266 MHz                                     | 7 M                | 32 GP<br>80 FPU<br>64 MMX            | 64                                    | 64 GB                           | L1: 32 KB<br>L2: 256 KB or 512 KB |

| Pentium III Processor                       | 1999                   | 500 MHz                                     | 8.2 M              | 32 GP<br>80 FPU<br>64 MMX<br>128 XMM | 64                                    | 64 GB                           | L1: 32 KB<br>L2: 512 KB           |

| Pentium III and Pentium III Xeon Processors | 1999                   | 700 MHz                                     | 28 M               | 32 GP<br>80 FPU<br>64 MMX<br>128 XMM | 64                                    | 64 GB                           | L1: 32 KB<br>L2: 256 KB           |

| <b>Intel Processor</b> | <b>Date Introduced</b> | <b>Microarchitecture</b>         | <b>Clock Frequency at Introduction</b> | <b>Transistors</b> | <b>Register Sizes<sup>1</sup></b>        | <b>System Bus Bandwidth</b> | <b>Max. Extern. Addr. Space</b> | <b>On-Die Caches<sup>2</sup></b>                       |

|------------------------|------------------------|----------------------------------|----------------------------------------|--------------------|------------------------------------------|-----------------------------|---------------------------------|--------------------------------------------------------|

| Pentium 4 Processor    | 2000                   | Intel NetBurst Microarchitecture | 1.50 GHz                               | 42 M               | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 3.2 GB/s                    | 64 GB                           | 12K µop Execution Trace Cache;<br>8KB L1;<br>256-KB L2 |

| Intel Xeon Processor   | 2001                   | Intel NetBurst Microarchitecture | 1.70 GHz                               | 42 M               | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 3.2 GB/s                    | 64 GB                           | 12K µop Trace Cache;<br>8-KB L1;<br>256-KB L2          |

| <b>Intel Processor</b>                                                           | <b>Date Introduced</b> | <b>Microarchitecture</b>                                                                          | <b>Clock Frequency at Introduction</b> | <b>Transistors</b> | <b>Register Sizes<sup>1</sup></b>            | <b>System Bus Bandwidth</b> | <b>Max. Extern. Addr. Space</b> | <b>On-Die Caches<sup>2</sup></b>                  |

|----------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------|--------------------|----------------------------------------------|-----------------------------|---------------------------------|---------------------------------------------------|

| Intel Xeon Processor                                                             | 2002                   | Intel NetBurst Microarchitecture; Hyper-Threading Technology                                      | 2.20 GHz                               | 55 M               | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 3.2 GB/s                    | 64 GB                           | 12K µop Trace Cache; 8-KB L1; 512-KB L2           |

| Intel Xeon Processor MP                                                          | 2002                   | Intel NetBurst Microarchitecture; Hyper-Threading Technology                                      | 1.60 GHz                               | 108 M              | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 3.2 GB/s                    | 64 GB                           | 12K µop Trace Cache; 8-KB L1; 256-KB L2; 1-MB L3  |

| Intel Pentium 4 Processor Supporting Hyper-Threading Technology                  | 2002                   | Intel NetBurst Microarchitecture; Hyper-Threading Technology                                      | 3.06 GHz                               | 55 M               | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 4.2 GB/s                    | 64 GB                           | 12K µop Execution Trace Cache; 8-KB L1; 512-KB L2 |

| Intel Pentium M Processor                                                        | 2003                   | Intel Pentium M Processor                                                                         | 1.60 GHz                               | 77 M               | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 3.2 GB/s                    | 4 GB                            | L1: 64 KB<br>L2: 1 MB                             |

| Intel Pentium 4 Processor Supporting Hyper-Threading Technology at 90 nm process | 2004                   | Intel NetBurst Microarchitecture; Hyper-Threading Technology                                      | 3.40 GHz                               | 125 M              | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 6.4 GB/s                    | 64 GB                           | 12K µop Execution Trace Cache; 16 KB L1; 1 MB L2  |

| Intel Pentium M Processor 755 <sup>3</sup>                                       | 2004                   | Intel Pentium M Processor                                                                         | 2.00 GHz                               | 140 M              | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 3.2 GB/s                    | 4 GB                            | L1: 64 KB<br>L2: 2 MB                             |

| 64-bit Intel Xeon Processor with 800 MHz System Bus                              | 2004                   | Intel NetBurst Microarchitecture; Hyper-Threading Technology; Intel Extended Memory 64 Technology | 3.60 GHz                               | 125 M              | GP: 32, 64<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 6.4 GB/s                    | 64 GB                           | 12K µop Execution Trace Cache; 16 KB L1; 1 MB L2  |

| Intel Processor                                                                 | Date Introduced | Microarchitecture                                                                                                         | Clock Frequency at Introduction | Transistors | Register Sizes <sup>1</sup>                  | System Bus Bandwidth  | Max. Extern. Addr. Space | On-Die Caches <sup>2</sup>                                  |

|---------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------|----------------------------------------------|-----------------------|--------------------------|-------------------------------------------------------------|

| 64-bit Intel Xeon Processor MP with 8MB L3                                      | 2005            | Intel NetBurst Microarchitecture; Hyper-Threading Technology; Intel Extended Memory 64 Technology                         | 3.33 GHz                        | 675M        | GP: 32, 64<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 5.3 GB/s <sup>4</sup> | 1024 GB (1 TB)           | 12K µop Execution Trace Cache; 16 KB L1; 1 MB L2, 8 MB L3   |

| Intel Pentium 4 Processor Extreme Edition Supporting Hyper-Threading Technology | 2005            | Intel NetBurst Microarchitecture; Hyper-Threading Technology; Intel Extended Memory 64 Technology                         | 3.73 GHz                        | 164 M       | GP: 32, 64<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 8.5 GB/s              | 64 GB                    | 12K µop Execution Trace Cache; 16 KB L1; 2 MB L2            |

| Intel Pentium Processor Extreme Edition 840                                     | 2005            | Intel NetBurst Microarchitecture; Hyper-Threading Technology; Intel Extended Memory 64 Technology; Dual-core <sup>5</sup> | 3.20 GHz                        | 230 M       | GP: 32, 64<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 6.4 GB/s              | 64 GB                    | 12K µop Execution Trace Cache; 16 KB L1; 1MB L2 (2MB Total) |

|                |                |

|----------------|----------------|

| Pentium4       | 4004           |

| 発表年: 2000年     | 1971年          |

| 集積度: 4200万TR   | 2300TR         |

| 周波数: 1.4GHz    | 750KHz         |

| ピン数: 478       | 16             |

| 電力: 55W        | ?              |

| 配線層: 6層        | ?              |

| 演算幅: 32ビット     | 4ビット           |

| メモリ 256Mb DRAM | 1Kb DRAM(1970) |

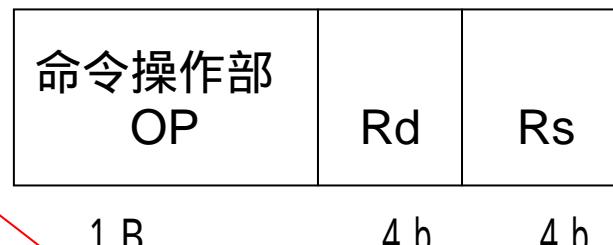

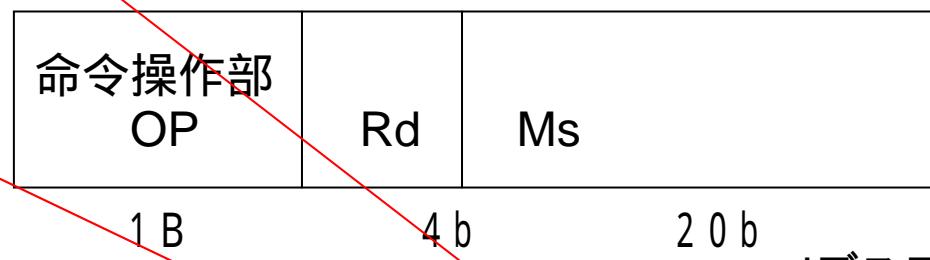

# 1.3 機械命令形式とアドレス方式

## 1.3.1 命令形式

命令操作: 8ビット, レジスタ: 4ビット, メモリ: 12ビット

2, 3アドレス命令形式      ビット数

Md    Ms1 op Ms2    OP    Md    Ms1    Ms2 ( 4 4 )

Md    Md op Ms        OP    Md    Ms ( 3 2 )

1アドレス命令形式

レジスタ - メモリ方式

Rd    Rd op Ms        OP    Rd    Ms ( 2 4 )

( 含 Rd    Rd op Rs ,    OP    Rd    Rs ( 1 6 )

Rd    Rs1 op Rs2 )    OP    Rd    Rs1    Rs2 ( 2 0 )

|     |       |      |       |        |

|-----|-------|------|-------|--------|

|     |       |      | LOAD  | R1, A  |

|     | ADD   | B, A | ADD   | R1, B  |

| (a) | ADD   | C, D | LOAD  | R2, C  |

|     | MUL   | B, C | ADD   | R2, D  |

|     | STORE | E, B | MUL   | R2, R1 |

|     |       |      | STORE | E, R2  |

|     |       |   |       |        |

|-----|-------|---|-------|--------|

|     | LOAD  | A | LOAD  | R1, A  |

|     | ADD   | B | LOAD  | R2, B  |

|     | STORE | T | ADD   | R1, R2 |

| (c) | LOAD  | C | LOAD  | R3, C  |

|     | ADD   | D | LOAD  | R4, D  |

|     | MUL   | T | ADD   | R3, R4 |

|     | STORE | E | MUL   | R1, R3 |

|     |       |   | STORE | E, R1  |

|     |       |   |                         |  |

|-----|-------|---|-------------------------|--|

|     | PUSH  | A |                         |  |

|     | PUSH  | B | $E = (A + B) * (C + D)$ |  |

|     | ADD   |   |                         |  |

| (e) | PUSH  | C |                         |  |

|     | PUSH  | D |                         |  |

|     | ADD   |   |                         |  |

|     | MUL   |   |                         |  |

|     | STORE | E |                         |  |

|                 | (a) | (b) | (c) | (d) | (e) |

|-----------------|-----|-----|-----|-----|-----|

| 命令フェッチ回数(実行命令数) | 4   | 6   | 7   | 8   | 8   |

| 主記憶データアクセス回数    | 11  | 5   | 7   | 5   | 5   |

| 必要メモリ量(ビット)     | 128 | 136 | 140 | 168 | 124 |

| <b>処理時間</b>     | 25  | 13  | 17  | 13  | 13  |

図 1.5 各種機械命令形式の評価 ( $E = (A+B) * (C+D)$  の場合)

(a) 2アドレス命令形式, (b) 1アドレス命令形式 (レジスタ-メモリ方式), (c) 1アドレス命令形式 (アキュムレータ方式), (d) 1アドレス命令形式 (ロードストア方式), (e) 0アドレス命令形式

## アキュムレータ方式

|     |           |       |            |

|-----|-----------|-------|------------|

| ACC | ACC op Ms | OP    | Ms( 2 0 )  |

| Md  | ACC       | STORE | Md ( 2 0 ) |

| ACC | Ms        | LOAD  | Ms ( 2 0 ) |

## ロードストア方式

|    |            |       |    |           |            |

|----|------------|-------|----|-----------|------------|

| Rd | Rs1 op Rs2 | OP    | Rd | Rs1       | Rs2( 2 0 ) |

| Rd | Rd op Rs   | OP    | Rd | Rs( 1 6 ) |            |

| Rd | Ms, Md     | LOAD  | Rd | Ms( 2 4 ) |            |

|    |            | STORE | Md | Rs( 2 4 ) |            |

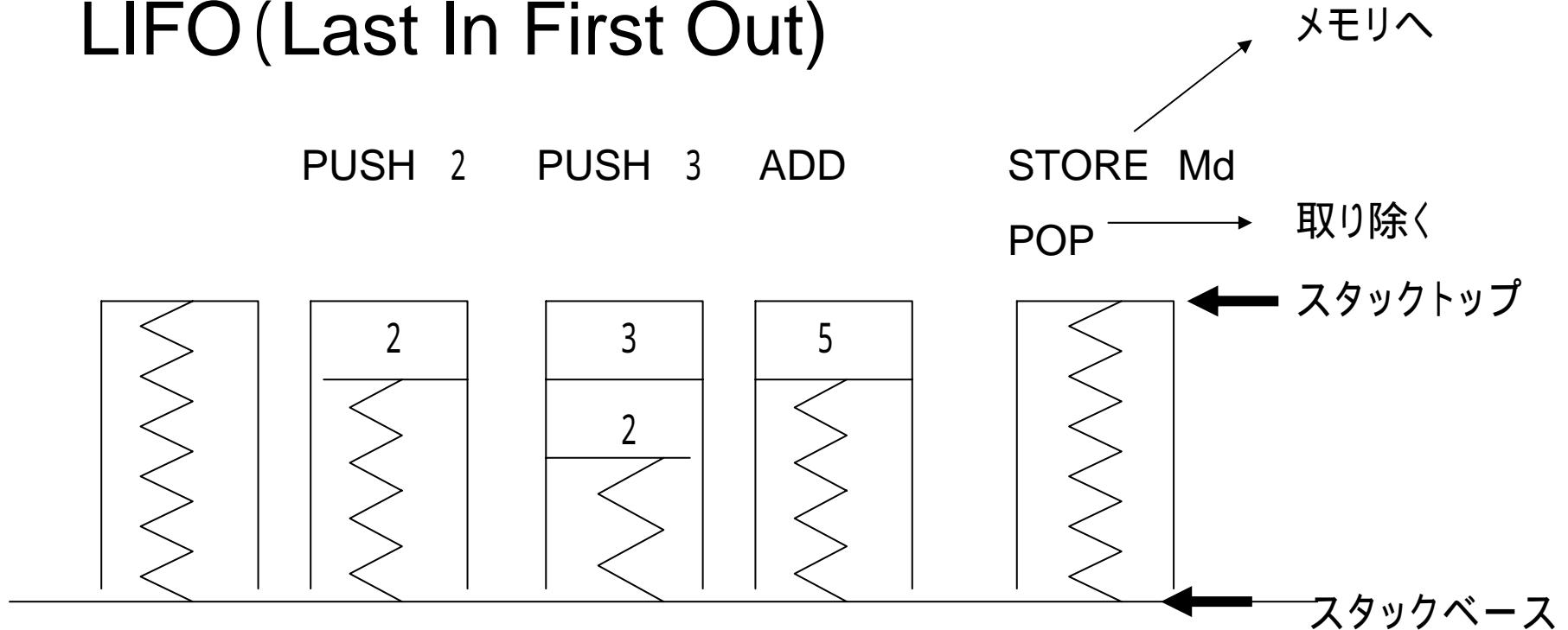

0アドレス命令形式

スタックコンピュータ

PUSH Ms(20)

STORE Md(20)

OP (8):**オペランド指定なし**

POP (8)

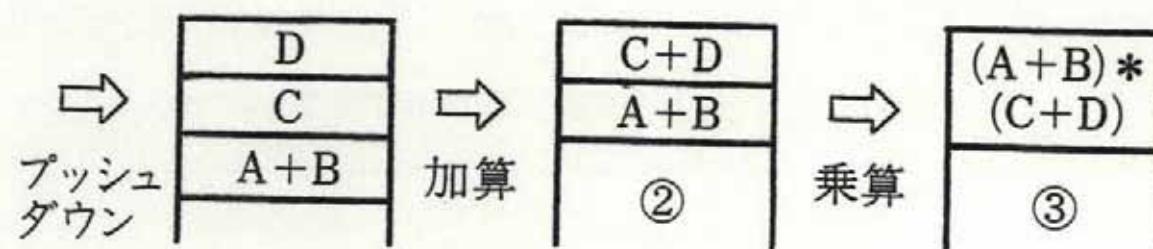

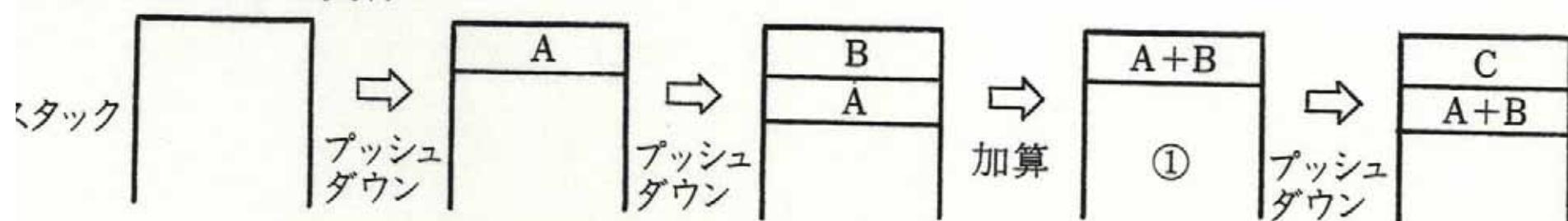

# スタックの構造

LIFO (Last In First Out)

反対語

FIFO (First In First Out): キュー

- ・ インフィックス記法:  $2 + 3$

- ・ プレフィックス記法:  $+ 2 3$

(ポーランド記法)

- ・ ポストフィックス記法:  $2 3 +$

(逆ポーランド記法)

## スタックによる計算

ポストフィックス記法の数式を左から1回走査

変数(数)であればスタックにPUSH

演算であればスタックトップとその下の数に

演算を施し、結果をプッシュ

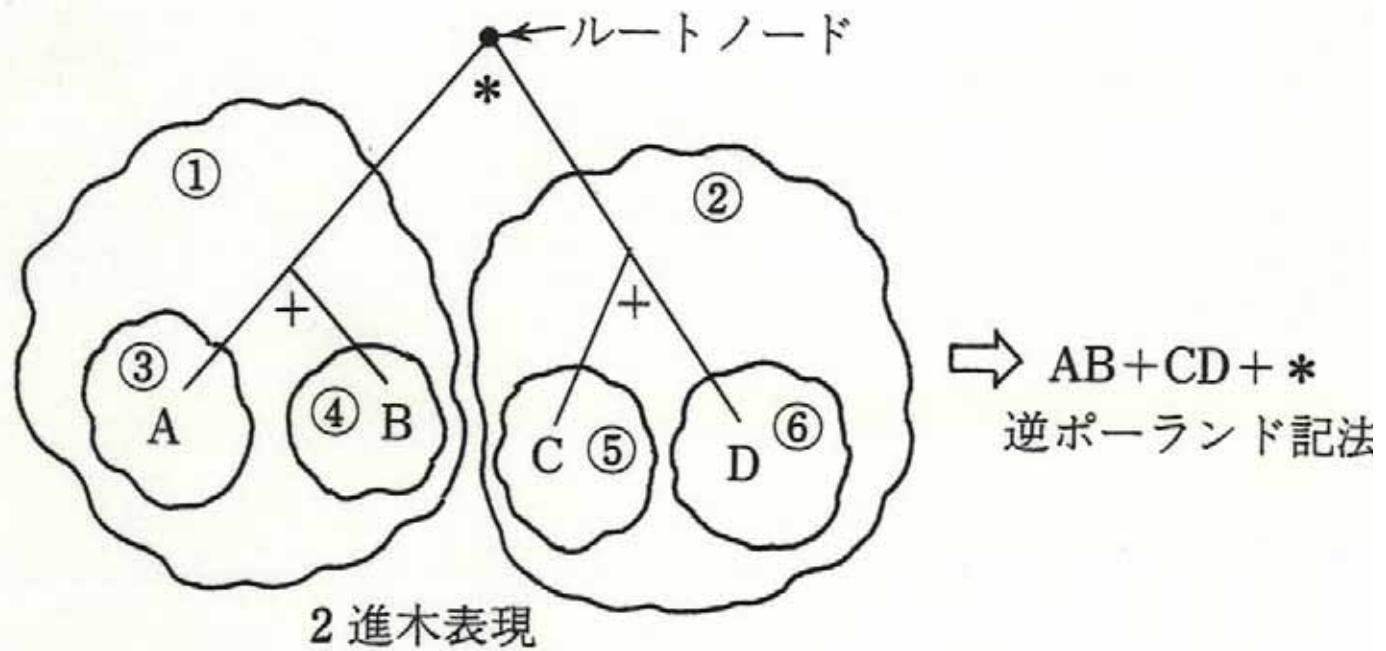

# 逆ポーランド記法への変換

インフィックス記法      op

逆ポーランド記法      op

部分式

部分式

部分式に再帰的に適用

例

2 + 3    2 3 +      ( 2 + 3 ) \* ( 4 + 5 )      ( 2 + 3 )( 4 + 5 ) \*

( 2 + 3 ) \* ( 4 + 5 )      2 3 + 4 5 + \*

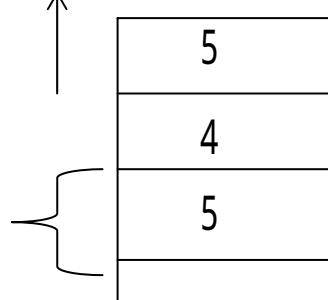

# 2 3 + の計算

2 3 +

2 3 +

2 3 +

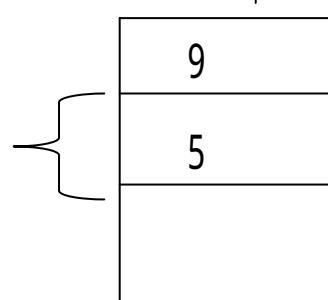

# (2+3)\*(4+5)の計算

2 3 + 4 5 + \*

PUSH

2 3 + 4 5 + \*

PUSH

2 3 + 4 5 + \*

加算

2 3 + の結果をボトムにおいてその上で 4 5 + の加算.

それらを掛け算

$(A+B)*(C+D)$  →

通常の算術式の記法

AB+CD+\* の実行

(a) 逆ポーランド記法への変換

(b) AB+CD+\* の実行

# 1.4 各種機械命令の評価

命令実行数 (IC)

データアクセス回数

必要メモリ量

プログラム実行時間

$$T = IC * CPI * MC$$

演算時間 1、メモリ 2 サイクル

逐次 vs 並列

|     |       |      |       |        |

|-----|-------|------|-------|--------|

|     |       |      | LOAD  | R1, A  |

|     | ADD   | B, A | ADD   | R1, B  |

| (a) | ADD   | C, D | LOAD  | R2, C  |

|     | MUL   | B, C | ADD   | R2, D  |

|     | STORE | E, B | MUL   | R2, R1 |

|     |       |      | STORE | E, R2  |

|     |       |   |       |        |

|-----|-------|---|-------|--------|

|     | LOAD  | A | LOAD  | R1, A  |

|     | ADD   | B | LOAD  | R2, B  |

|     | STORE | T | ADD   | R1, R2 |

| (c) | LOAD  | C | LOAD  | R3, C  |

|     | ADD   | D | LOAD  | R4, D  |

|     | MUL   | T | ADD   | R3, R4 |

|     | STORE | E | MUL   | R1, R3 |

|     |       |   | STORE | E, R1  |

|     |       |   |                         |  |

|-----|-------|---|-------------------------|--|

|     | PUSH  | A |                         |  |

|     | PUSH  | B |                         |  |

|     | ADD   |   | $E = (A + B) * (C + D)$ |  |

| (e) | PUSH  | C |                         |  |

|     | PUSH  | D |                         |  |

|     | ADD   |   |                         |  |

|     | MUL   |   |                         |  |

|     | STORE | E |                         |  |

|                 | (a) | (b) | (c) | (d) | (e) |

|-----------------|-----|-----|-----|-----|-----|

| 命令フェッチ回数(実行命令数) | 4   | 6   | 7   | 8   | 8   |

| 主記憶データアクセス回数    | 11  | 5   | 7   | 5   | 5   |

| 必要メモリ量(ビット)     | 128 | 136 | 140 | 168 | 124 |

| <b>処理時間</b>     | 25  | 13  | 17  | 13  | 13  |

図 1.5 各種機械命令形式の評価 ( $E = (A+B) * (C+D)$  の場合)

(a) 2アドレス命令形式, (b) 1アドレス命令形式 (レジスタ-メモリ方式), (c) 1アドレス命令形式 (アキュムレータ方式), (d) 1アドレス命令形式 (ロードストア方式), (e) 0アドレス命令形式

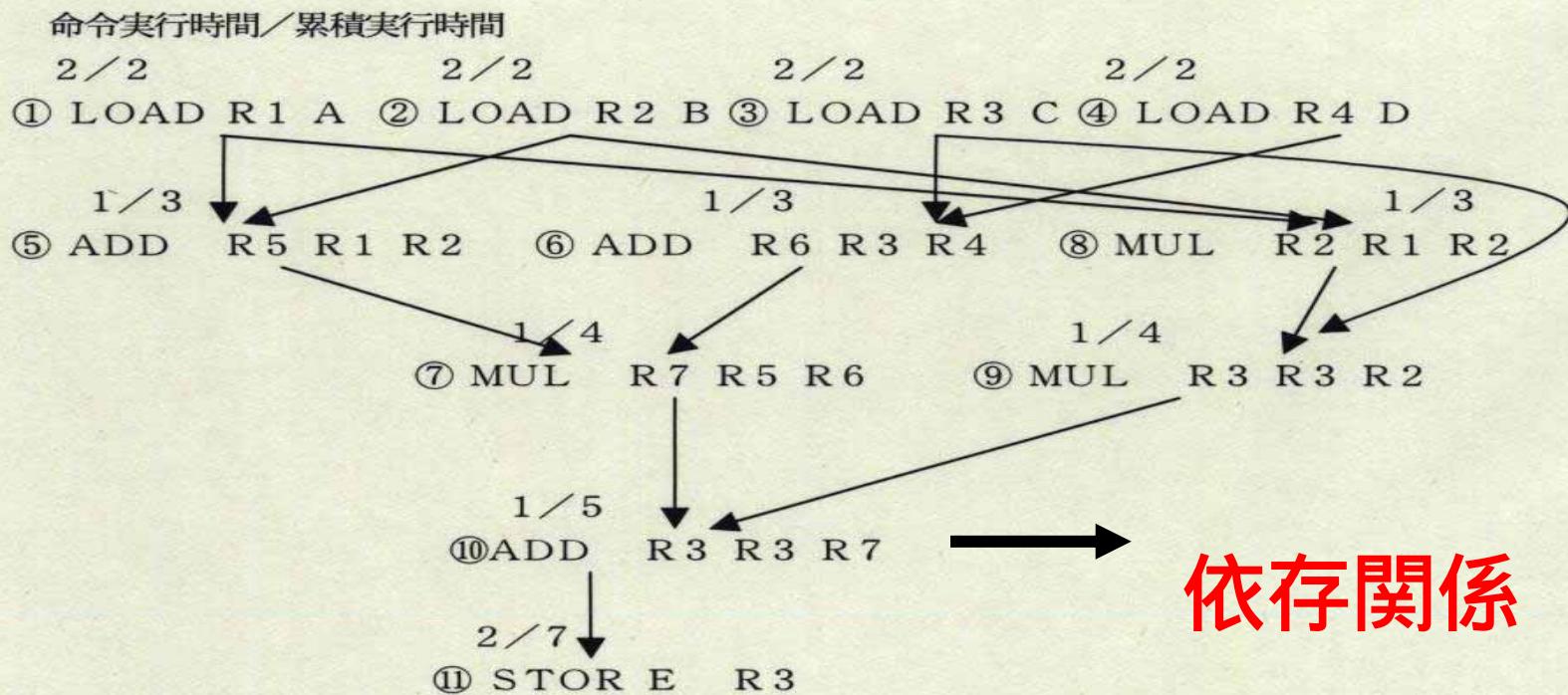

$E = (A + B) * (C + D) + A * B * C$  の実行

A ロードストアアーキテクチャ 演算は3オペランド

| プログラム |    |    |    | 時間 |

|-------|----|----|----|----|

| LOAD  | R1 | A  |    | 2  |

| LOAD  | R2 | B  |    | 2  |

| LOAD  | R3 | C  |    | 2  |

| LOAD  | R4 | D  |    | 2  |

| ADD   | R5 | R1 | R2 | 1  |

| ADD   | R6 | R3 | R4 | 1  |

| MUL   | R7 | R5 | R6 | 1  |

| MUL   | R2 | R1 | R2 | 1  |

| MUL   | R3 | R3 | R2 | 1  |

| ADD   | R3 | R3 | R7 | 1  |

| STORE | E  | R3 |    | 2  |

| 計     |    |    |    | 16 |

## B ロードストア 2オペランド

|       |    |    |   |

|-------|----|----|---|

| LOAD  | R1 | A  | 2 |

| LOAD  | R2 | B  | 2 |

| LOAD  | R3 | C  | 2 |

| LOAD  | R4 | D  | 2 |

| MOVE  | R5 | R1 | 1 |

| ADD   | R5 | R2 | 1 |

| ADD   | R4 | R3 | 1 |

| MUL   | R4 | R5 | 1 |

| MUL   | R1 | R2 | 1 |

| MUL   | R1 | R3 | 1 |

| ADD   | R1 | R4 | 1 |

| STORE | E  | R1 | 2 |

| 計 17  |    |    |   |

|       |    |    |   |

|-------|----|----|---|

| LOAD  | R1 | A  | 2 |

| LOAD  | R2 | B  | 2 |

| LOAD  | R3 | C  | 2 |

| LOAD  | R4 | D  | 2 |

| ADD   | R1 | R2 | 1 |

| ADD   | R4 | R3 | 1 |

| MUL   | R1 | R4 | 1 |

| MUL   | R2 | R3 | 1 |

| LOAD  | R3 | A  | 2 |

| MUL   | R2 | R3 | 1 |

| ADD   | R1 | R2 | 1 |

| STORE | E  | R1 | 2 |

| 計 18  |    |    |   |

$$E = (A + B) * (C + D) + A * B * C$$

C 2アドレス命令形式 1リード / 1ライトの場合

ADD D, C 7

MUL C, B 7

MUL C, A 7

ADD B, A 7

MUL B, D 7

ADD B, C 7

STORE, B 4

計 46

## D スタックアーキテクチャ

| プログラム   | 時間 |

|---------|----|

| PUSH A  | 2  |

| PUSH B  | 2  |

| ADD     | 1  |

| PUSH C  | 2  |

| PUSH D  | 2  |

| ADD     | 1  |

| MUL     | 1  |

| PUSH A  | 2  |

| PUSH B  | 2  |

| MUL     | 1  |

| PUSH C  | 2  |

| MUL     | 1  |

| ADD     | 1  |

| STORE E | 2  |

| 計       | 22 |

## E レジスタ - メモリ

|       |    |    |   |

|-------|----|----|---|

| LOAD  | R1 | A  | 2 |

| ADD   | R1 | B  | 3 |

| LOAD  | R2 | C  | 2 |

| ADD   | R2 | D  | 3 |

| MUL   | R1 | R2 | 1 |

| LOAD  | R3 | A  | 2 |

| MUL   | R3 | B  | 3 |

| MUL   | R3 | C  | 3 |

| ADD   | R1 | R3 | 1 |

| STORE | E  | R1 | 2 |

計 2 2

|       |    |    |   |

|-------|----|----|---|

| LOAD  | R1 | A  | 2 |

| MOVE  | R2 | R1 | 1 |

| ADD   | R2 | B  | 3 |

| LOAD  | R3 | C  | 2 |

| MOVE  | R4 | R3 | 1 |

| ADD   | R4 | D  | 3 |

| MUL   | R2 | R4 | 1 |

| MUL   | R1 | B  | 3 |

| MUL   | R1 | R3 | 1 |

| STORE | E  | R1 | 2 |

計 1 9

メモリ装置L/S 2台、演算装置ALU 2台の時（リストスケジューリング）

| 時間 | L/S | L/S | ALU | ALU |

|----|-----|-----|-----|-----|

| 9  |     |     |     |     |

| 8  |     | ⑪   |     |     |

| 7  |     |     | ⑩   |     |

| 6  |     |     | ⑨   | ⑦   |

| 5  |     |     | ⑧   | ⑤   |

| 4  |     |     |     | ⑥   |

| 3  | ①   | ②   |     |     |

| 2  | —   | —   |     |     |

| 1  | ③   | ④   |     |     |

並列処理を入

れる

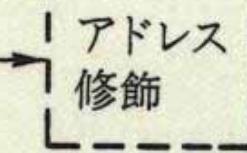

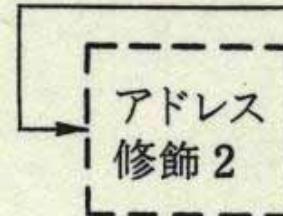

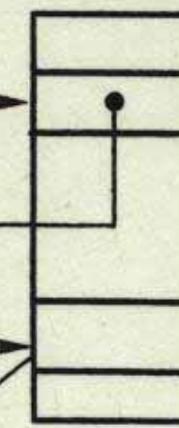

## 1 . 3 . 2 アドレッシングモード

( 1 ) 即値 , 直接 , 間接

( 2 ) 絶対 , 相対

アドレス指定ビット数

参照の局所性 : 基準アドレスから変位

プログラムでのアドレス変更

機械命令

即値

演算装置などへ

主記憶装置

直接

演算装置などへ

間接

主記憶装置

演算装置などへ

(a) 主記憶アクセス回数による分類

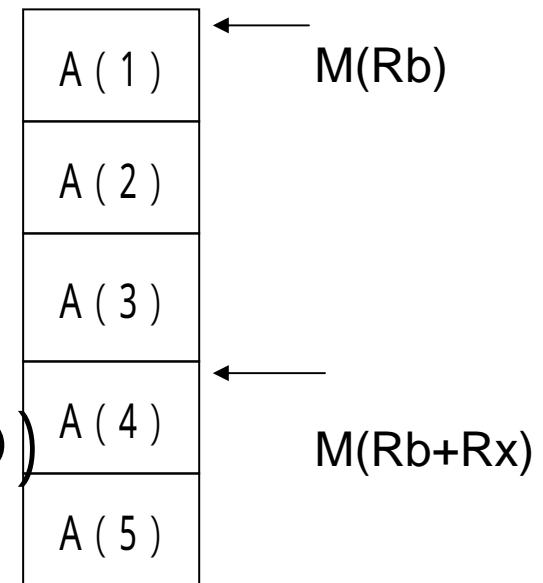

### (3) アドレッシングモード レジスタ $R_i$

即値 #I

利用頻度大

レジスタ間接  $M(R_i)$

リターンアドレス

ディスプレースメント  $M(R_i + D)$

絶対  $M(D)$

インデックス  $M(R_i + R_j + D)$

ベクトルや配列へのアクセス  $R_x$ : インデックスレジスタ

+ 4ずつ増やす

D:0にセット

$A(i)$ : 4バイトデータ

Rb: ベースレジスタ

$R_x$ : インデックスレジスタ

# 反復プログラム

S=0.0

DO 10 I=1,128

10 S=S + A(I)

LOADW Rs #FW0.0

LOADW Rx #IW0

L ADDFW Rs M(Rb+Rx+10)

ADDIW Rx #IW4

BRCMPLT Rx #IW512 M(L)

STORE M(Rb+0) Rs

分岐命令

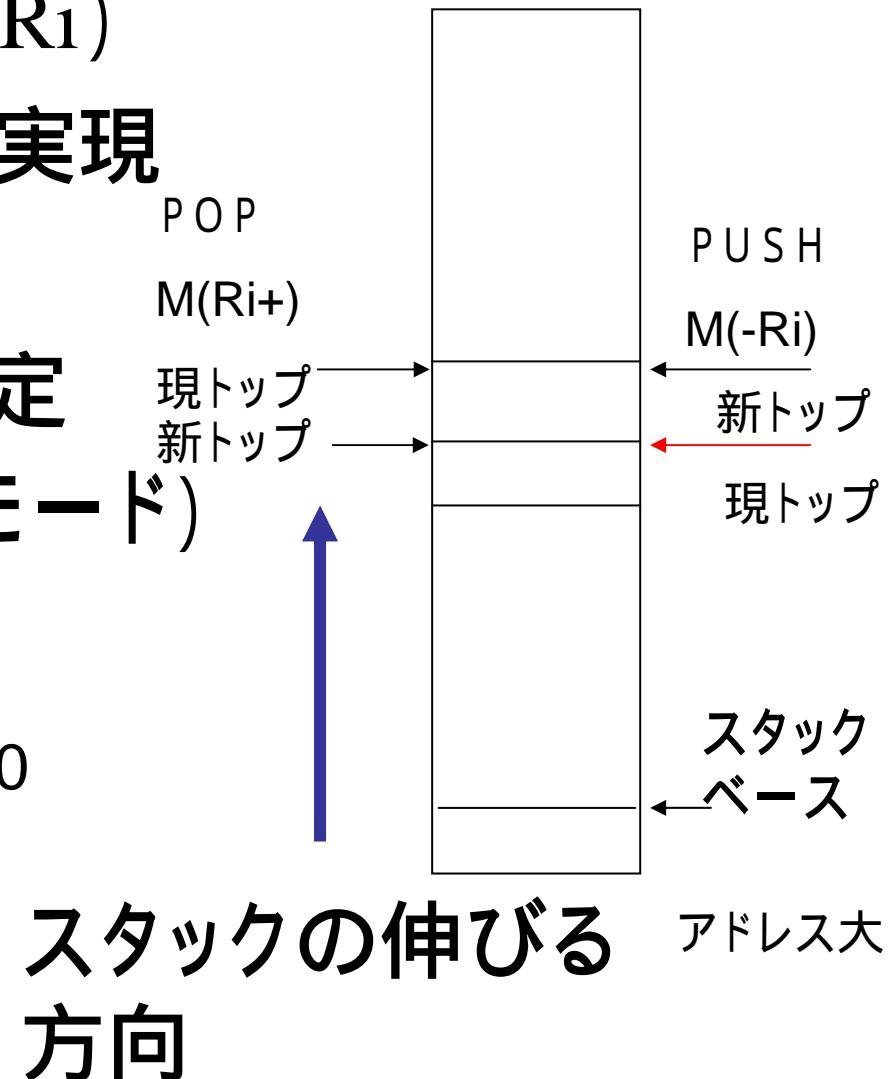

自動インクリメント  $M(R_i + )$

アドレス小

自動デクリメント  $M(-R_i)$

## メモリ上でのスタック実現

自己相対  $M(PC+D)$

## 分岐先アドレスの決定

メモリ間接  $M$ (ベースモード)

## ポインタ変数

PUSH: STORE  $M(-R_1)$   $R_0$

POP: LOAD  $R_0 M(R_1 + )$

$R_1$ : スタックトップレジスタ

# 1.5 データ表現

## (1) 固定小数点(整数)

小数点位置はプログラム実行中固定：

そろばんと同じ

負の数の表現

2の補数と1の補数

## (2) 浮動小数点数

単精度(32ビット), 倍精度(64ビット)

小数点位置を示す情報を個々のデータに保持

## (3) 10進数

パックとアンパック形式

可変長演算

## (4) 文字

|    |  |  |     |  |

|----|--|--|-----|--|

| 符号 |  |  | ... |  |

|----|--|--|-----|--|

小数点：純小数 小数点：整数

(a) 固定小数点数の表現

|   |   |   |   |       |

|---|---|---|---|-------|

| 1 | 1 | 0 | 1 | 絶対値表現 |

|---|---|---|---|-------|

|   |   |   |   |         |

|---|---|---|---|---------|

| 1 | 0 | 1 | 1 | 2 の補数表現 |

|---|---|---|---|---------|

|   |   |   |   |         |

|---|---|---|---|---------|

| 1 | 0 | 1 | 0 | 1 の補数表現 |

|---|---|---|---|---------|

(b) 負数 ( $-5$  の場合) の表現

|    |     |   |  |     |    |  |

|----|-----|---|--|-----|----|--|

| 符号 | 指 数 |   |  | 仮 数 |    |  |

| 0  | 1   | 8 |  |     | 31 |  |

符号：仮数の符号

仮数：16進6桁

指数：エクセス64符号

(c) 浮動小数点数の表現 (IBM 単精度)

|      |    |    |    |     |       |    |

|------|----|----|----|-----|-------|----|

| 数字   | 数字 | 数字 | 数字 | ... | 数字    | 符号 |

| 1バイト |    |    |    |     | パック形式 |    |

|      |    |     |    |     |              |    |

|------|----|-----|----|-----|--------------|----|

| ゾーン  | 数字 | ゾーン | 数字 | ... | 符号           | 数字 |

| 1バイト |    |     |    |     | ゾーン(アンパック)形式 |    |

(d) 10進数の表現 (IBM)

図 1.6 各種の数表現

# 10,9の補数

10の補数

$$\begin{array}{r}

536 \\

-378 \\

\hline

158

\end{array}

\quad

\begin{array}{r}

536 \\

1000 \\

-378 \\

\hline

-1000

\end{array}

\quad

\begin{array}{r}

536 \\

622 \\

-1000 \\

\hline

158

\end{array}$$

622

符号桁

数値桁

0536

$$\begin{array}{r}

+9622 \\

\hline

10158

\end{array}$$

無視

$$\begin{array}{r}

536 \\

999 \\

-378 \\

-1000 \\

+1 \\

\hline

\end{array}

\quad

\begin{array}{r}

9\text{の補数} 621 \\

\hline

\end{array}$$

$$\begin{array}{r}

536 \\

+621 \\

\hline

1157 \\

-1000 \\

+1 \\

\hline

158

\end{array}

\quad

\begin{array}{r}

0536 \\

+9621 \\

\hline

10157 \\

+1 \\

\hline

\end{array}$$

# 2, 1の補数

## 2の補数

$L$ 桁の正整数 $X$ の2の補数 $\bar{X}$

$$X + \bar{X} = 2^L$$

$$\begin{array}{r} 101 + 011 \\ \hline \text{各桁反転} + 1 \\ 1000 \end{array}$$

|                                           |                                                                                              |

|-------------------------------------------|----------------------------------------------------------------------------------------------|

| $+X:0X$<br>$-X:1\bar{X}$                  | <span style="margin-right: 20px;">符号桁</span><br><span style="margin-right: 20px;">数値桁</span> |

| $\underline{+1011(-5)}$<br><br>$1101(-3)$ |                                                                                              |

## 1の補数

$L$ 桁の正整数 $X$ の1の補数 $\bar{\bar{X}}$

$$X + \bar{\bar{X}} = 2^L - 1$$

$$\begin{array}{r} 101 + 010 \\ \hline \text{各桁反転} \\ 111 \end{array}$$

|                                                                                                                                     |                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| $+X:0X$<br>$-X:1\bar{\bar{X}}$                                                                                                      | <span style="margin-right: 20px;">符号桁</span><br><span style="margin-right: 20px;">数値桁</span> |

| $\underline{+0101(+5)}$<br><br><span style="border: 1px solid black; border-radius: 50%; padding: 2px;">1</span><br>$10010$<br>$+1$ |                                                                                              |

循環桁上げ

# 浮動小数点数

$10^{-100} \sim 10^{100}$

2進固定小数点:  $2 * 100 \log_2 10: 600$  ビット?

IBM单精度32ビット  $m r^e$

符号1ビット, 指数 $e$ : 7ビット(-64から+63),

仮数 $m$ : 24ビット純小数(16進6桁),

基數 $r$ : 16

正規化: 仮数第1桁非零 1 ~ F

$16^{-65} \sim (1-16^{-6}) 16^{63}$

IBM倍精度64ビット

仮数: 16進14桁(56ビット)

### 3.7.3 浮動小数点数の標準化

IBM 形式の浮動小数点数の形式

IEEE (アメリカの電気電子学会 .

アイトリプルイーと読む )) 標準

(1) 単精度浮動小数点

符号(s) 1 ビット ,

| 符号<br>s | 指数 8<br>e | 仮数 23<br>f |

|---------|-----------|------------|

|---------|-----------|------------|

指数(e) 8 ビット ( げたばき 1 2 7 )

仮数(f) 23 ビット

基數 2

e=255 で f = 0 なら数の値は NaN ( 非数 )

e=255 で f=0 なら数の値は  $(-1)^s$

0 < e < 255 なら数の値は

$(-1)^s 2^{e-127} (1.f)$

正規化数

e=0, f = 0 なら数の値は

$(-1)^s 2^{-126} (0.f)$

非正規化数

e=f=0 なら数の値は  $(-1)^s 0$

## (2) 倍精度浮動小数点

符号( s ) 1 ビット ,

指数( e ) 11 ビット( げたばき 1023 ),

仮数( f ) 52 ビット

## (3) IEEE 標準の特徴

簡約表現

基数が 2

仮数の第 1 衔は暗黙的に 1

非正規化数

正規化表現  $2^{-126}$  : 最小数

非正規化( denormalize ) 表現可

数値としての

の数値

1 / 0 は を値

非数の導入

$\sqrt{-1}$  ,  $0/0$  , - : NaN ( Not a Number )

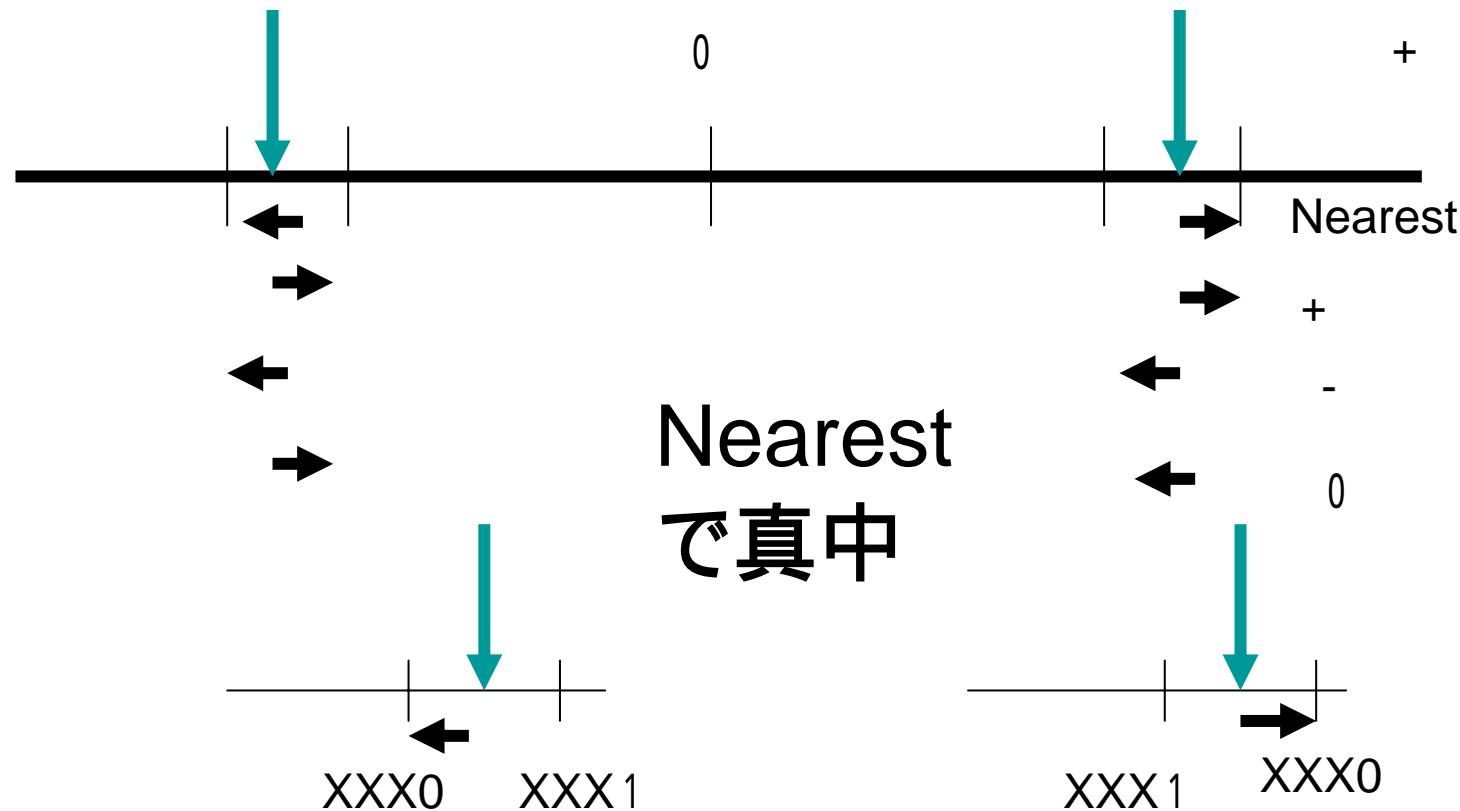

丸めの方式の指定

4 つの丸めの方式

- 最も近い数への丸め

- + 方向への丸め

- - 方向への丸め

- 0 方向への丸め

# 丸め方式

- $X_0 = X, X_1 = (X_0 - Y) + Y, X_2 = (X_1 - Y) + Y$

- $X_n = (X_{n-1} - Y) + Y$

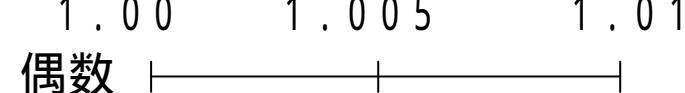

- 四捨五入

- $X=1, Y= - 0.555, X_0 - Y = 1.555 \quad 1.56,$

- $X_1 = 1.56 - 0.555 = 1.005 \quad 1.01$

- $X_1 - Y = 1.01 + 0.555 = 1.565 \quad 1.57,$

- $X_2 = 1.57 - 0.555 = 1.015 \quad 1.02$

- 偶数に丸め

- $X_0 - Y = 1.555 \quad 1.56, \quad \begin{array}{c} 1.55 \\ 1.555 \\ \hline 1.00 \end{array} \quad \begin{array}{c} \text{偶数} \\ 1.56 \end{array}$

- $X_1 = 1.56 - 0.555 = 1.005 \quad 1.01$

内部割込み

## 例外：マスク可能

- ・オーバフロー：正規化数より大  $2^{128}$

- ・アンダフロー：非正規化数発生

## 演算

- ・演算異常：NaN の発生時

- ・ゼロデバイド

- ・精度異常（inexact）： $1/3$  など

# 1 . 6 機械命令セットの機能

## ( 1 ) 算術演算命令

演算種類 : ADD,SUB,MUL,DIV

データタイプ : I,F,D

データ長 : B,HW,W,DW , EW

命令形式 : R-R、R-Memory

加算命令だけでも10個以上

## (2)論理演算・ビット演算命令

プール演算: AND(論理積), OR(論理和), NOT(否定)

| AND     | OR      | NOT |

|---------|---------|-----|

| 0 · 0 0 | 0 + 0 0 | 0 1 |

| 0 · 1 0 | 0 + 1 1 | 1 0 |

| 1 · 0 0 | 1 + 0 1 |     |

| 1 · 1 1 | 1 + 1 1 |     |

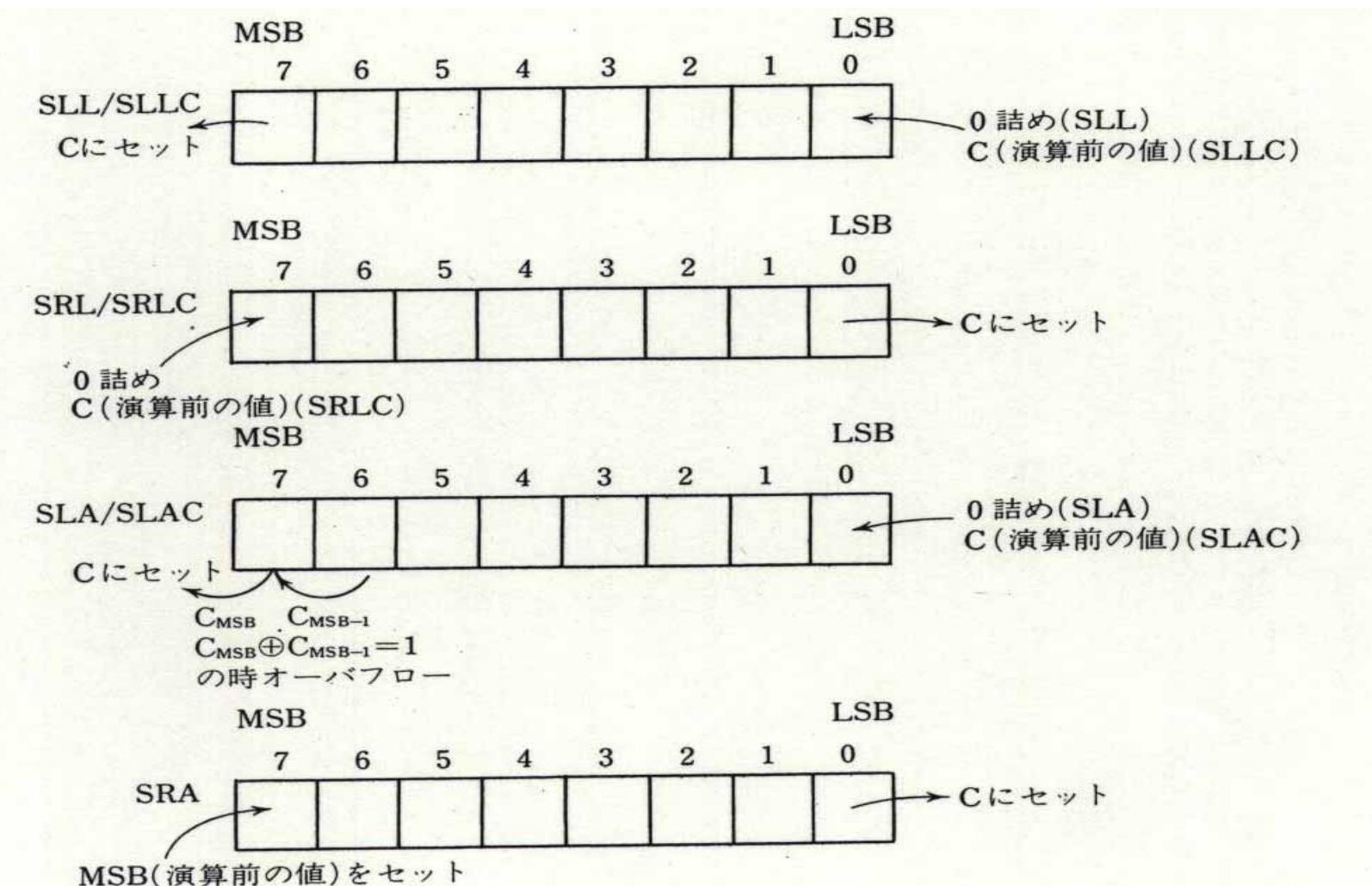

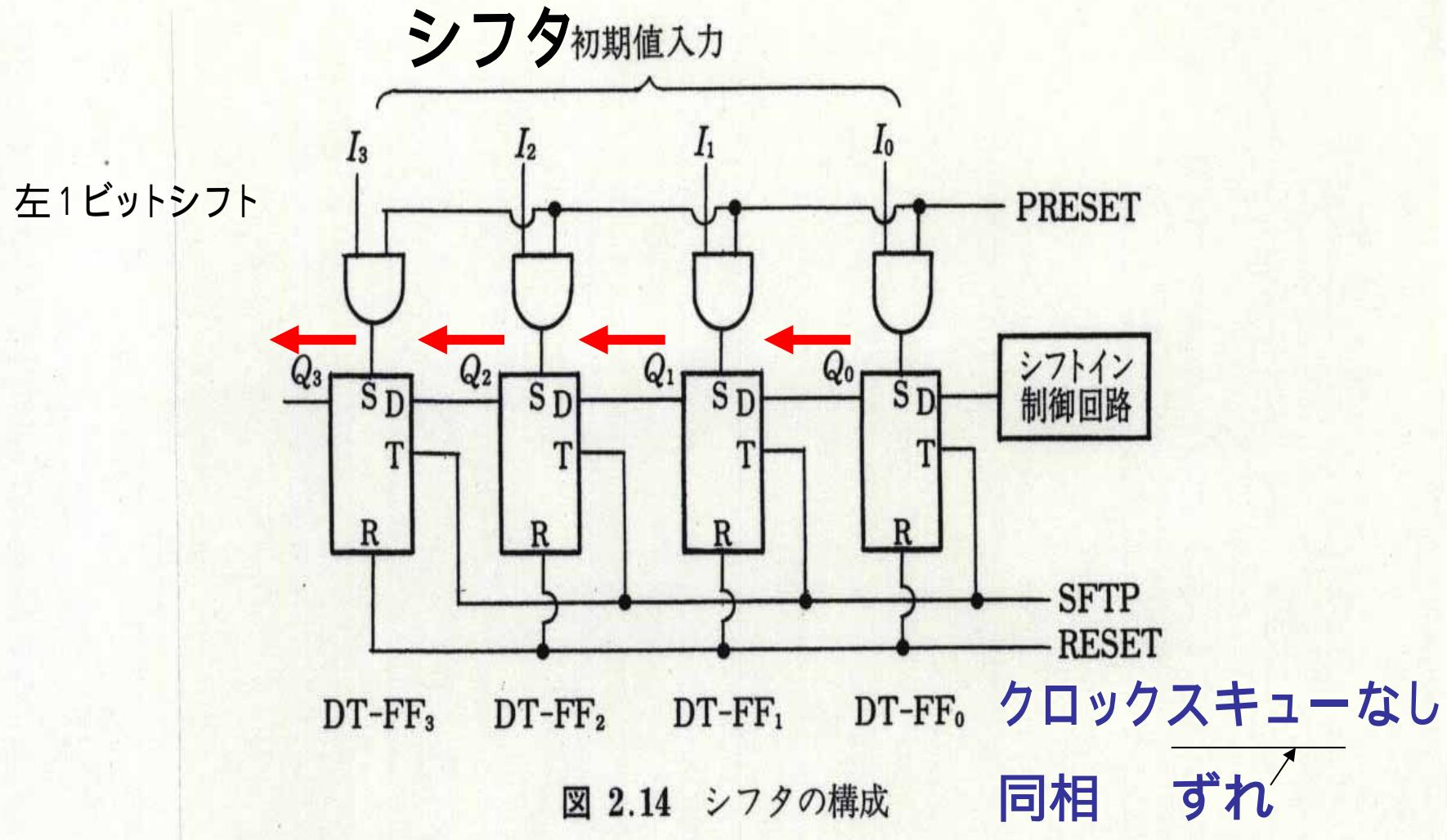

# シフト演算: 論理シフト, 算術シフト

図 2.25 シフト演算

**比較演算**: E(Equal), LT(Less Than),

GT(Greater Than)

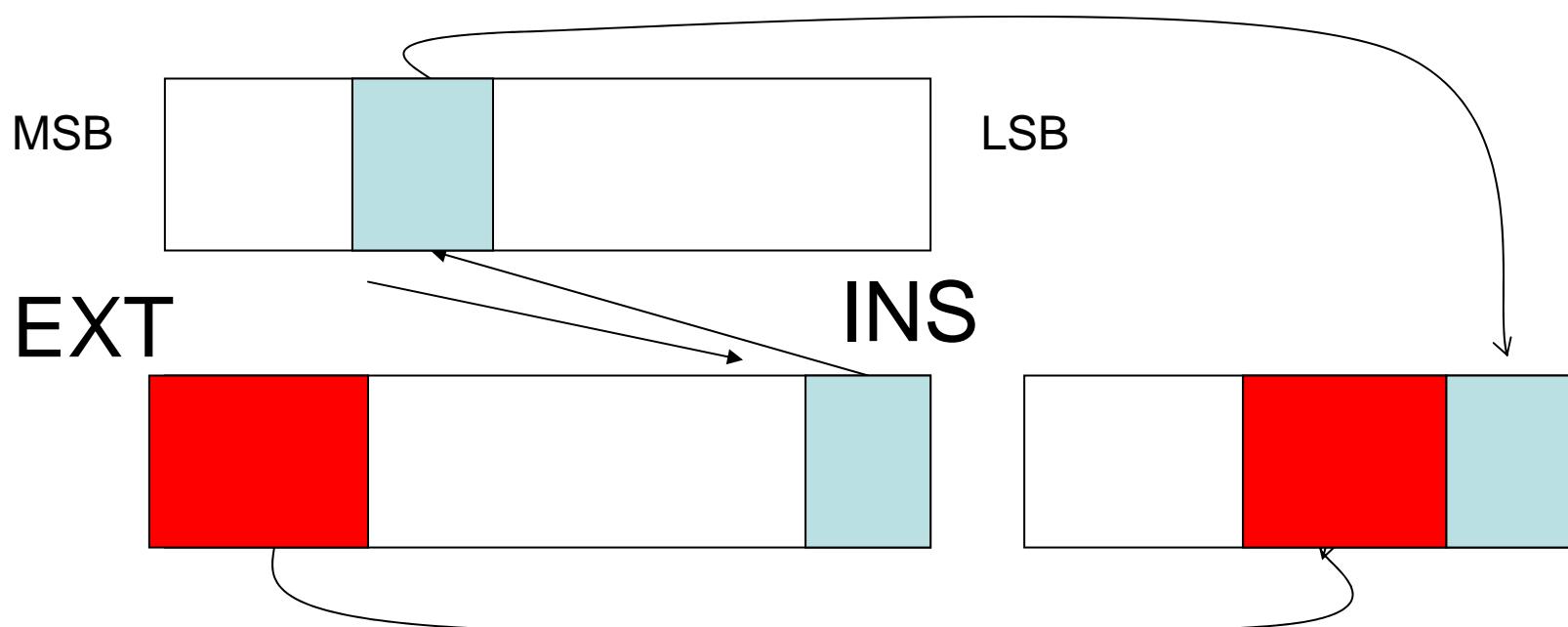

**ビット演算**: EXT(抽出), INS(挿入),

CONS(連接)

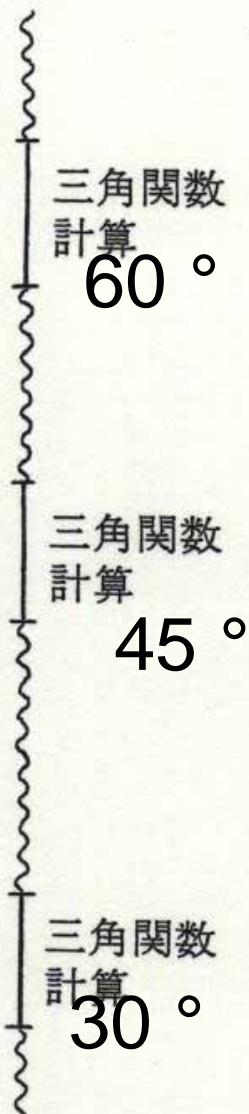

## ( 3 ) 分岐命令

無条件分岐

単純な無条件分岐: UCN

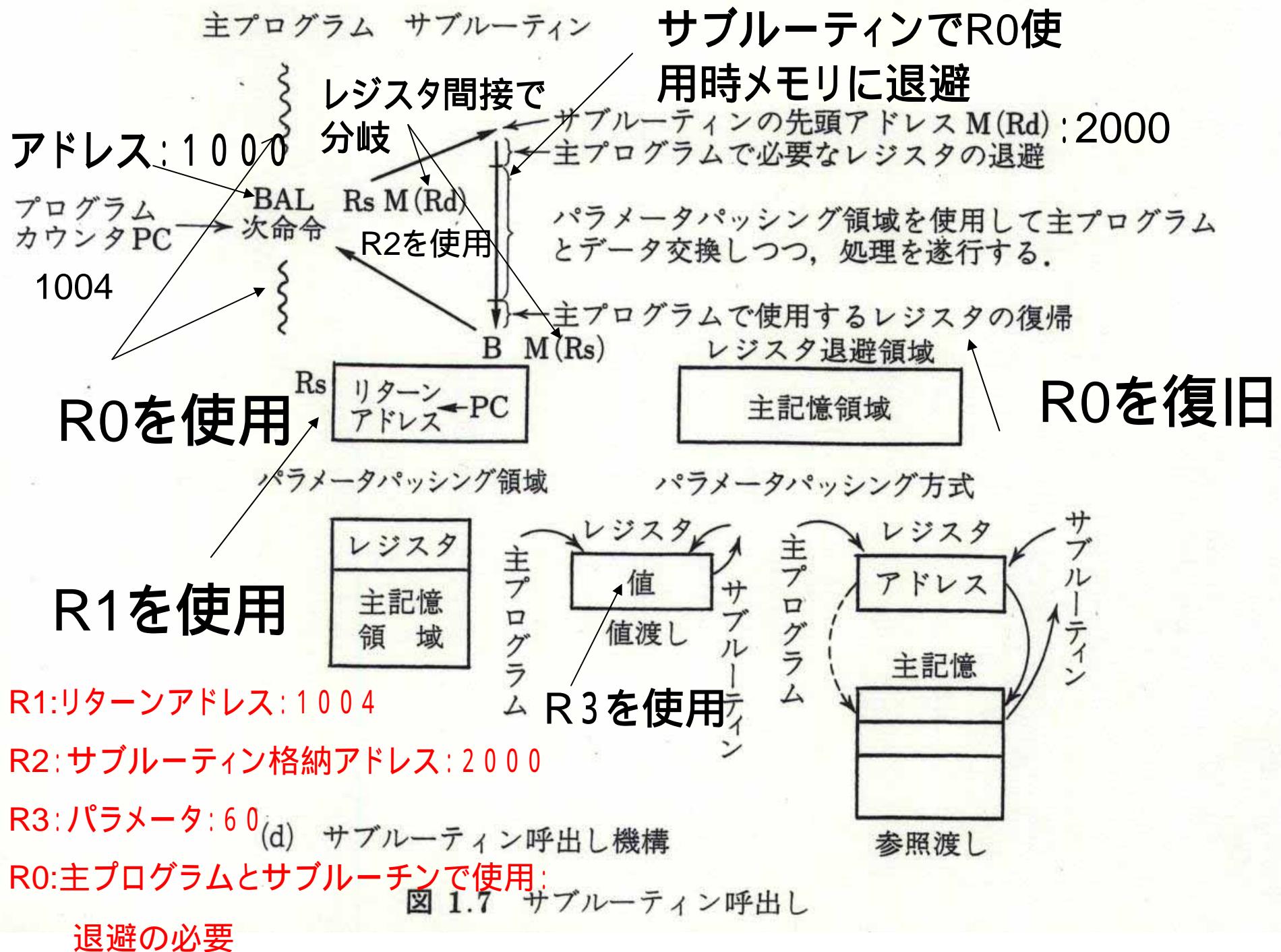

手続き呼び出し: BAL

Branch and Link

パラメータパッシング

レジスタ待避と復旧

多重レベル呼出し

再帰的プログラム

プログラム

(a) サブルーティン

を用いない方式

主プログラム 三角関数

サブルーティン

主プログラム

サブルーティン

(b) サブルーティンを

用いる方式

(c) サブルーティンのネスト

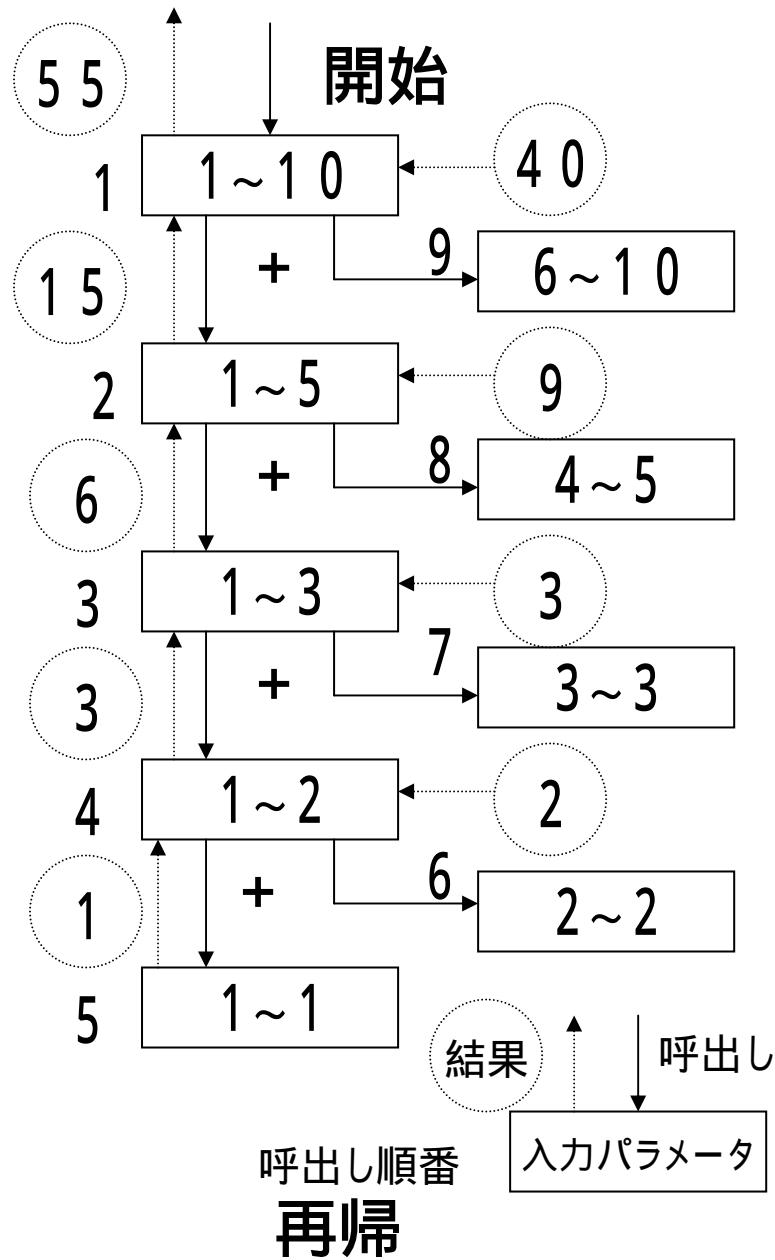

# 再帰プログラム

A(I)の総和計算

Proc S(M,N)

If M=N Then A(M)

Else S(M,N) = S(M,(M+N)/2)

+ S((M+N)/2 + 1 , N)

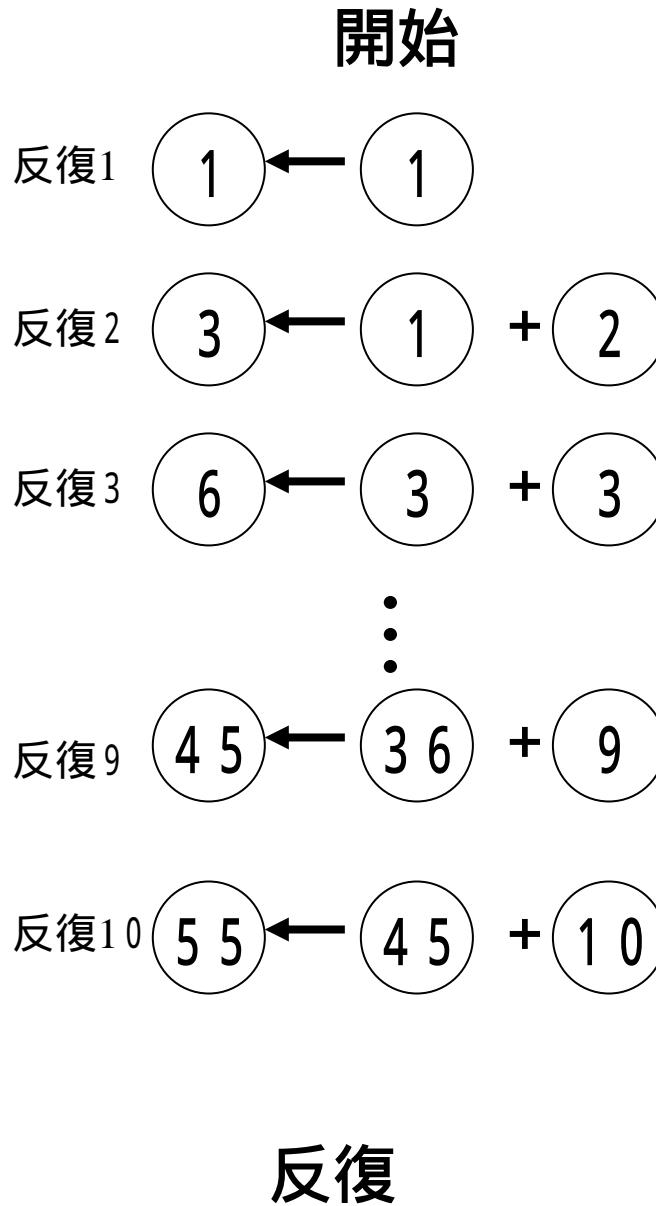

# 反復プログラム

S=0.0

DO 10 I=1,128

10 S=S + A(I)

```

/*100万個のデータの整数加算を1000回繰り返す.反復10秒,再帰210

秒*/

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

int SUM(int i,int j);

void main(void)

{int i,j,k;

int s;

time_t start, finish;

double elapsed_time;

time( &start );

for(k=1;k<=10000;k++)

{

s=SUM(1,100000);

}

time( &finish );

printf("再帰総和=%d\n",s);

elapsed_time = difftime( finish, start );

printf( "\n再帰プログラムの実行に %f 秒かかりました。 \n",

elapsed_time );

```

```

time( &start );

for(k=1;k<=10000;k++)

{s=0;

for(i=1;i<=100000;i++)

s=s+i;

}

time( &finish );

printf("反復総和=%d\n",s);

elapsed_time = difftime( finish, start );

printf( "\n反復プログラムの実行に %f 秒かかりました。 \n", elapsed_time );}

int SUM(int i,int j)

{if(i==j) return (i);

else return (SUM(i,(i+j)/2)+SUM((i+j)/2+1,j));

}

```

図1.10(a) 反復と再帰による1~10の総和計算

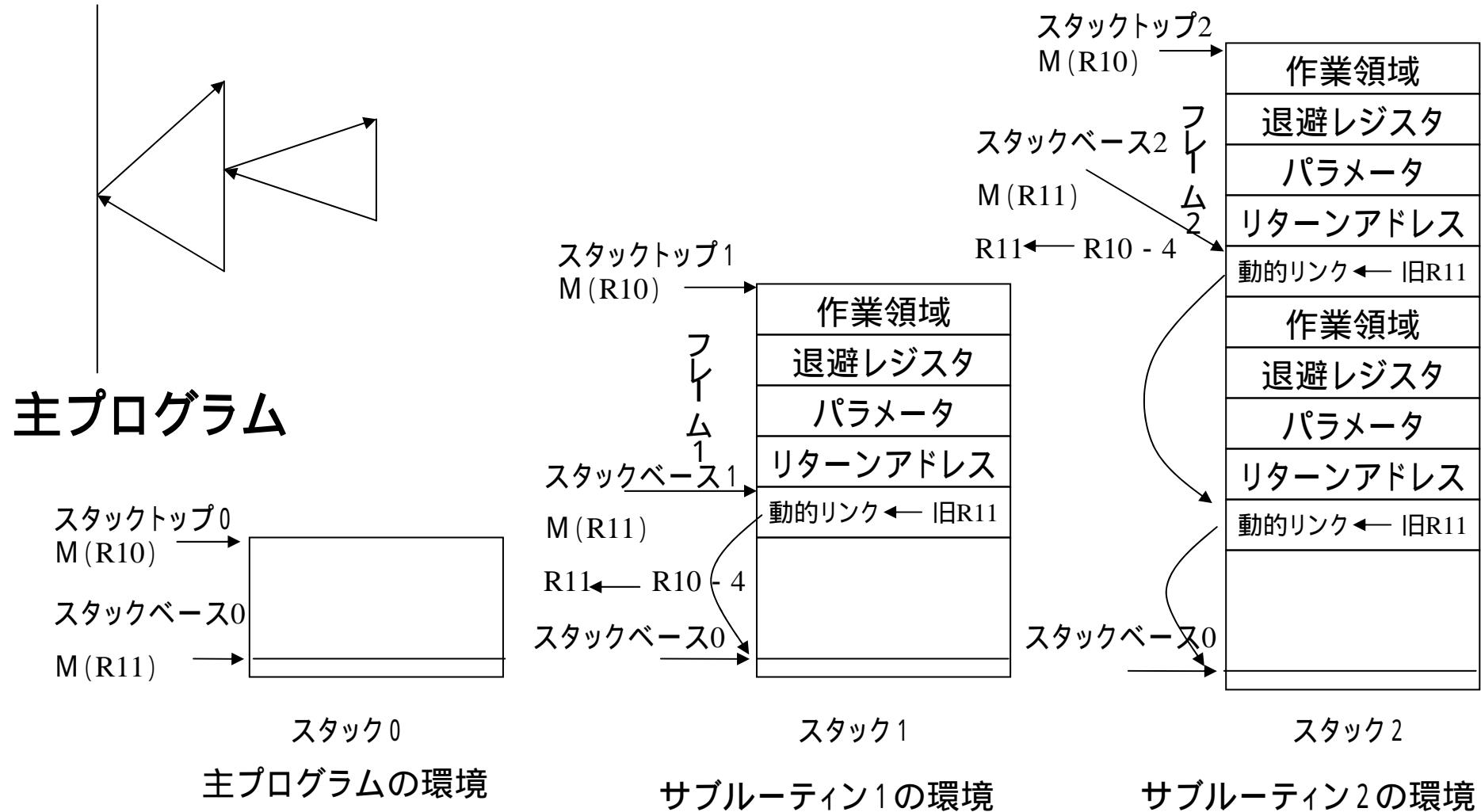

# 制御スタックによる管理

図1.10(b) サブルーティン呼出しの制御

## 条件分岐

比較 & 分岐: BRCMP Compare and Branch

BRCMPE R0 R1 A: R0=R1ならAへ分岐

条件コード: BRC Branch on Condition

条件: Z:ゼロ, V:オーバフロー

N:負, C:キャリー

SUB R2 R0 R1 R0=R1ならZ=1となる

BR CZ A: Z=1ならAへ分岐

条件レジスタ: BRCR Branch on Condition Reg

汎用レジスタ内容 0, 1

CMPE R2 R0 R1: R0=R1ならR2=1

BR CR R2 A: R2=1ならAへ分岐

ADD R3 R2 R1

挿入されるとどうなるか?

( 4 ) データ転送命令

ロードストア

ムーブ:MOVE

I / O

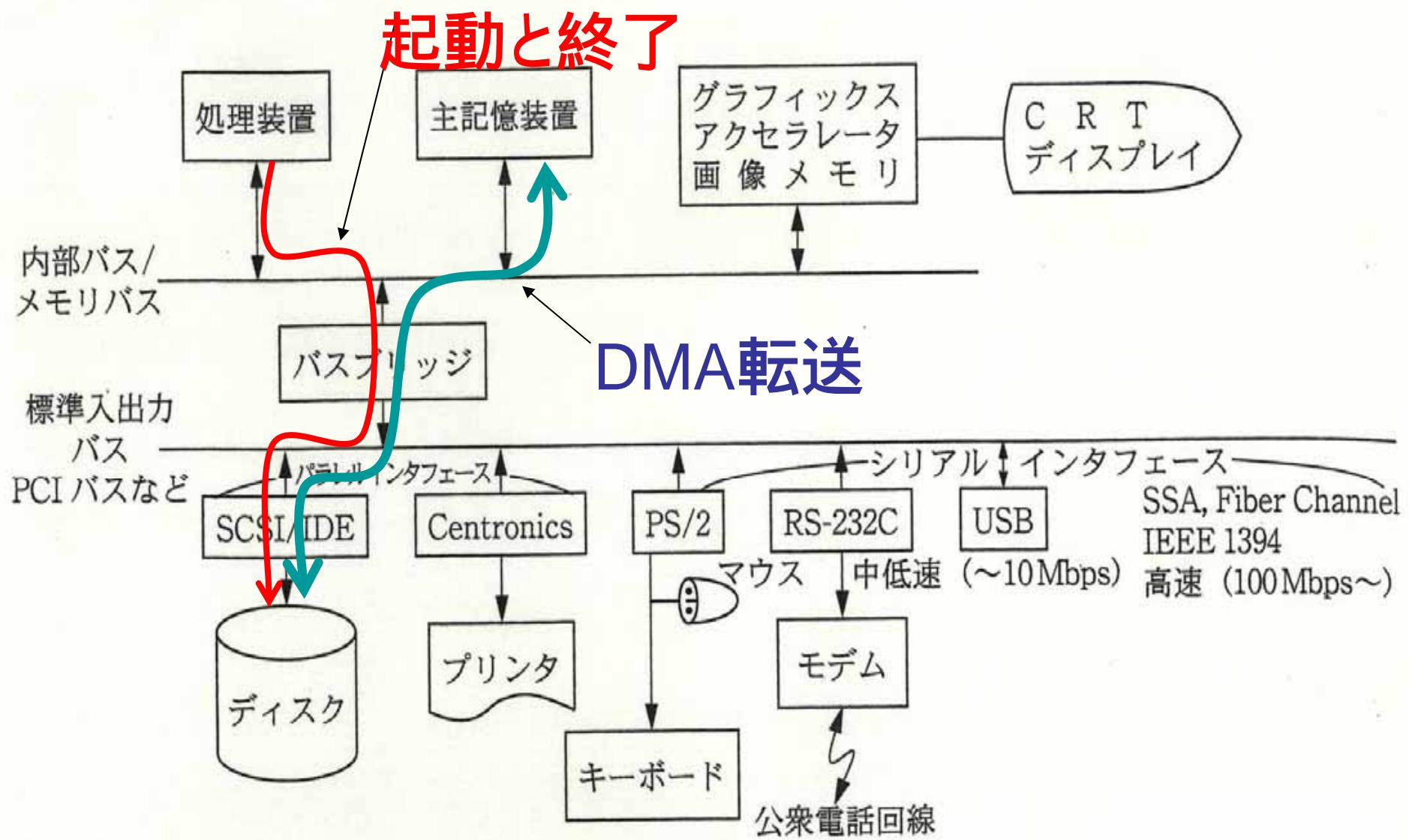

# 1.7 入出力制御装置と入出力装置

標準入出力バス

インターフェース

パラレル

SCSI:ディスク

Centronics:プリンタ

シリアル

低速:10Mbps

RS-232C, USB

高速:100Mbps

Fiber Channel

IEEE1394

図 1.8 パーソナルコンピュータの入出力制御と装置

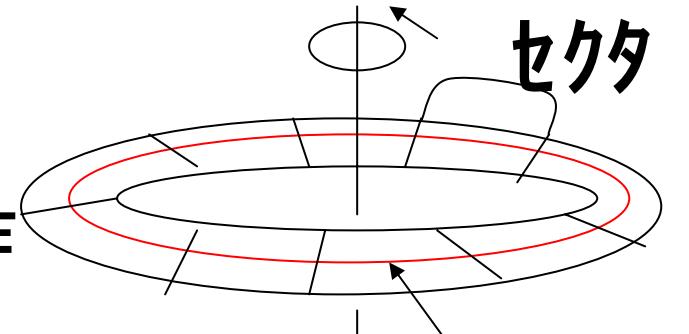

# ハードディスクの制御

メモリマップD/I/O

メモリへのR/Wデータ操作

起動処理

トラック番号:

アドレスXXXX0

セクタ番号:

アドレスXXXX1

転送バイト数:

アドレスXXXX2

転送メモリアドレス:

アドレスXXXX4

ディスク状態:

アドレスXXXX8

故障状態

トラック

Write

Read

使用中

データアクセスOK

- ハードディスク

年率: 60%で容量増加

トラック数: 5,000~30,000

セクタ数: 100~500

セクタバイト数: 512B

シーク(seek)時間: 5~12msec

回転待ち(rotation latency)

3,600~15,000RPM(Rotations Per Minute)

3,600RPMで $1/(2 * 60) = 8\text{msec}$

7,200RPMで4msec

データ転送

プログラムモードバス VS DMA

データアクセスOKチェック データ転送

DMA プロセッサと独立に動作

終了処理

ポーリング

終わったかのチェック

割込み

終わりましたの報告

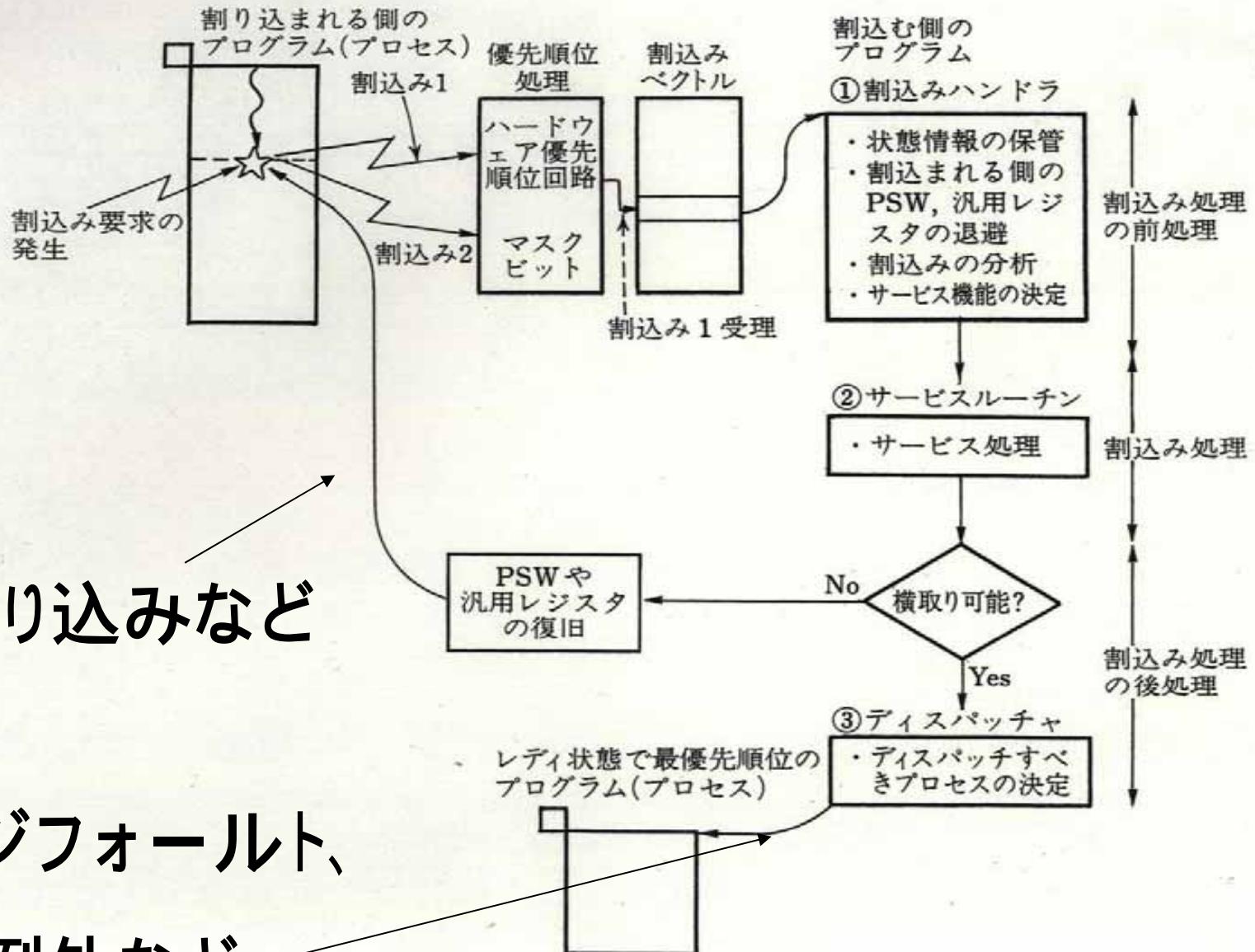

# 1.8 割込み

外部割込み：実行中のプログラムとは無関係な事象で生起

故障

入出力終了

内部割込み：実行中のプログラムに起因した事象で生起

演算で誤り

記憶領域外の参照

トレース

OS呼び出し(I/Oアクセス要求など)

ページフォールト

I/O割り込みなど

ページフォールト、

演算例外など

図 5.13 割込み処理の手続

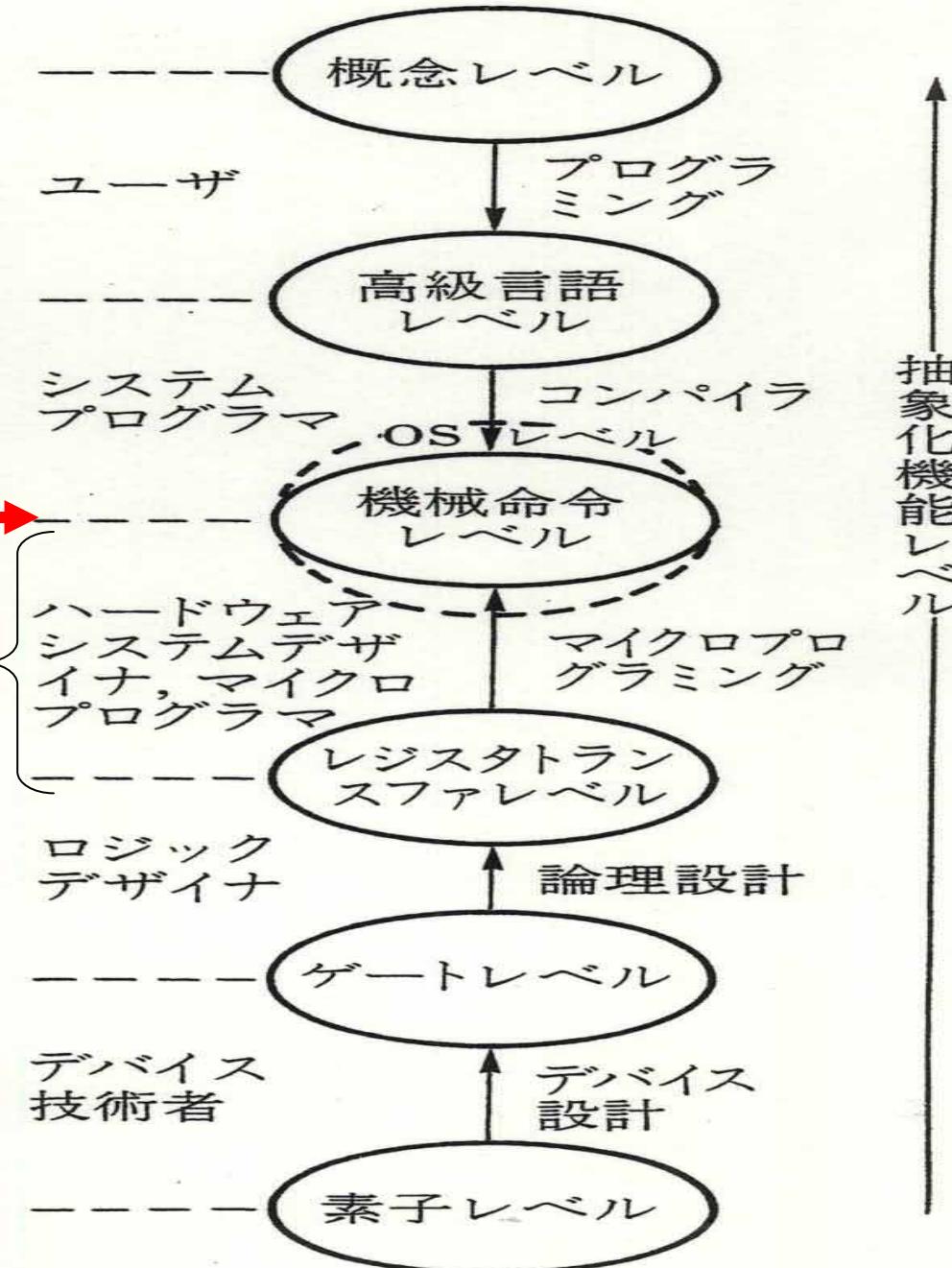

# 1.9 階層構造

(1) レベル

概念レベル

What to do: A(I)

高級言語レベル

How to do

反復プログラム

S=0.0

DO 10 I=1,128

10 S=S + A(I)

複雑、大規模システム

企業

社長

副社長、副社長

専務、専務、専務

部長、部長、...、部長

課長、課長、...、課長

コンピュータ

アーキテク

チャ

**狭義**

**広義**

図 1.10 コンピュータシステムの階層構造

# 機械命令レベル

コンピュータアーキテクチャ

Rb:1000

ハードとソフトのインターフェース

LOADW Rs #FW0.0

1010

A(1)

LOADW Rx #IW0

1014

A(2)

L ADDFW Rs M(Rb+Rx+10)

ADDIW Rx #IW4

BRCMPLT Rx #IW512 M(L)

STORE M(Rb+0) Rs

A(127)

A(128)

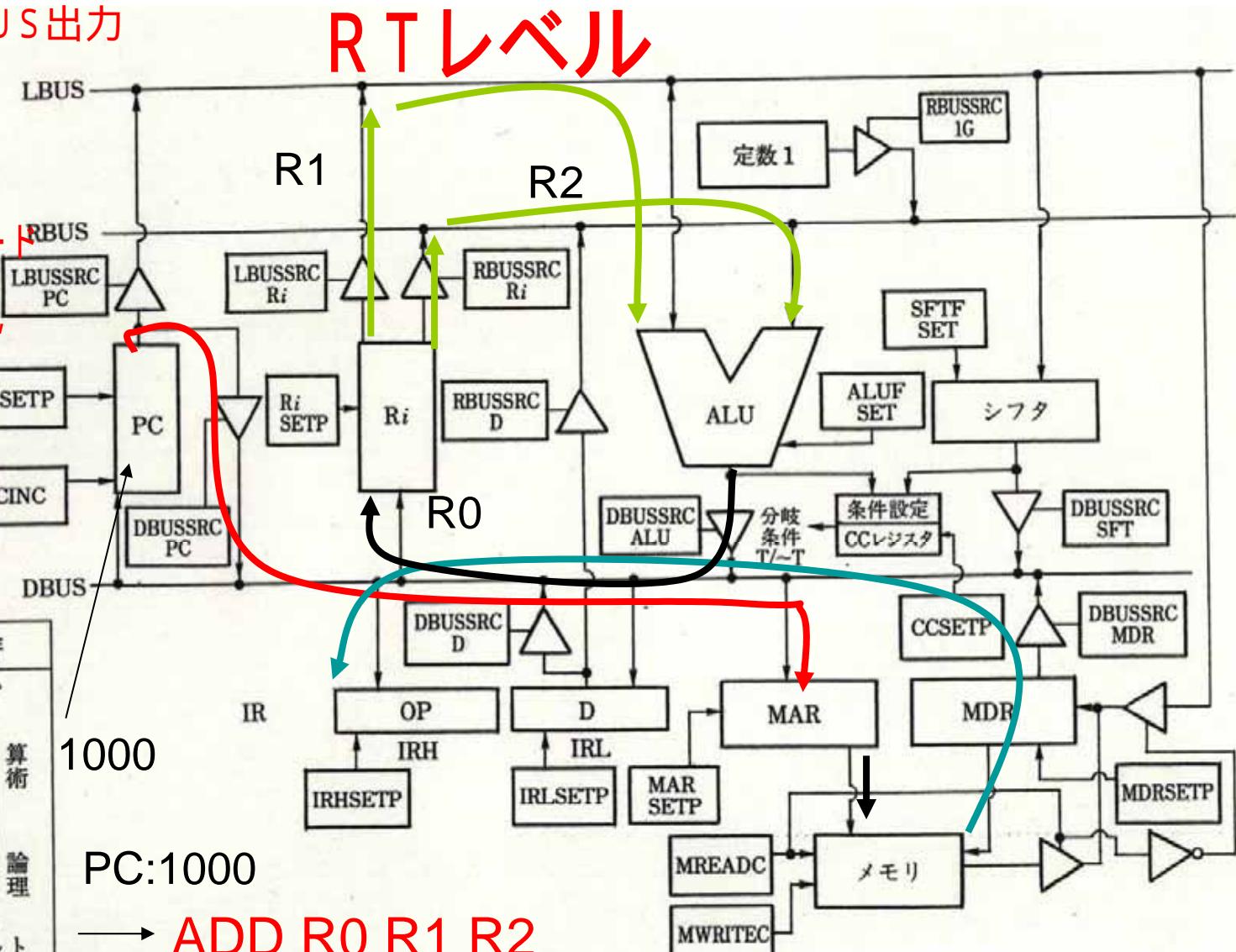

RTレベル

機能ブロックでの設計

ゲートレベル

AND, OR, NOTでの論理設計

素子レベル

トランジスタの設計

MOS, CMOS

1 PCリード, DBUS出力

2 MARセット,

メモリアクセス

3 IRセット, デコード

4 レジスタ読出し,

演算開始

5 結果格納

クロック

| ALUF           |                |                | 操作    |

|----------------|----------------|----------------|-------|

| S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> |       |

| 0              | 0              | 0              | クリア   |

| 0              | 0              | 1              | B-A   |

| 0              | 1              | 0              | A-B   |

| 0              | 1              | 1              | A+B   |

| 1              | 0              | 0              | A⊕B   |

| 1              | 0              | 1              | A+B   |

| 1              | 1              | 0              | A·B   |

| 1              | 1              | 1              | プリセット |

1002

算術論理演算装置

図 2.20 データバス

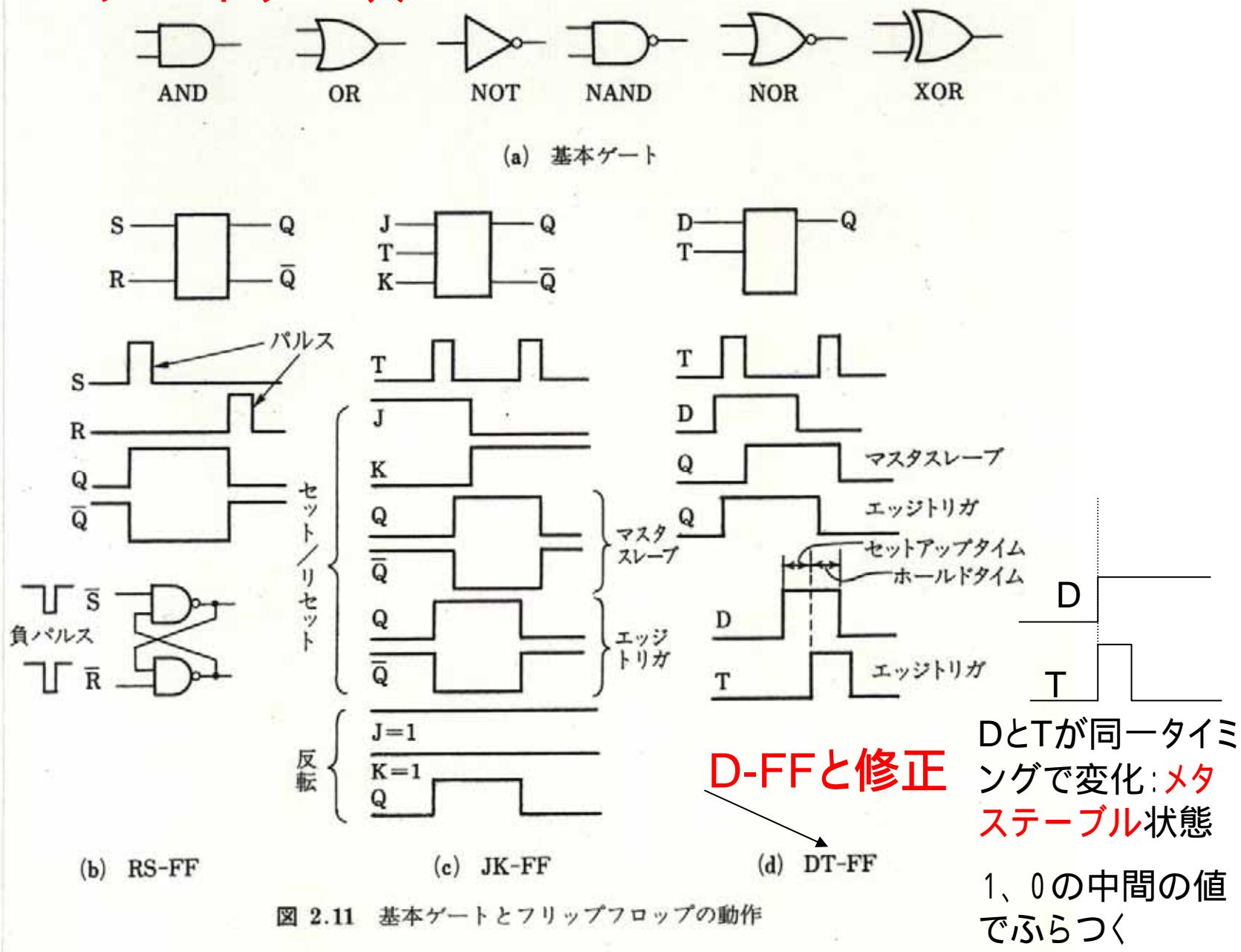

# ゲートレベル

# 組み合わせ回路の例

| 入力  |     |          | 出力  |           |

|-----|-----|----------|-----|-----------|

| $X$ | $Y$ | $C_{in}$ | $S$ | $C_{out}$ |

| 0   | 0   | 0        | 0   | 0         |

| 0   | 0   | 1        | 1   | 0         |

| 0   | 1   | 0        | 1   | 0         |

| 0   | 1   | 1        | 0   | 1         |

| 1   | 0   | 0        | 1   | 0         |

| 1   | 0   | 1        | 0   | 1         |

| 1   | 1   | 0        | 0   | 1         |

| 1   | 1   | 1        | 1   | 1         |

図 2.3 加算器設計のための真理値表

真理値表 積和標準形

簡単化

$$S = \bar{X} \cdot \bar{Y} \cdot C_{in} + \bar{X} \cdot Y \cdot \bar{C}_{in} + X \cdot \bar{Y} \cdot \bar{C}_{in} + X \cdot Y \cdot C_{in}$$

$$C_{out} = \bar{X} \cdot Y \cdot C_{in} + X \cdot \bar{Y} \cdot C_{in} + X \cdot Y \cdot \bar{C}_{in} + X \cdot Y \cdot C_{in}$$

$$\left\{ \begin{array}{l} S = X \oplus Y \oplus C_{in} \\ C_{out} = (X \oplus Y)C_{in} + XY \end{array} \right.$$

$\oplus$ : 排他的論理和

# 簡単な順序回路の例

取り込んだ入力値が出力に現れるまでの時間

ホールドタイム

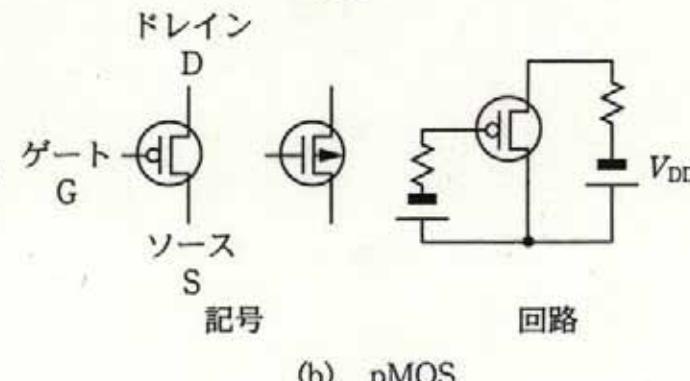

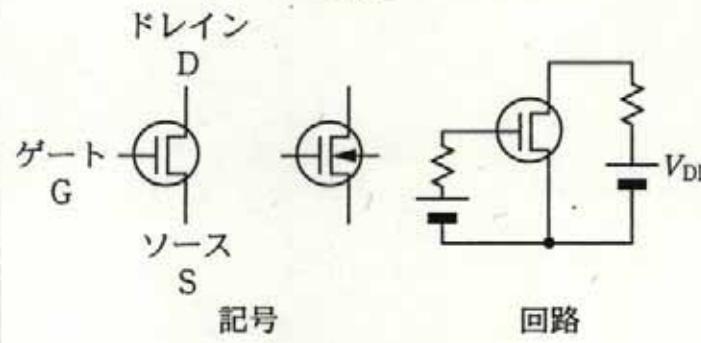

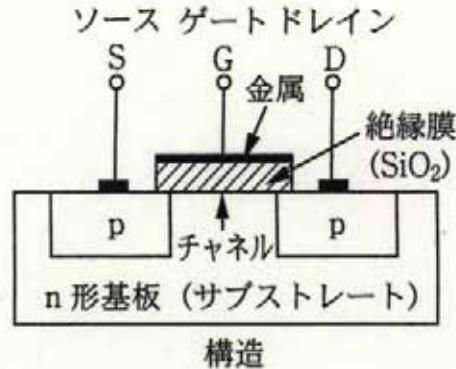

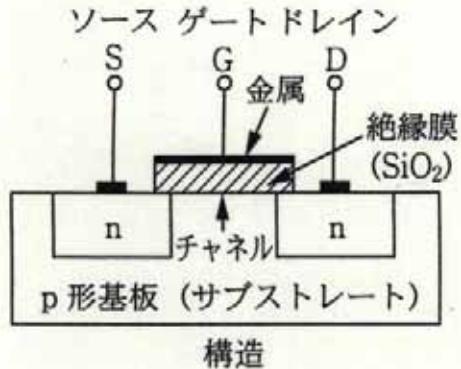

# 素子レベル

MOS

## 電界効果を利用(FET)

## 電子、正孔いずれか一方が関与

Metal Oxide Semiconductor

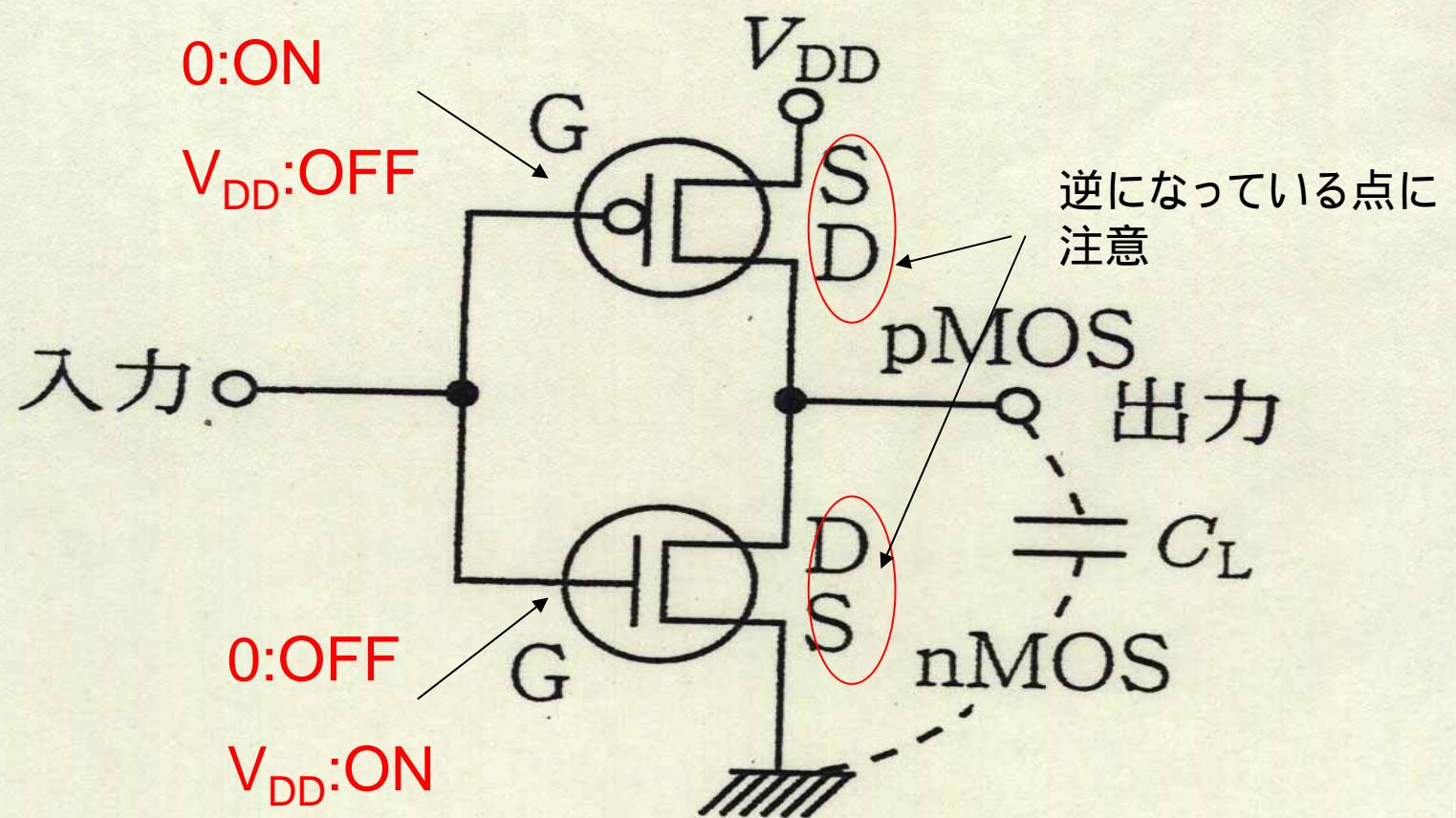

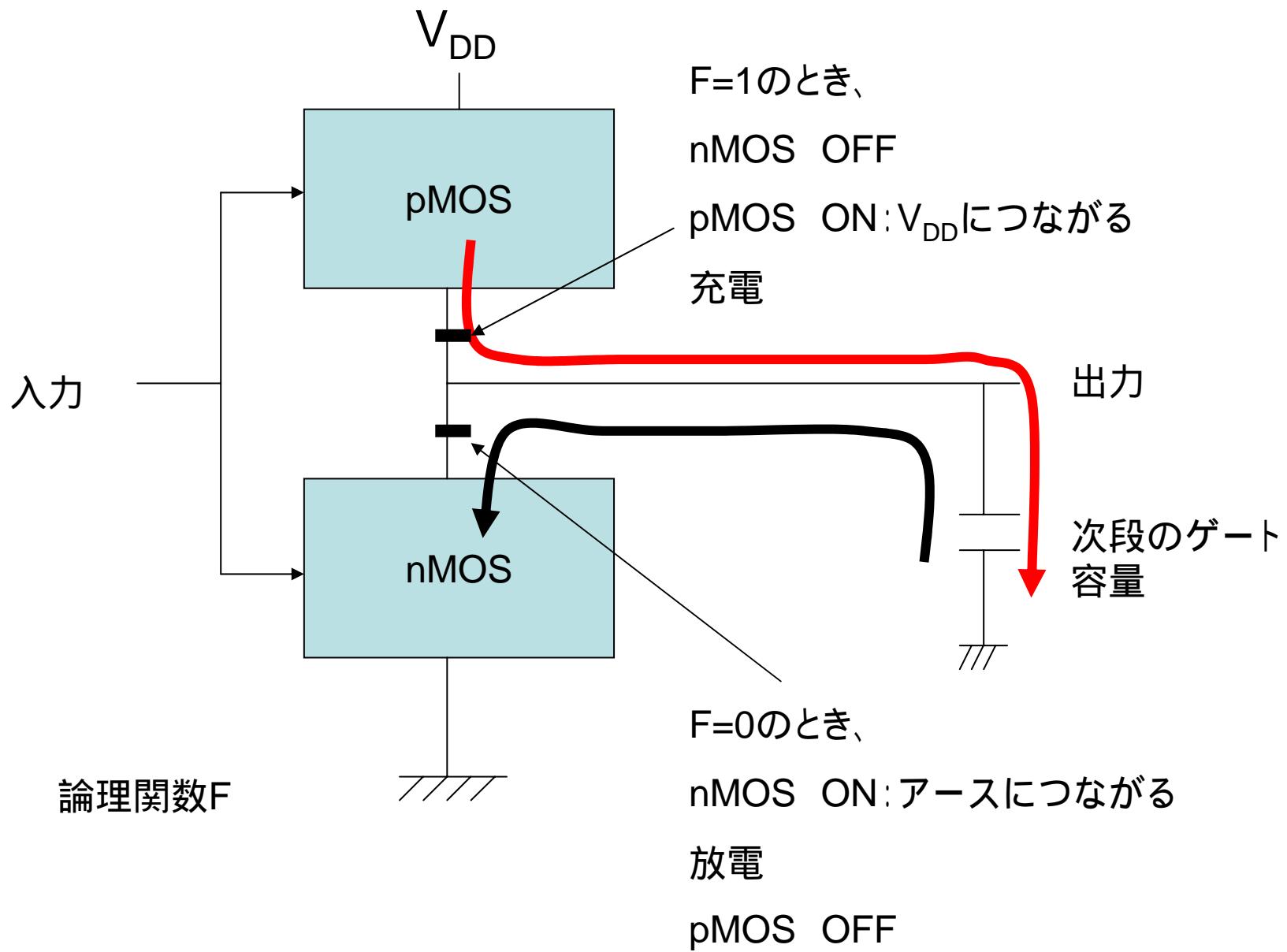

図 2.32 CMOS 否定回路

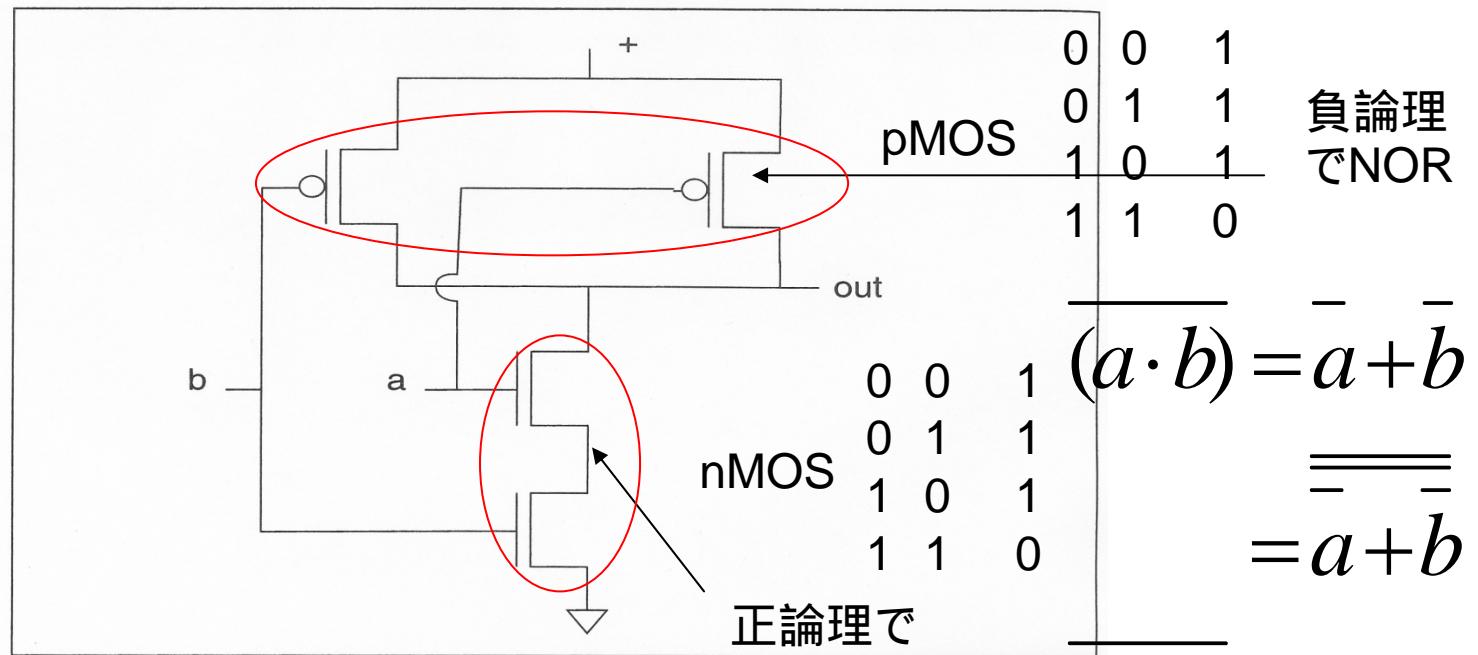

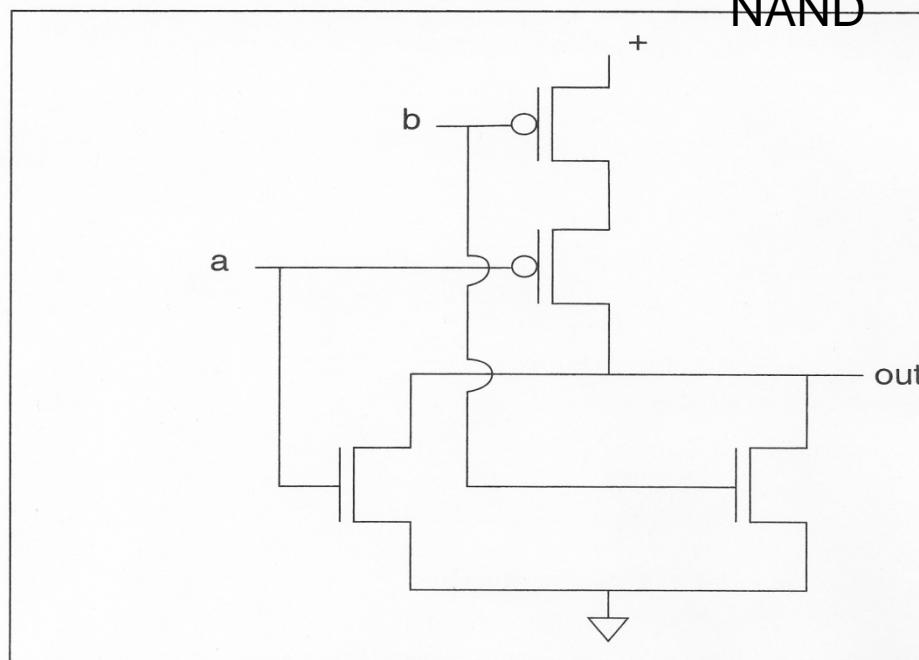

NAND

NOR

## ( 2 ) 特徴

容易な設計

階層設計，機能分割

( 垂直分割と水平分割 )

互換性の実現

高級言語：機械命令レベルと独立

機械命令セット：RTと独立

# トレードオフの実現

## 乗算の例

高級言語:あり

機械命令:あり

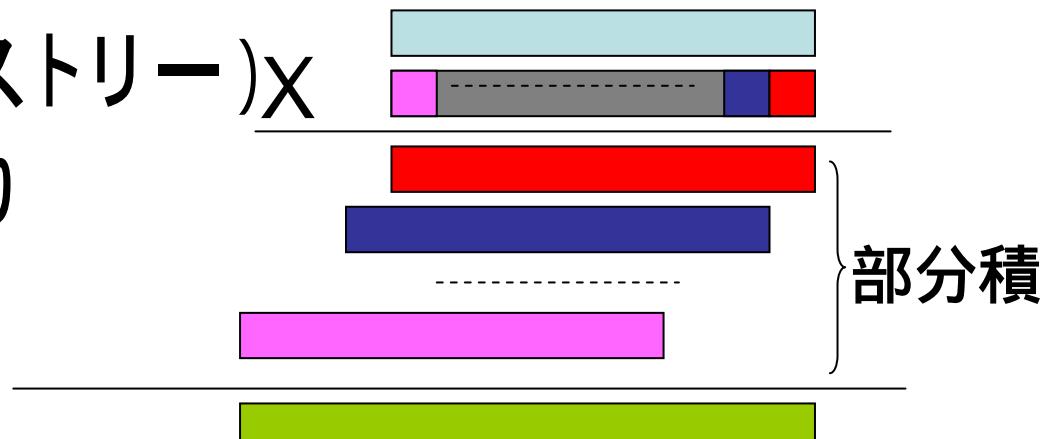

RT:あり(ワレストリー) $\times$

高級言語:あり

機械命令:あり

RT :なし

( RTレベルでの反復加算:

加算とシフト)

部分積

の総和

高級言語:あり

機械命令:なし

(機械命令で反復加算

:加算とシフト)

R T :なし

仮想化技術

# 1.10 OS

## 1 OSの必要性

複雑な機能の提供: 命令セットの拡張

大容量記憶, ファイル操作,

ネットワーク, 入出力

リソースの共有利用: 効率的な管理,

セキュリティ

多数のユーザプロセスの実行

多数のサーバプロセスの実行

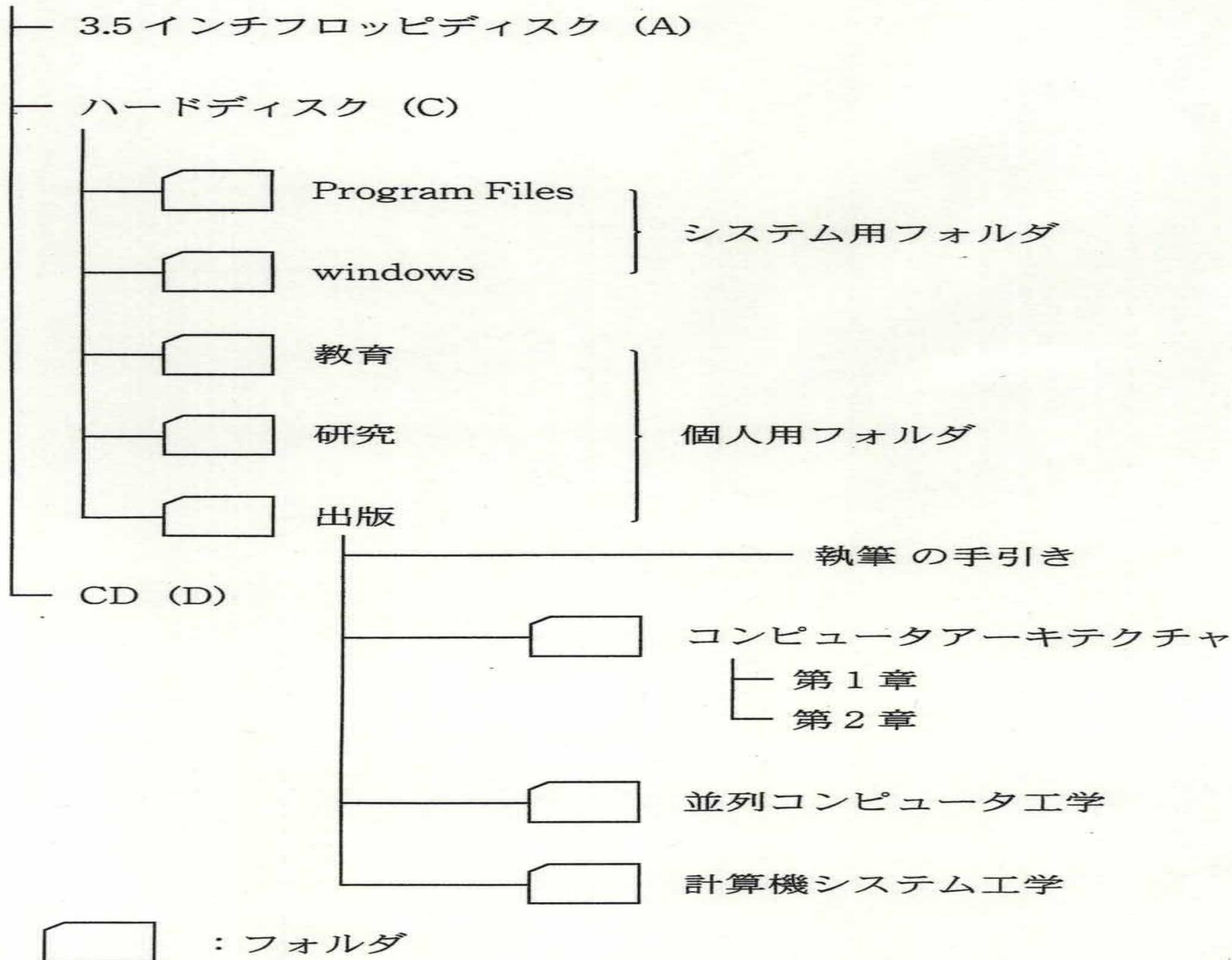

# 2 OSの機能

記憶管理

多重仮想記憶

ファイル管理

ディレクトリ管理，ファイル更新・編集

効率のよい記憶方式

入出力管理

デバイスドライバ

スケジューリング

## マイコンピュータ

図 1.11 ファイルのデータ構造

# 通信管理

## アプリケーション層

FTP, Telnet, WWW, SMTP, . . .

## TCP / UDP層

TCP: コネクション型

バーチャルチャネル

UDP: コネクションレス型

## IP層

中継ノード間での通信制御

IPアドレス

## インターフェース層

マルチキャスト機能

## 物理層

イーサネット, ATM

# プロセス管理 OSの中のOS

たくさんのプロセスの擬似的な並行実行

プロセス: OSにより管理実行されているプログラム

並列プロセスの例

長時間かかるCプログラムを実行させながら

WORDで文書作成し、プリントアウト

プリンタが動作し始め

EXCELで表計算処理を開始していると

時計の表示

電子メールの受信通知の表示

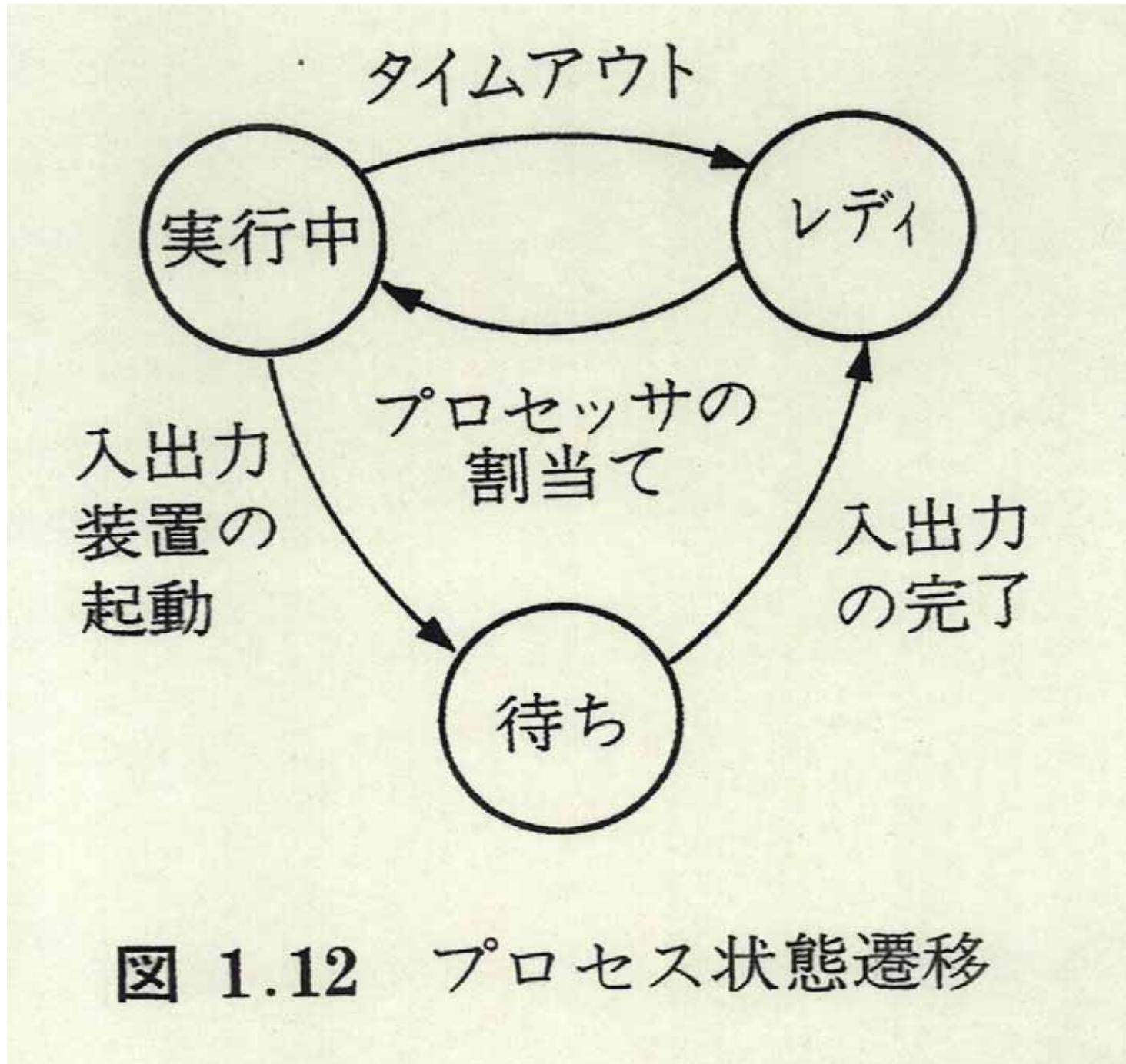

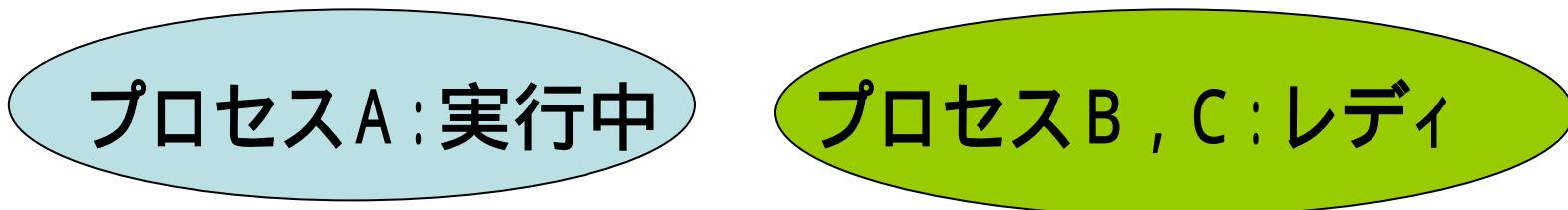

# プロセスの状態

実行中：プロセスがOSからプロセッサを割り当てられて実行中の状態

レディ：プロセスは実行可能状態であるが、OSのプロセッサ割当てがなされていない状態

待ち：プロセスに必要なデータが揃っていないので、待たねばならない状態

(1) プロセススイッチ

契機: 割込み

外部割込み: 入出力, タイマ

マシンチェック

内部割込み: 演算例外,

命令例外, ページ

フォルト, トレース

スーパーバイザーコール

多重プログラミング,

TSS (Time Sharing System)

プロセスA, B, C:レディ

OS:プロセスAを選択し, 実行させる

プロセスA:ディスクアクセス

I/O命令実行でOSに割込み

OS:プロセスAのI/O処理し, Aを待ちへ

プロセスBを選択し, 実行へ

プロセスB:一定時間実行(タイムクアンタム)

10 msec

タイマー割込み

OSがBをレディへ,Cを選択

プロセスC:実行

プロセスB:レディ

プロセスA:待ち

ディスクからI/O割込み

OSがチェックし、プロセスAのディスク

アクセス終了を知る

OSはプロセスAをレディへ

プロセスC: 実行中

プロセスB: レディ

プロセスA: レディ

プロセスC: ディスクアクセス

OS: プロセスCを待ちへ、

プロセスAを実行へ

プロセスA: 実行

プロセスB: レディ

プロセスC: 待ち

( 2 ) プロセススケジューリング

( 3 ) プロセス間通信

同期 : 排他制御 , 事象待ち

メッセージ交換

メモリ空間共有 , 非共有

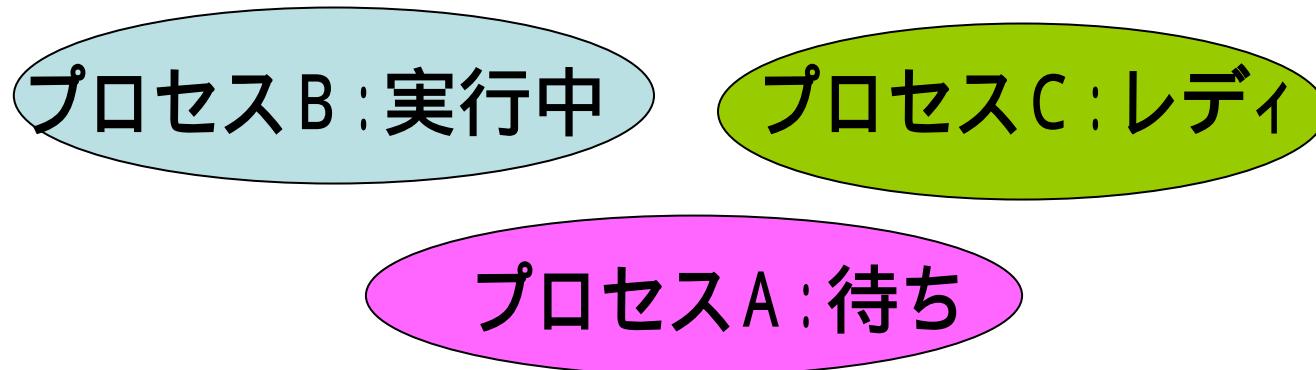

# 3 O S の構成

シンプルな構成の必要性

マイクロカーネル

## 1.11 コンピュータの分類

### 1 基本ハードウェア技術(構成部品)

機械式:歯車など

電気機械式:リレー

電子式:真空管, Tr, 集積回路

光式:レンズなど

DNA:?

量子:?

リレー

ST管

MT管

EPROM

TR LSI

VLSI

真空管

8ビットプロセッサ

6800

32ビットプロセッサ

SPARC

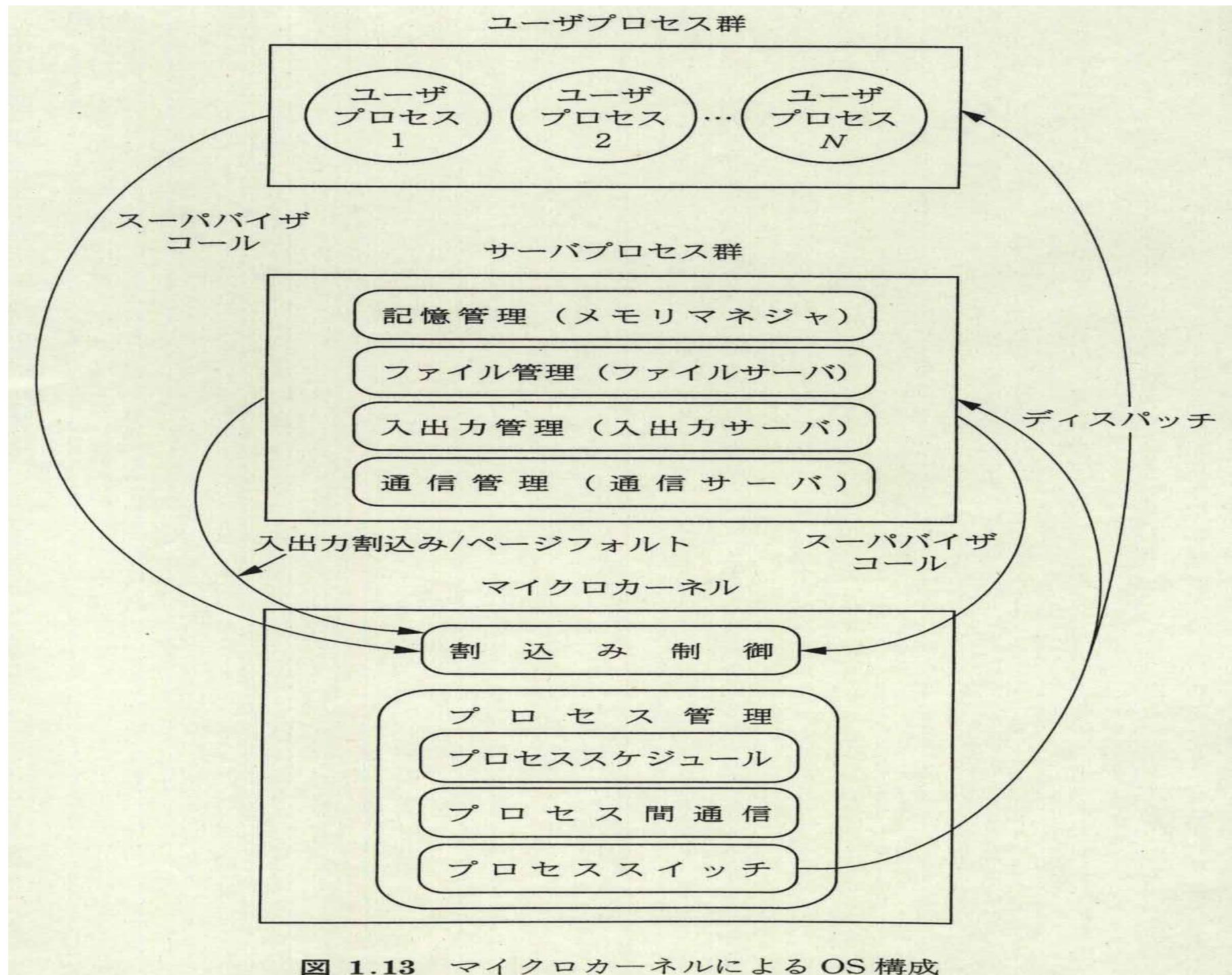

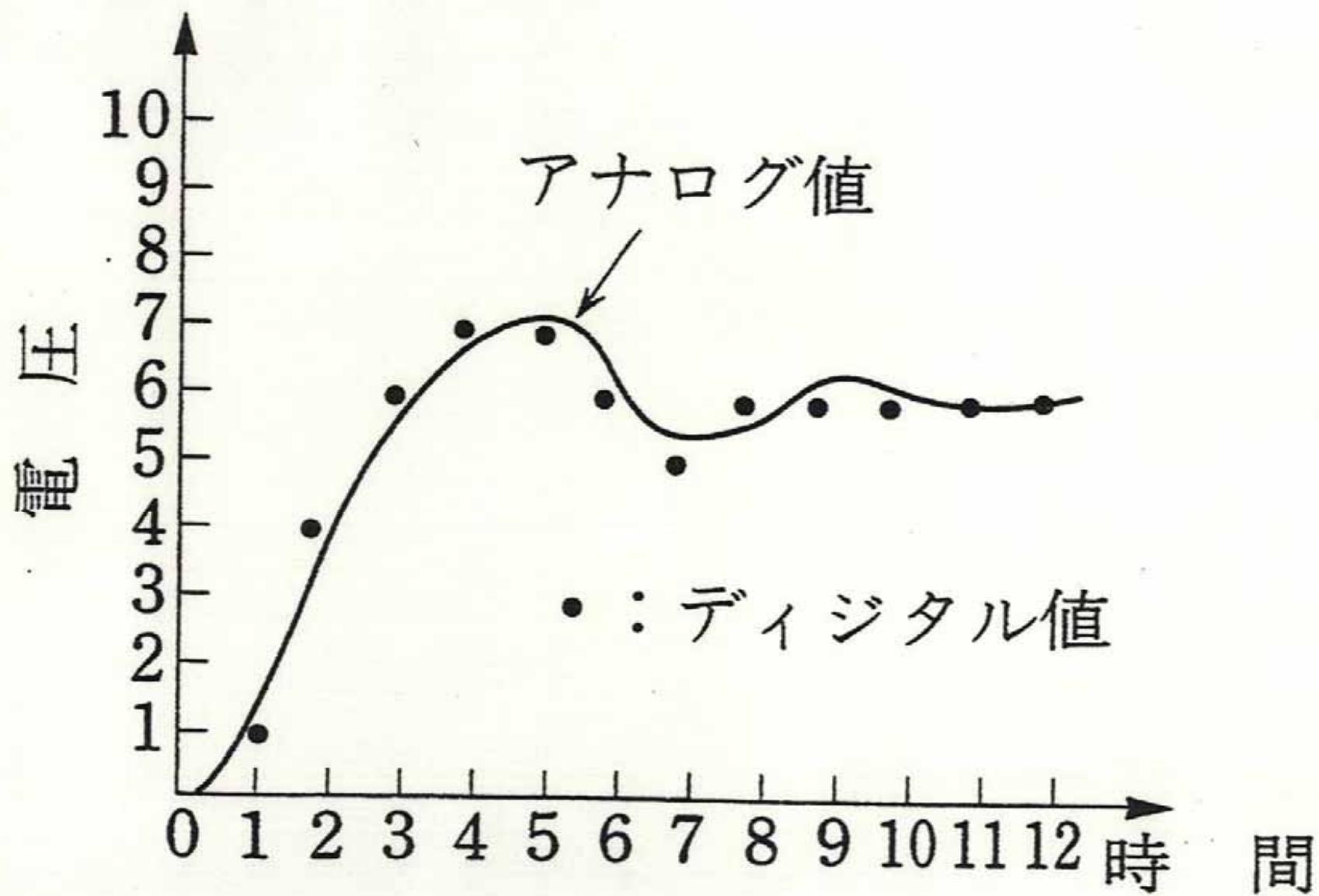

## 2 取り扱う量：アナログかデジタルか

アナログ量：連続量

デジタル量：離散量

シャノンの標本化定理

AD変換，DA変換

図 1.14 アナログ量とデジタル量

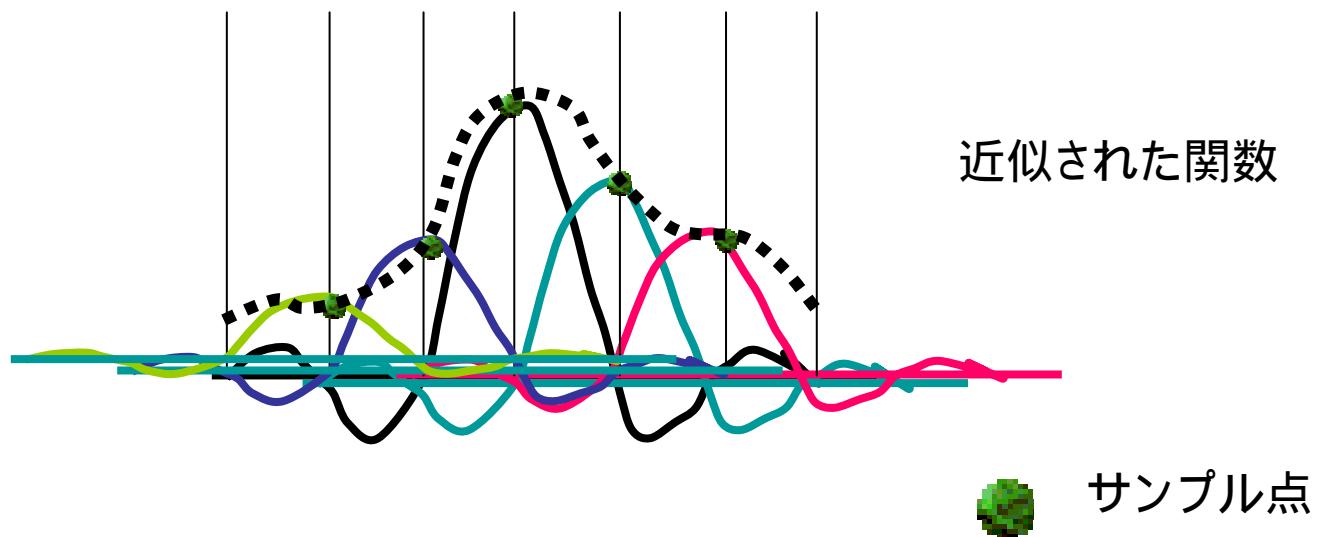

# シャノンの標本化定理の証明

## フーリエ変換

$$C(\nu) = \int_{-\infty}^{\infty} f(t) \exp(-2\pi j \nu t) dt$$

$$f(t) = \int_{-\infty}^{\infty} C(\nu) \exp(-2\pi j \nu t) d\nu$$

パルス

$$f(t) = 1 : |t| < (1/2)\theta, 0 : |t| > (1/2)\theta$$

$$C(\nu) = \theta \frac{\sin \pi \nu \theta}{\pi \nu \theta}$$

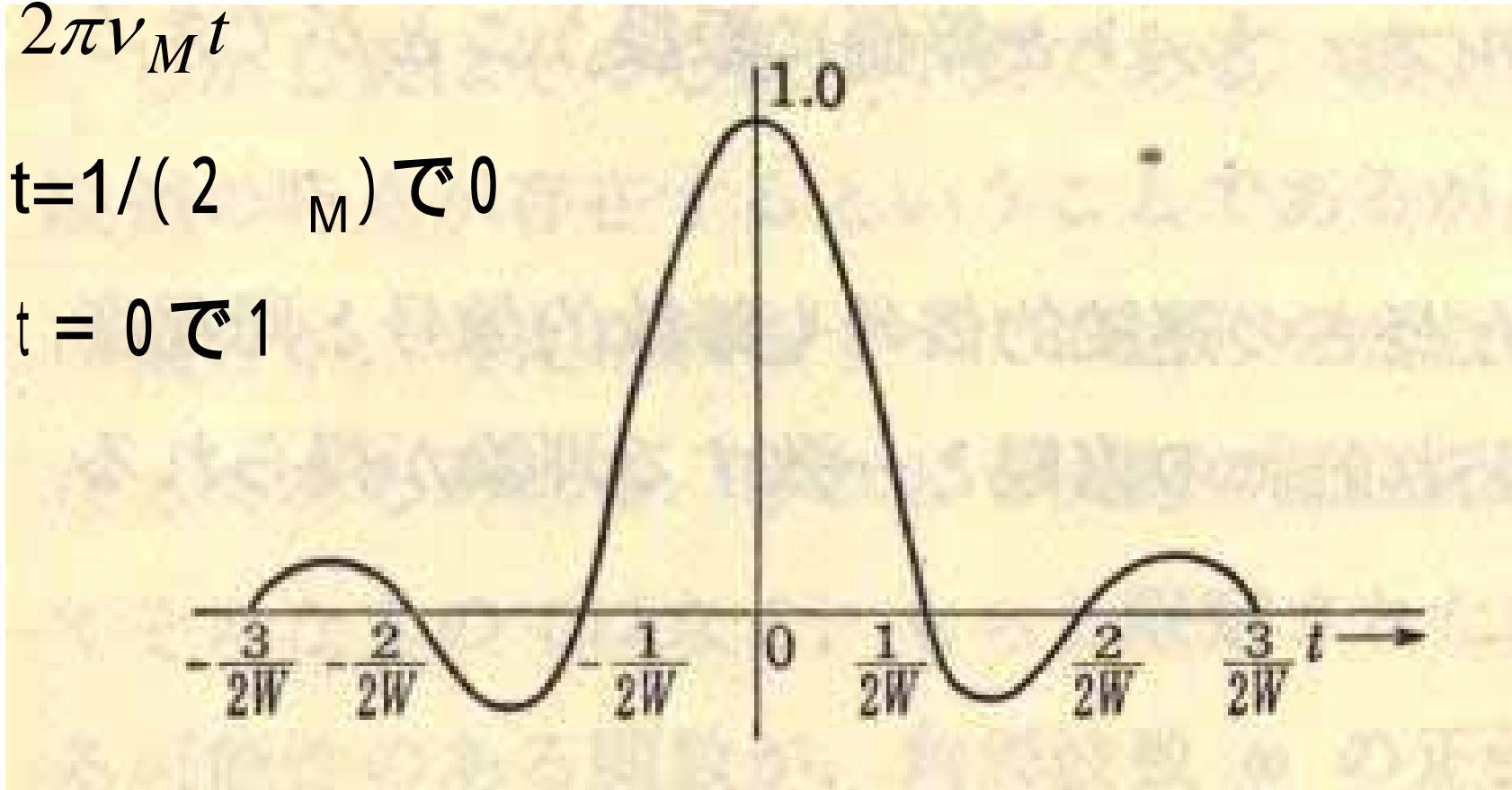

標本化関数

$$f(t) = 2\nu_M \frac{\sin 2\pi \nu_M t}{2\pi \nu_M t}$$

$$C(\nu) = 1 : |\nu| < \nu_M, 0 : |\nu| > \nu_M$$

$f(t)$ : 臨界周波数  $\nu_M$  の周波数成分のみ

$C(\nu)$  は  $-\nu_M$  から  $\nu_M$  までの成分を有する

$C(\nu)$  のフーリエ級数は

$$C(\nu) = \sum_k a_k \exp\left(\pi j k \nu / \nu_M\right)$$

$a_k$  は

$$\int_{-\nu_M}^{\nu_M} C(\nu) \exp\left(-\pi j k \nu / \nu_M\right) d\nu =$$

$$\int_{-\nu_M}^{\nu_M} \sum_k a_k \exp(-\pi j \nu (k' - k) / \nu_M) d\nu$$

$$= 2 a_k \nu_M$$

式より

$$f(t) = \int_{-\infty}^{\infty} C(\nu) \exp(2\pi j \nu t) d\nu$$

$t=k/(2\nu_M)$  とすると

より、

$f(k/(2\nu_M)) = \int_{-\nu_M}^{\nu_M} C(\nu) \exp(\pi j k / \nu_M) d\nu$

$= 2\nu_M a_{-k}$

標本点を知れば、 $a_{-k}$  が求まり

$$C(\nu) = \sum_k a_k \exp(\pi j k \nu / \nu_M)$$

が定まる。

, 式より

$$\begin{aligned} f(t) &= \sum a_k \int_{-\nu_M}^{\nu_M} \exp(\pi j k \nu / \nu_M) \exp(2\pi j \nu t) d\nu \\ &= \sum a_{-k} \int_{-\nu_M}^{\nu_M} \exp(-\pi j k \nu / \nu_M) \exp(2\pi j \nu t) d\nu \\ &= \frac{1}{2\nu_M} \sum f(k/(2\nu_M)) \int_{-\nu_M}^{\nu_M} \exp(\pi(2\nu_M t - k)j\nu / \nu_M) d\nu \\ &= \sum f(k/(2\nu_M)) \frac{\sin \pi(2\nu_M t - k)}{\pi(2\nu_M t - k)} \end{aligned}$$

## 標本化関数

$$\sin 2\pi\nu_M t$$

$$2\pi\nu_M t$$

$t = 1/(2\nu_M)$  で 0

$t = 0$  で 1

$$W = \nu_M$$

- 3 - 2 - 1 0 + 1 + 2 + 3

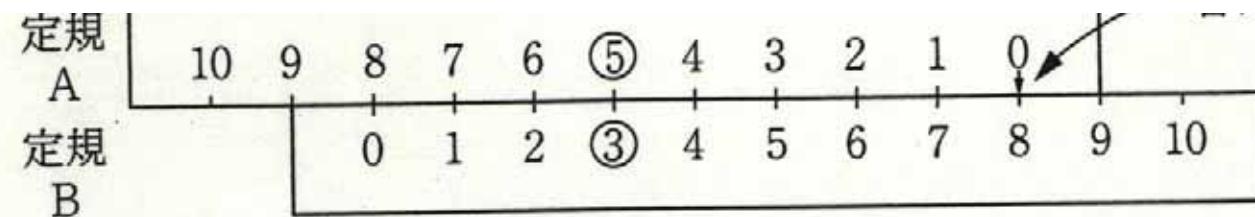

# アナログとデジタルは違わない？

メモリとの親和性

精度

信頼性

汎用性

アナログコンピュータ

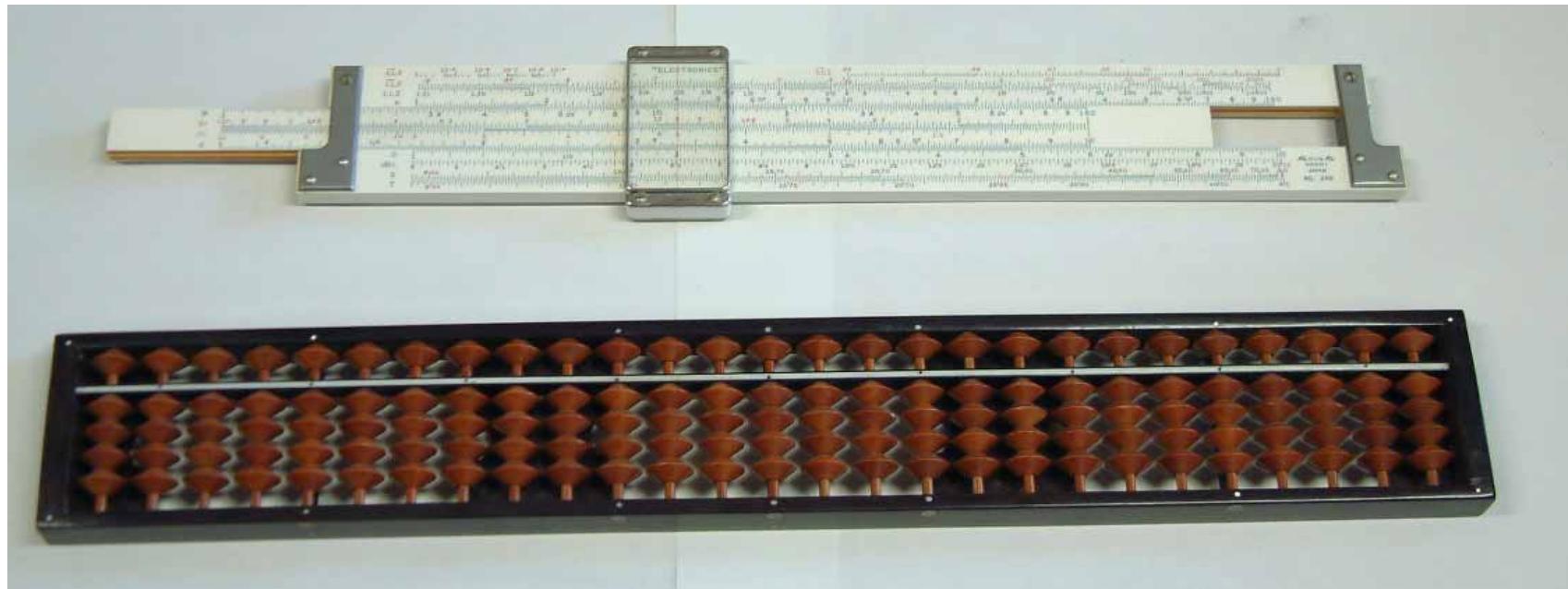

問題解決 > 物理現象・量に写像

例: 計算尺

プログラミング

配線

デジタルコンピュータ

問題解決 > アルゴリズムによる

記号操作

例: そろばん

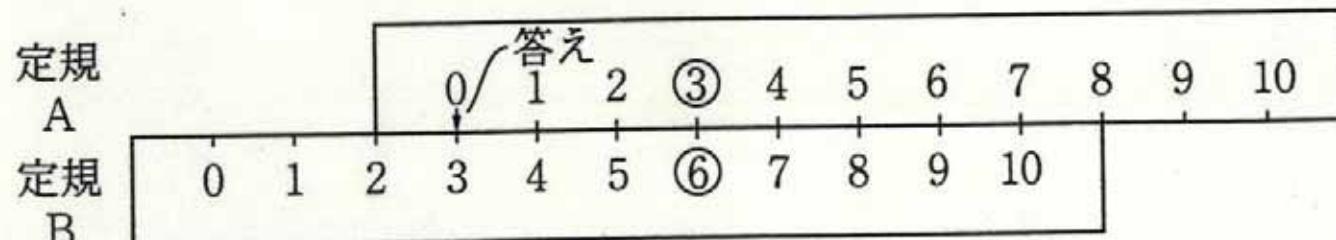

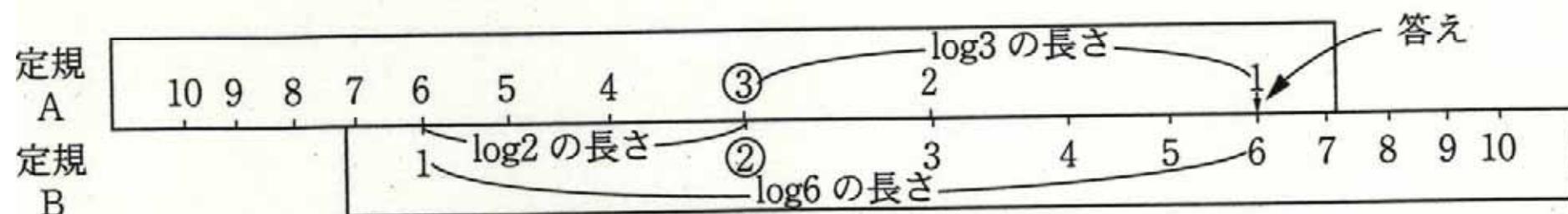

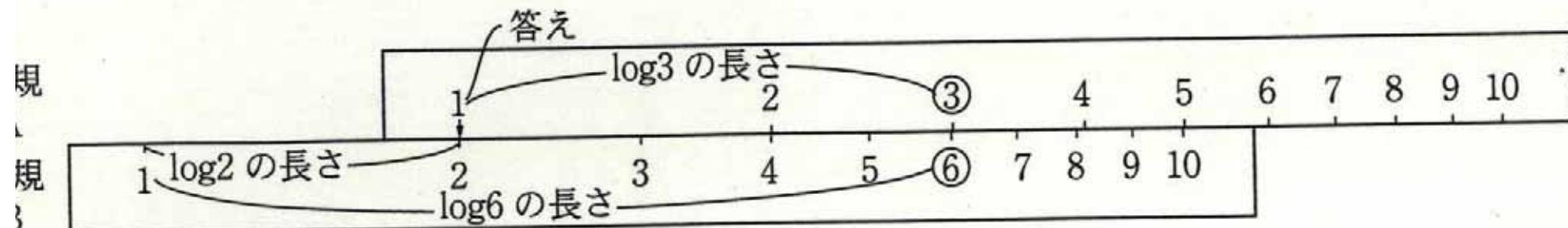

(a) 加算 ( $3+5$ )

(b) 減算 ( $6-3$ )

(c) 乗算 ( $2 \times 3$ )

(d) 除算 ( $6 \div 3$ )

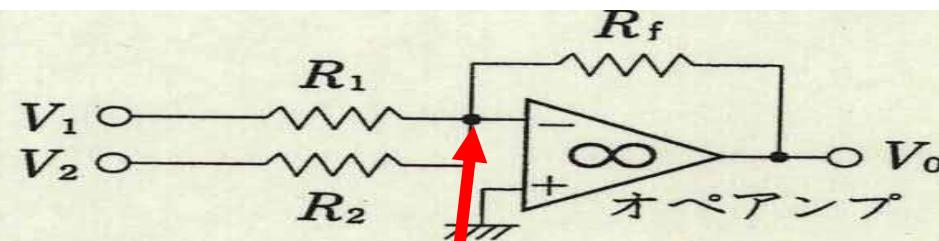

(a) 加算器

$$V_0 = -R_f \left( \frac{V_1}{R_1} + \frac{V_2}{R_2} \right)$$

仮想接地: 0 V

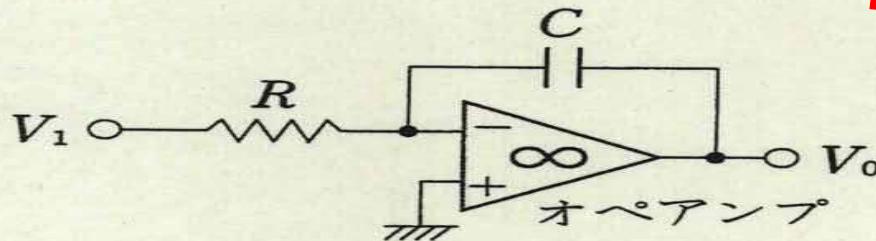

$$(b) 積分器 \quad V_0 = -\frac{Q}{C} = -\frac{1}{CR} \int V_1 dt$$

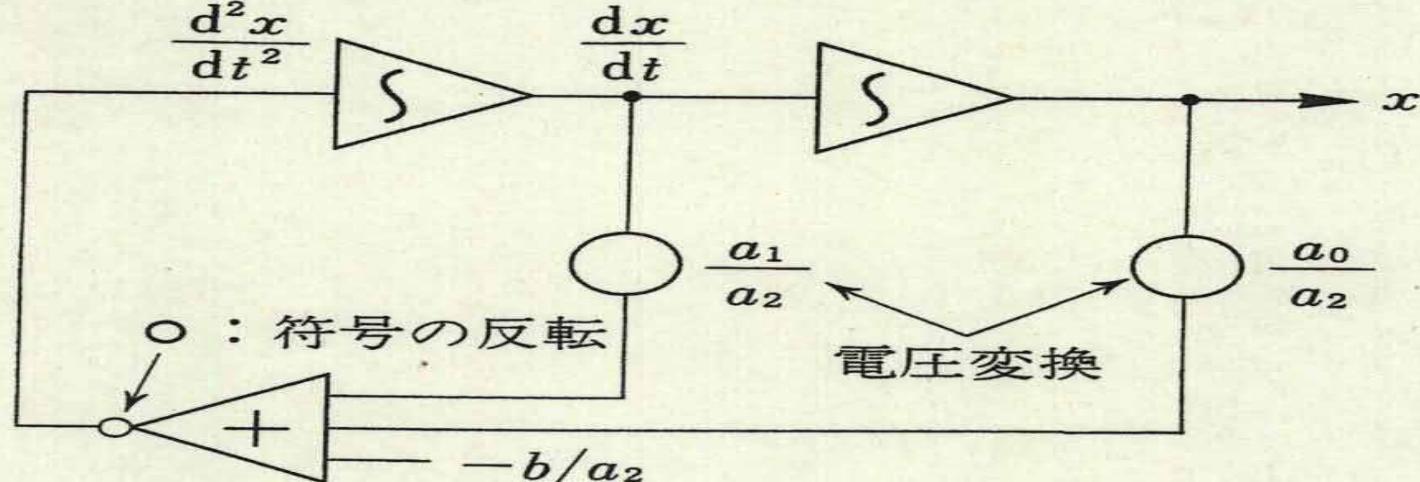

$$a_2 \frac{d^2x}{dt^2} + a_1 \frac{dx}{dt} + a_0 x = b$$

(c) 常微分方程式を解く回路

### 3 制御方式

集中制御・逐次制御

ノイマン式

分散制御・並列制御

非ノイマン式

データフロー

ニューラルネット

光コンピュータ

DNAコンピュータ

量子コンピュータ