# 第4章 記憶装置の構成

## 4.1 記憶階層方式

### 4.1.1 記憶装置への要求事項

- (1) 速度: アクセスタイムとサイクルタイム

- (2) 容量

- (3) 不揮発性(Non-Volatile) : 電源切っても記憶は残る

- (4) 書換え可能性

- (5) ランダムアクセス性

- (6) 可搬性

## 4.1.2各種の記憶デバイスの速度と容量

### (1)半導体メモリ

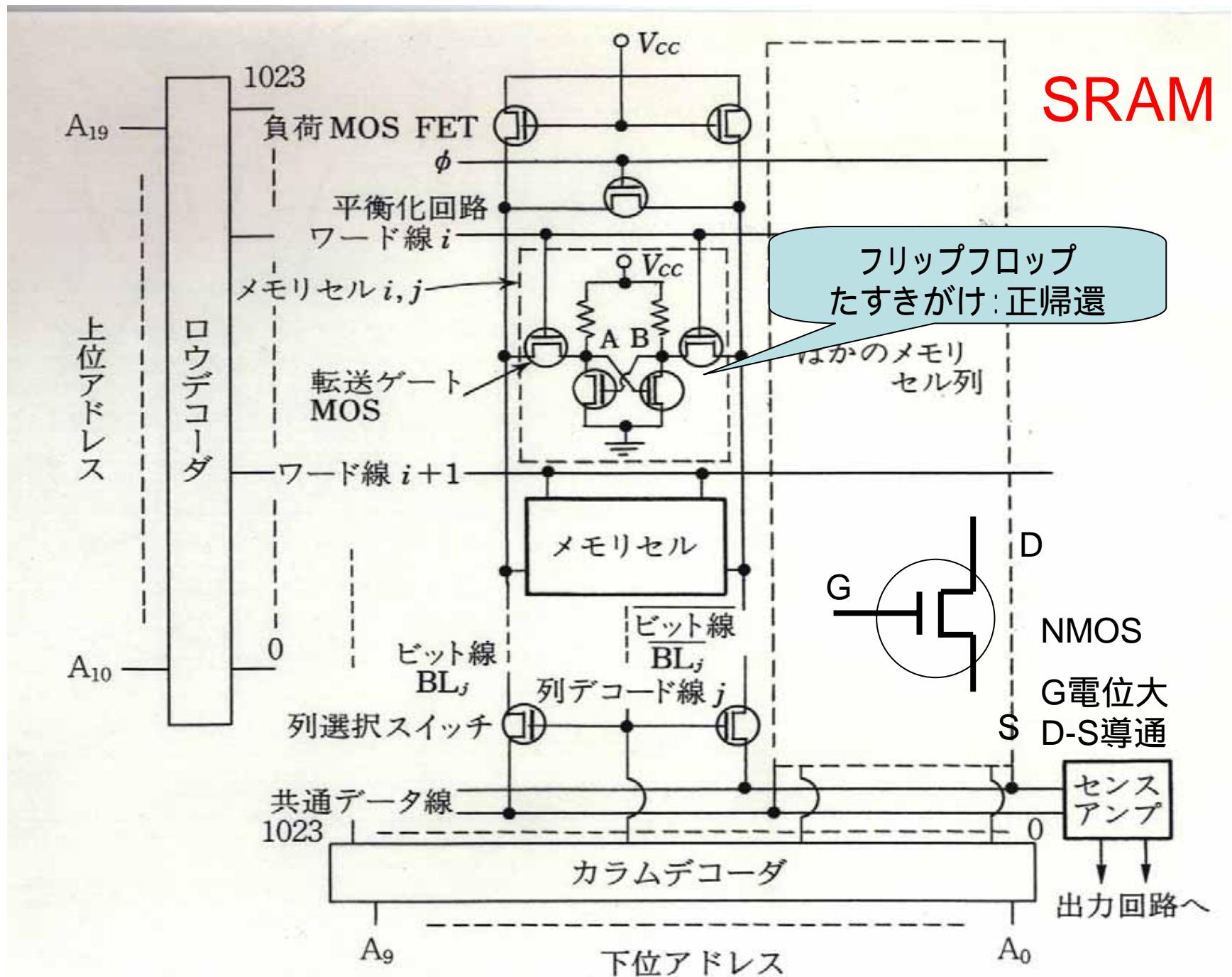

SRAMとDRAM

S:Static

電気を入れておけば安定に情報を記憶

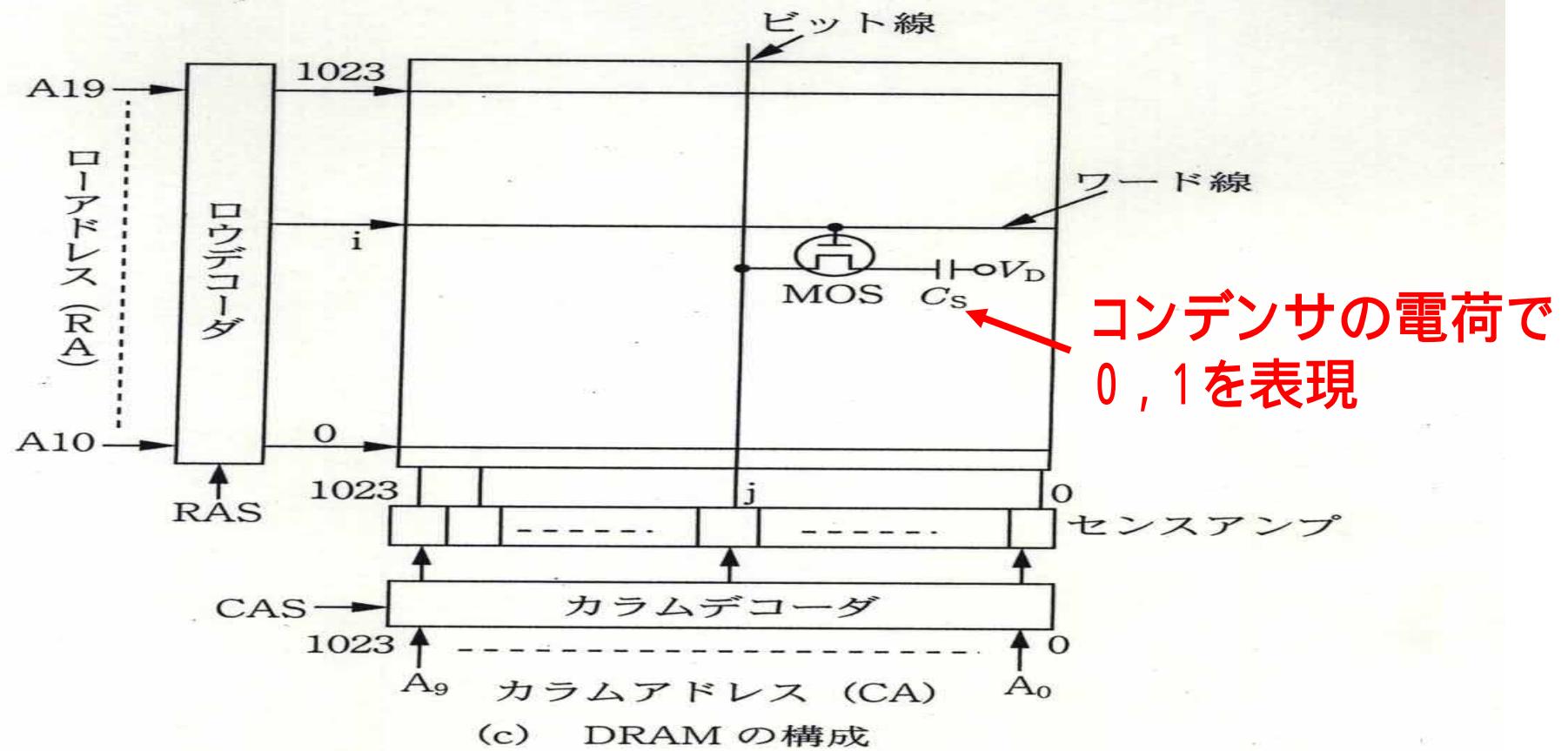

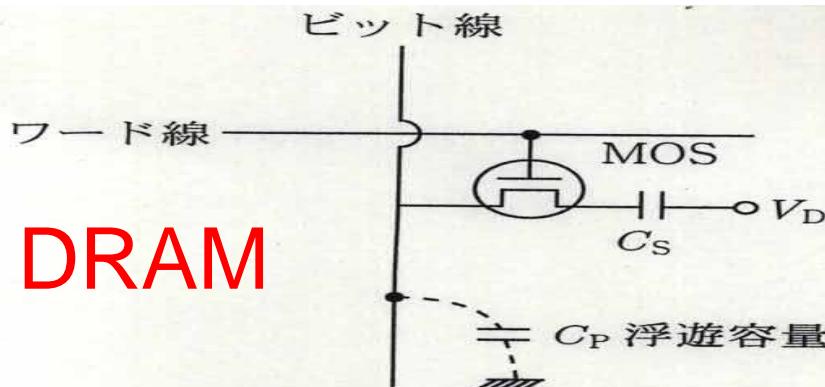

D:Dynamic

電気を入れておいても、ときどき読み出さない

と記憶がなくなる リフレッシュが必要

図 4.1 SRAM の構成 [電子情報通信ハンドブック, オーム社 (1988)]

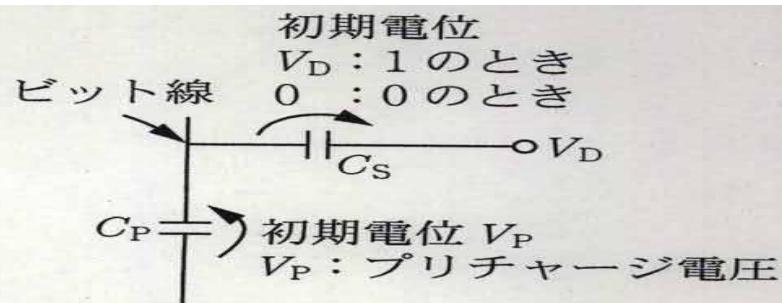

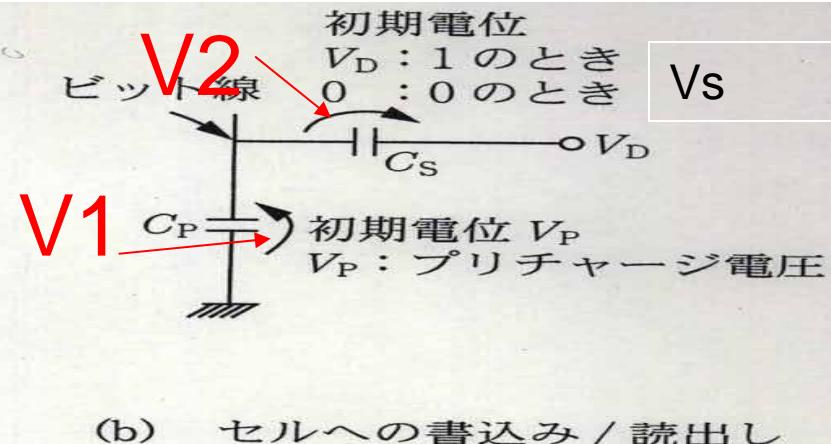

図 4.2 DRAM の構成の動作

$$V_1 + V_2 = V_D$$

$$V_1 C_p - V_2 C_s = V_p C_p - V_s C_s$$

$$V_1 = (V_p C_p - V_s C_s + V_D C_s) / (C_p + C_s)$$

電荷保存則

# DRAM

1の読み出し時:  $V_p C_p / (C_p + C_s)$

0の読み出し時:  $(V_p C_p + C_s V_D) / (C_p + C_s)$

$V_p = V_D / 2$  とすると、

1の読み出し時:  $V_D (1 - C_s / (C_p + C_s)) / 2$

0の読み出し時:  $V_D (1 + C_s / (C_p + C_s)) / 2$

高速ページモード, SDRAM, RDRAM

## リフレッシュ

セル当たり 96 msec ごと

1行単位で同時に読み出して書き込む

# DRAMについての私の経験

- 1Kb DRAM

1974に購入(東光株式会社)

アクセスタイム 350nsec

容量 256KB

価格 1000万円

- 256Mb DRAM

2001年にパソコンのアドオンメモリとして購入

アクセスタイム 70nsec

容量 128MB

価格 5000円

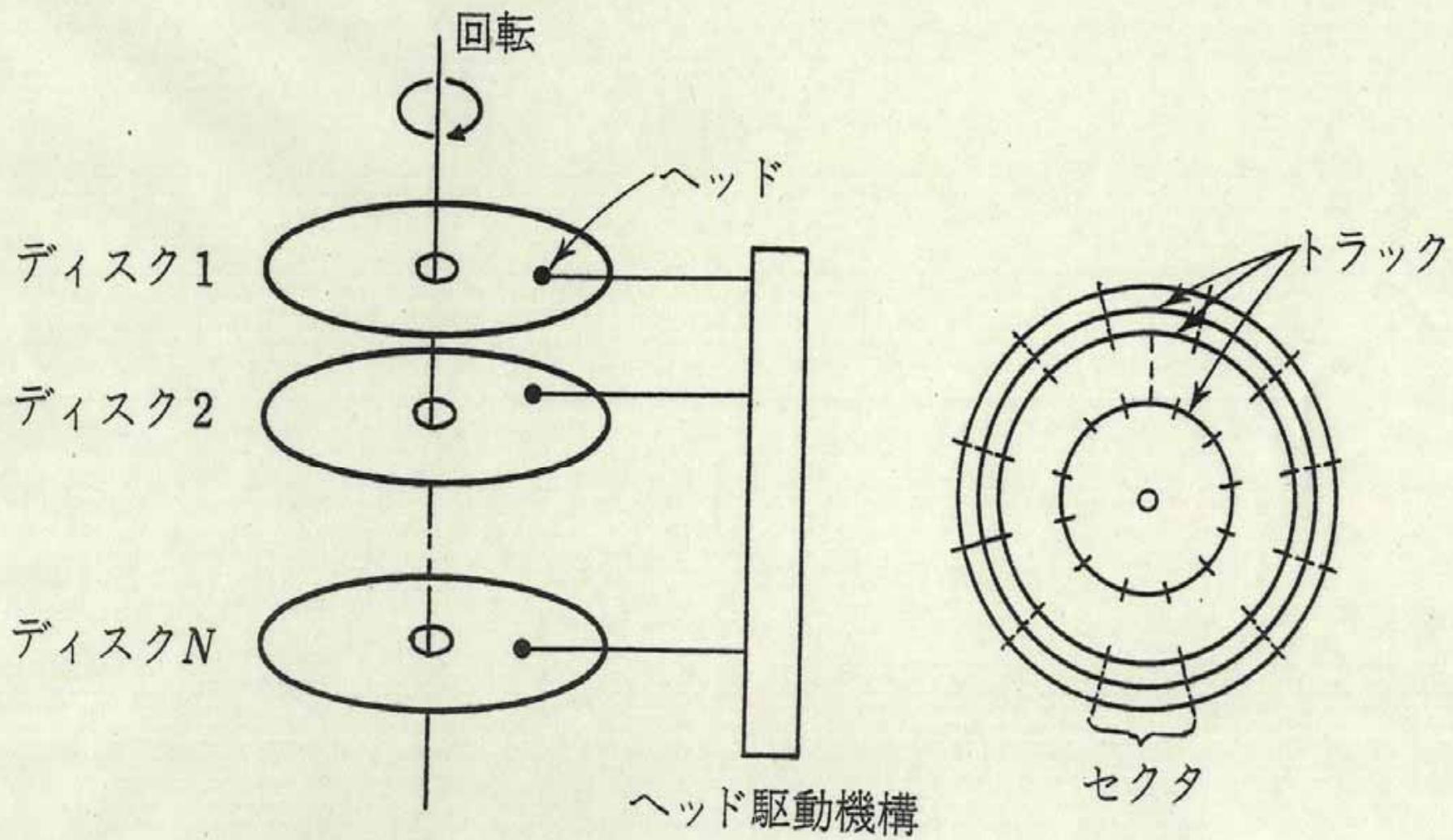

## (2) 固定型補助記憶装置

### ハードディスク

年率: 60%で容量増加

浮上隙間は 10~20 nm 程度

トラック数: 5,000~30,000

セクタ数: 100~500

セクタバイト数: 512B

シーク (seek) 時間: 5~12 msec

回転待ち (rotation latency)

3,600~15,000 RPM (Rotations Per Minute)

3,600 RPM で  $1/(2 * 60) = 8$  msec

7,200 RPM で 4 msec

図 4.4 磁気ディスク装置 (HDA) の構成

### (3)可搬(リムーバブル)型補助記憶装置

フロッピディスク(FD)

フラッシュ(flash memory)

SuperDisk,

光および光磁気ディスク

CD-R(追記型, 一回の書き込みのみ可能)

CD-RW(複数回の読み出し書き込みが可能)

MO(Magneto - Optical)

DVD(Digital Versatile Disk) - RAM

カセット型磁気テープ

2倍速, 4倍速のドライブ装置:

音楽用CDの基準データ転送速度

150KB/sの何倍

## (4)リードオンリメモリ(ROM)

マスクROM

PROM(Programmable ROM)

EPROM(Erasable PROM)

EEPROM(Electrically Erasable PROM)

OSなどの基本プログラム部分の格納

例えばローダ

制御記憶などのデコーダ

文字パターン

関数表

表 4.1 記憶素子/装置の諸元 (1999 年現在)

| 素子・装置                                | 容 量                            | ア クセス 時 間                                            | 転送速度                     |

|--------------------------------------|--------------------------------|------------------------------------------------------|--------------------------|

| SRAM                                 | 4~16 Mb                        | 10~30 ns                                             | —                        |

| DRAM                                 | 16~256 Mb                      | 30~100 ns                                            | —                        |

| SDRAM                                | 16~128 Mb                      |                                                      | 100 Mb/s                 |

|                                      |                                | RAS より 2~3 クロック, CAS より 2~3 クロック, 以後 1 クロックごとにバースト転送 |                          |

| 補助記憶装置: 固定型<br>磁気ディスク                | 4~20 GB<br>(記憶密度 1~5 Gb/平方インチ) | 10~20 ms                                             | 10~50 MB/s               |

| 補助記憶装置: リムーバブル型<br>半導体記憶<br>フラッシュメモリ | 10~240 MB                      |                                                      | W 0.8 MB/s<br>R 8 MB/s   |

| 磁気記憶<br>フロッピディスク                     | 1.44 MB                        | 100 ms                                               | 100 KB/s                 |

| 光磁気ディスク(MO)                          | 0.64~1.3 GB                    | 30 ms                                                | 3~6 MB/s                 |

| 光コンパクトディスク<br>CD-ROM<br>(書き込み不可)     | 640 MB                         | 125 ms                                               | 3.6 MB/s                 |

| CD-R<br>(書き込み一度だけ可)                  | 640 MB                         | 170 ms                                               | W 1.2 MB/s<br>R 3 MB/s   |

| CD-RW<br>(書き込み複数回可)                  | 640 MB                         | 150 ms                                               | W 0.3 MB/s<br>R 3.6 MB/s |

| DVD                                  | 5.2 GB                         | 120 ms                                               | W 1.4 MB/s<br>R 2.8 MB/s |

| Zip                                  | 250 MB                         | 30 ms                                                | 3 MB/s                   |

| SuperDisk                            | 120 MB                         | 100 ms                                               | 680 KB/s                 |

| 磁気テープカートリッジ                          | 10~50 GB                       | 数 秒                                                  | 0.5~6 MB/s               |

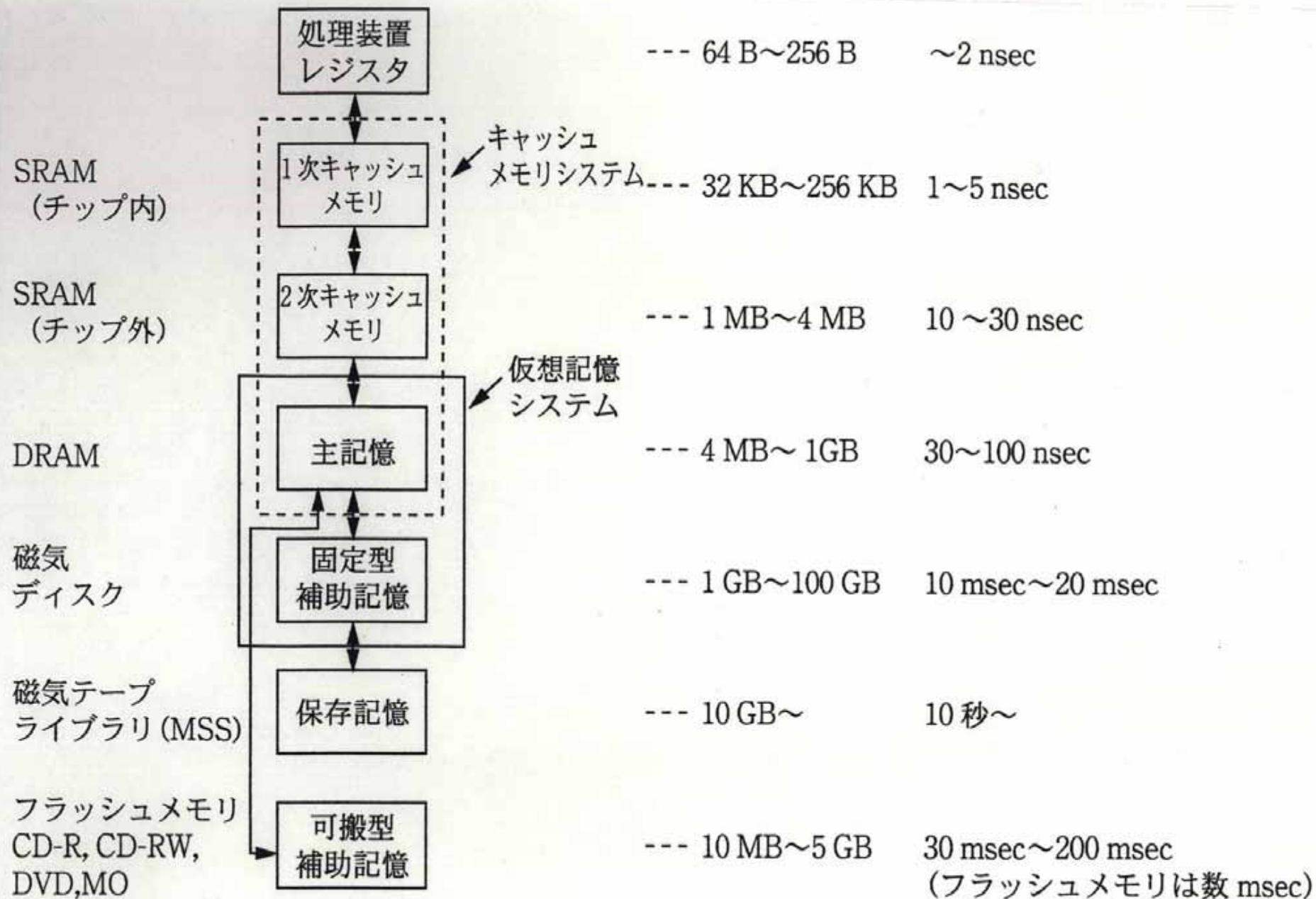

### 4.1.3 記憶階層方式

参照の局所性 (locality of references)

時間局所性 (temporal locality)

空間局所性 (spatial locality)

アナロジ:

頭の中、メモ帳、机上の本、引出しのファイル、

部屋の本箱、地下倉庫

図 4.5 記憶階層方式

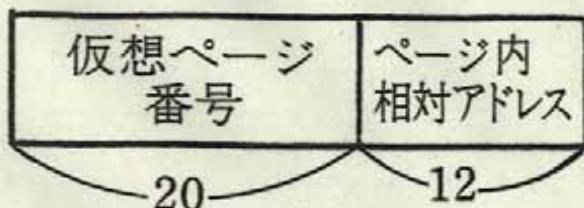

## 4.2仮想記憶

ユーザのアドレス空間: 4 GB

実記憶容量: 4 MB

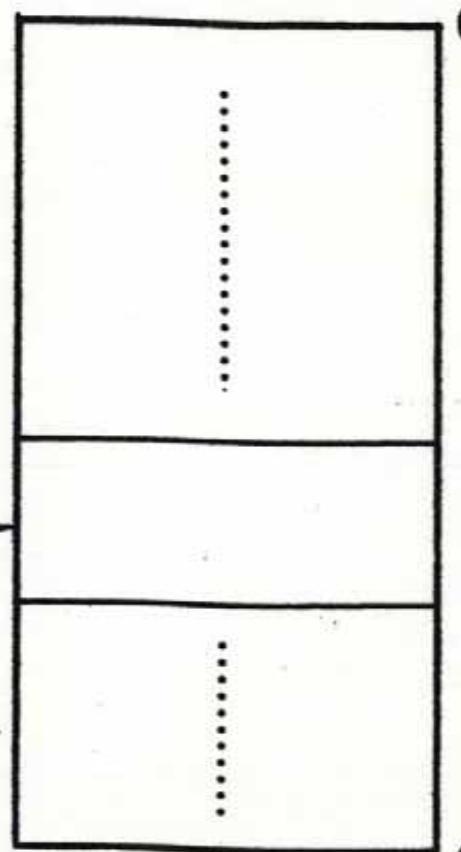

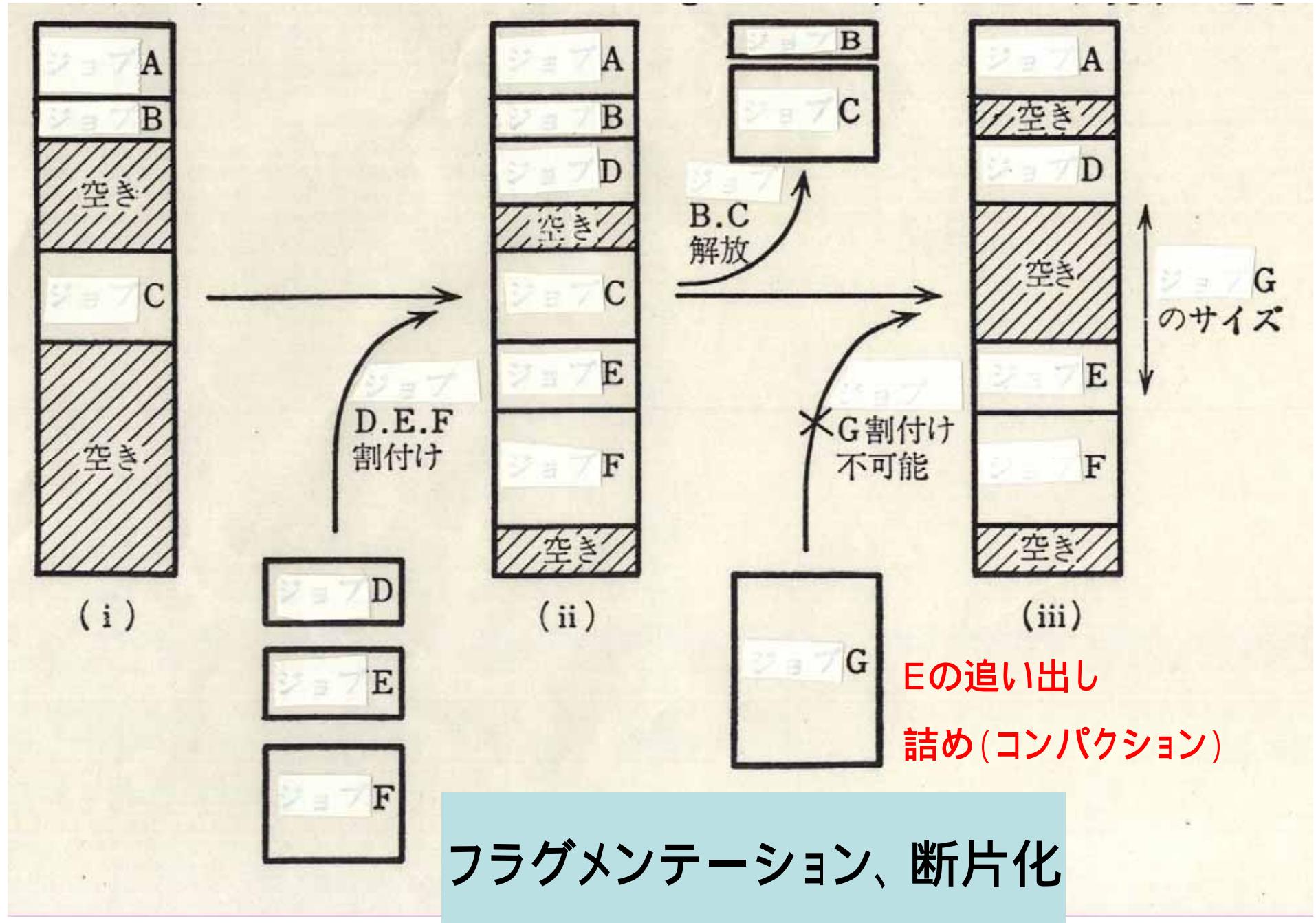

### 4.2.1基本方式

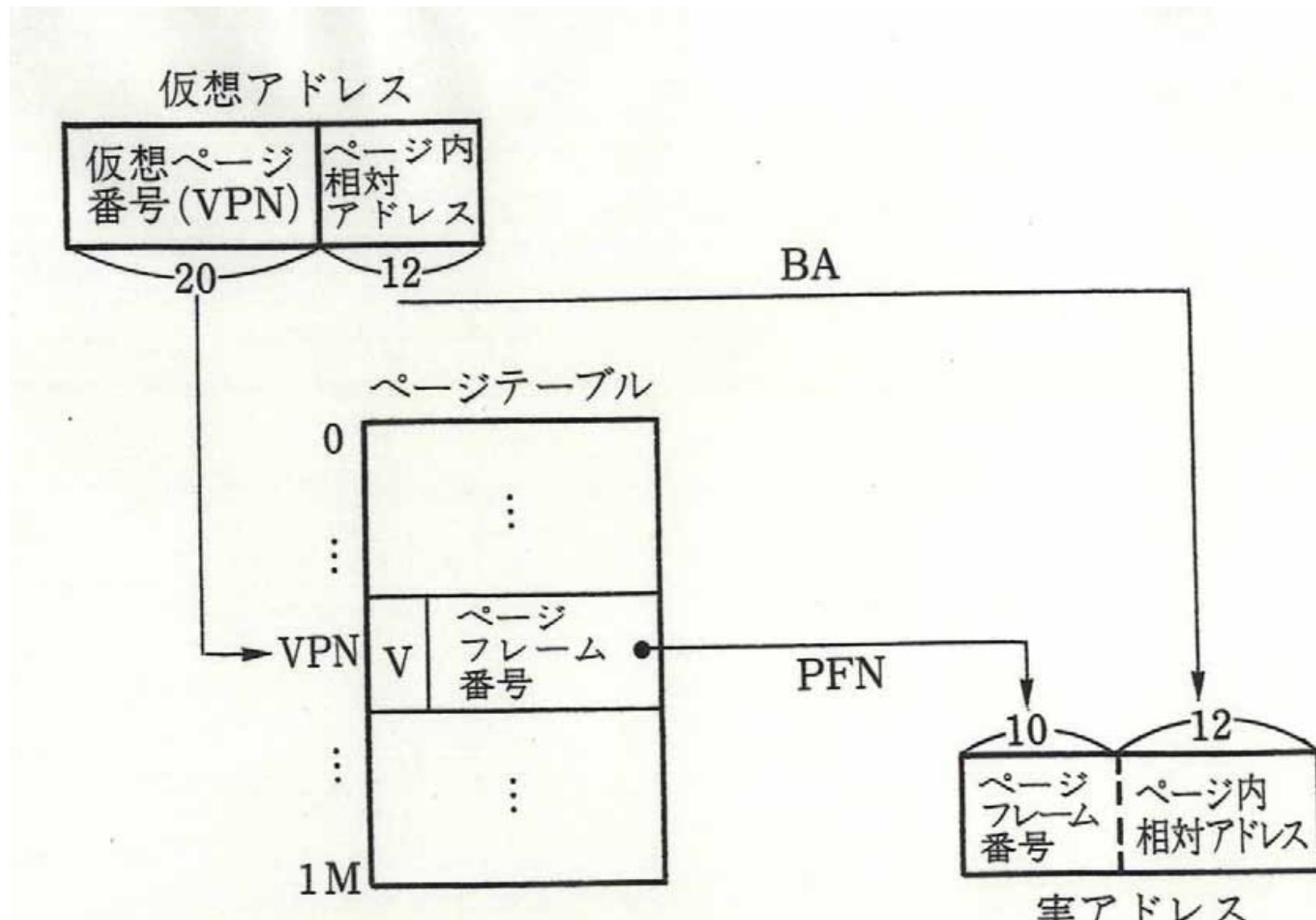

(1)ページング方式

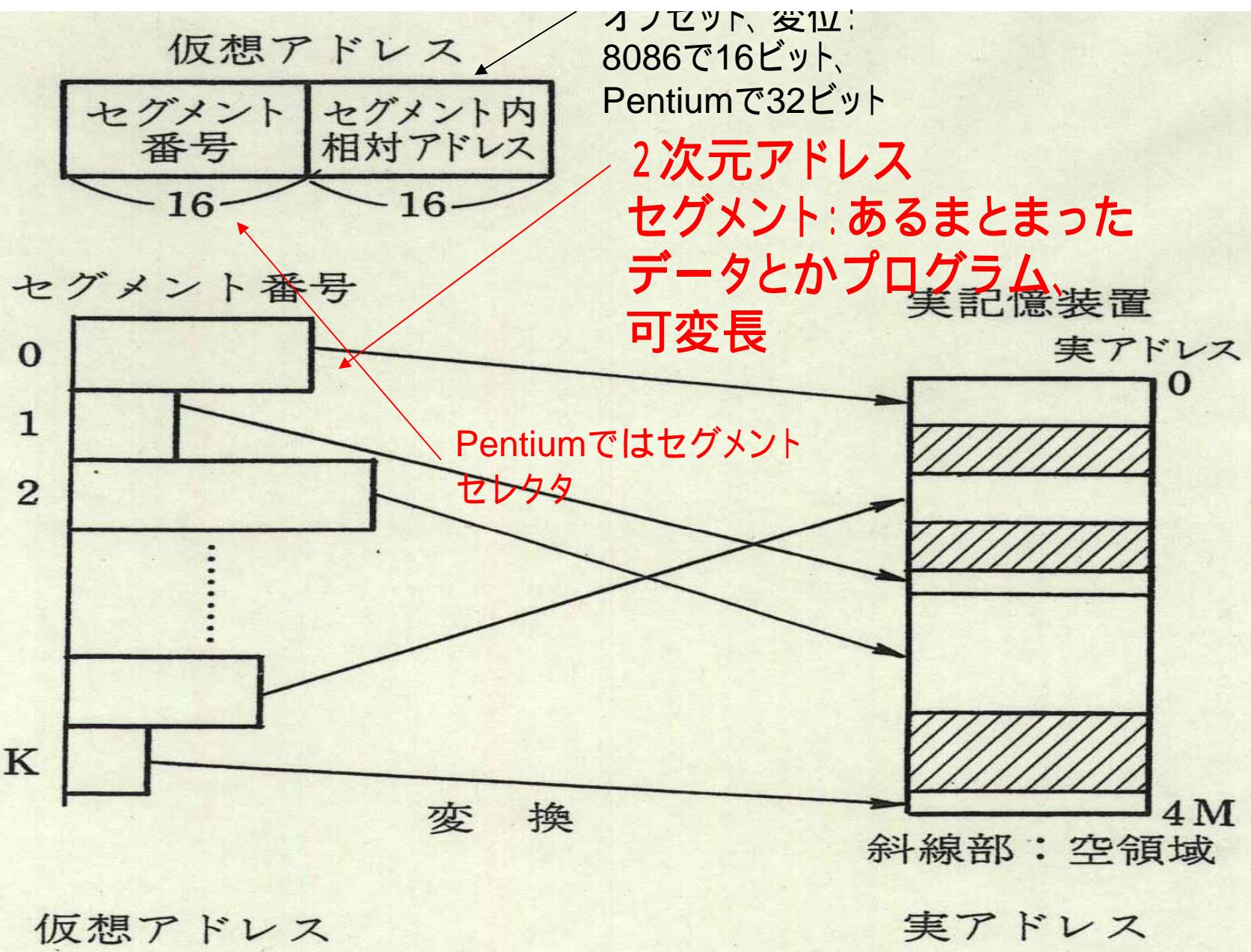

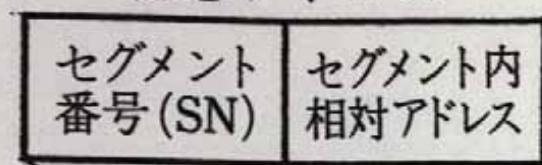

(2)セグメンテーション方式

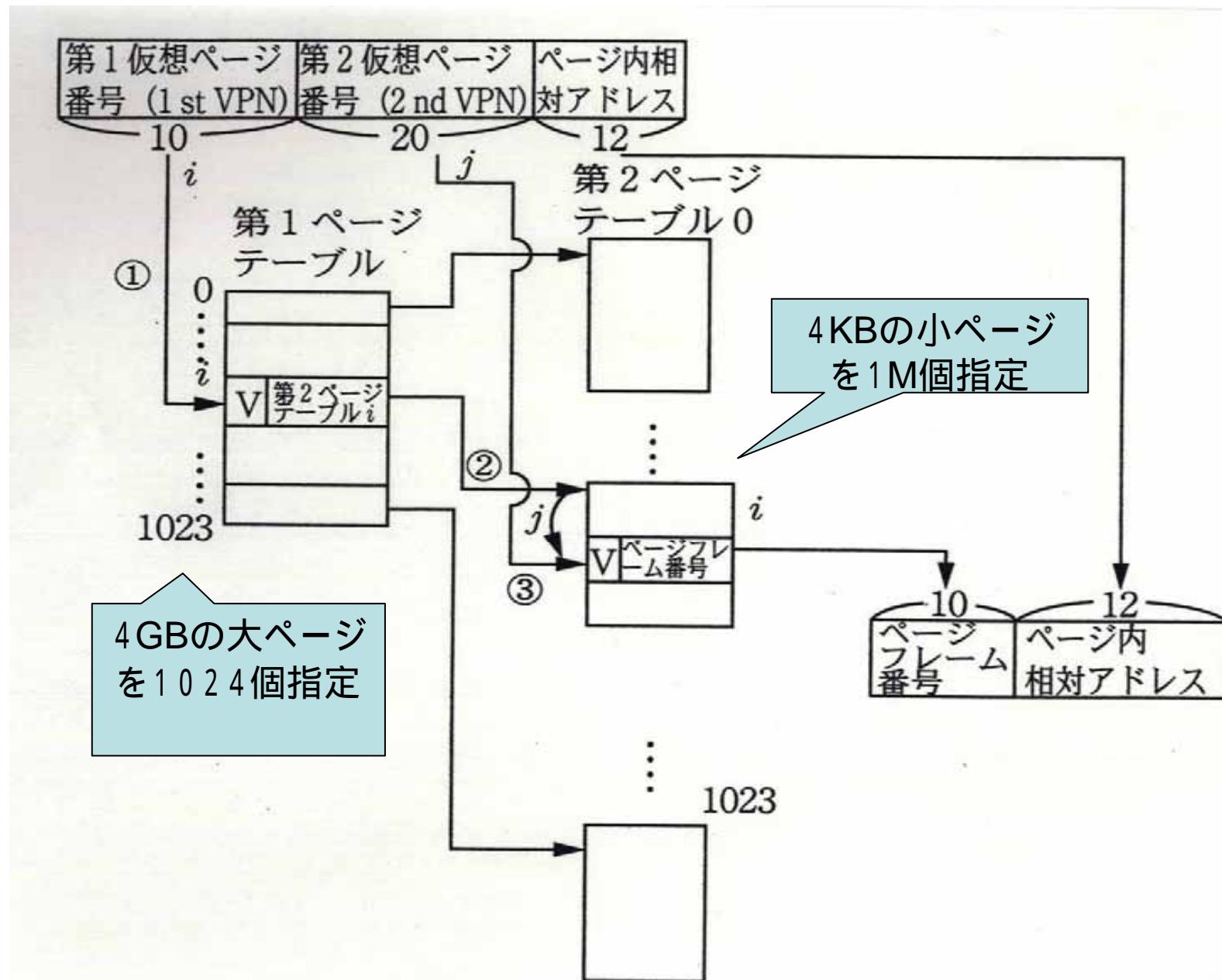

### 4.2.2写像方式

(1)直接写像

ページテーブル

多重レベルページング

セグメントテーブル

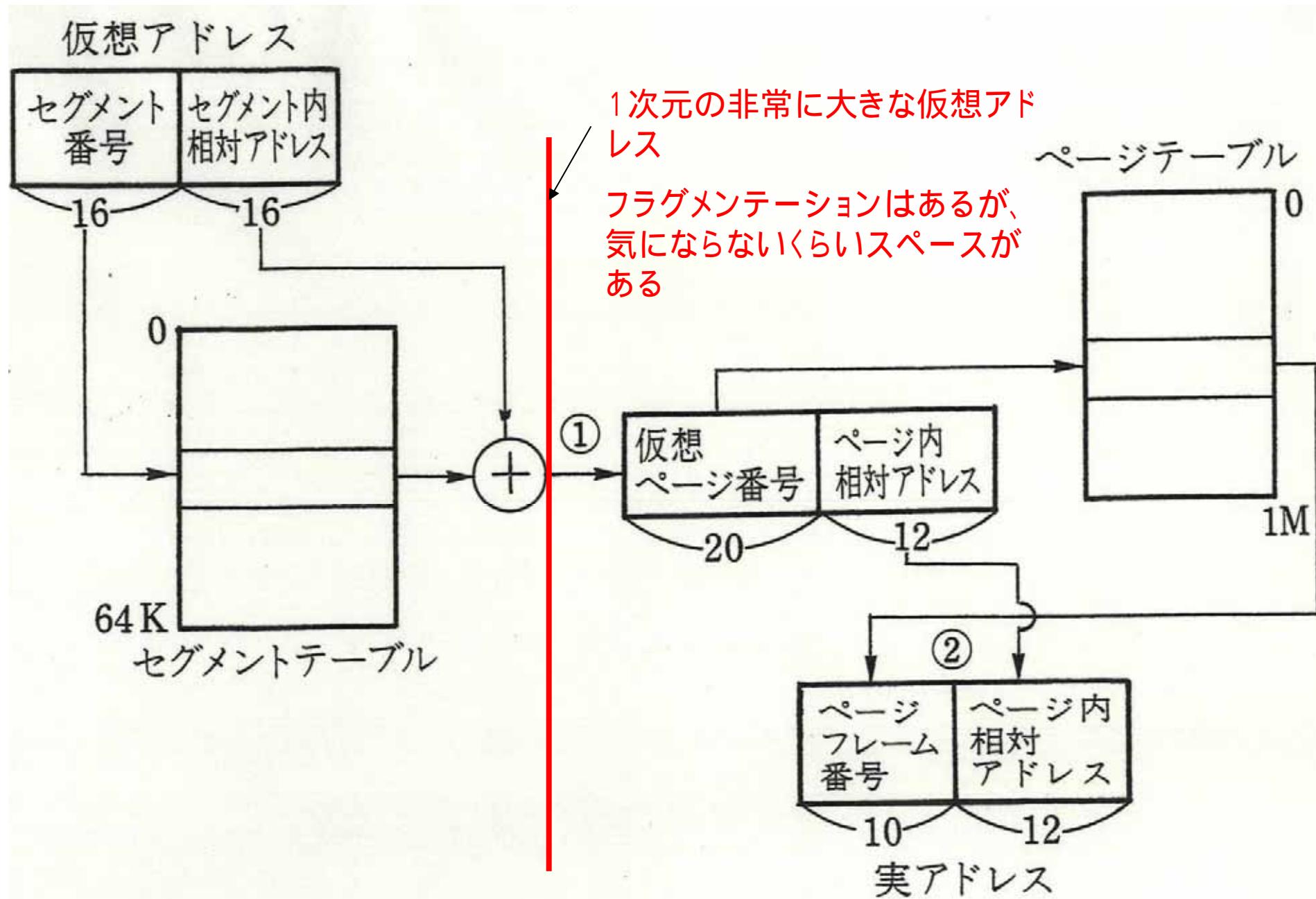

セグメンテーション + ページング

Pentiumの方式

ページ化セグメンテーション

仮想アドレス

## 1次元アドレス

仮想ページ番号

実記憶装置

ページフレーム番号

0

1

2

1023

変換

仮想アドレス

実アドレス

図 4.6 ページング方式

## ページングでの仮想アドレスの生成

IBMメインフレームのアドレッシングモード

例インデックスモード

Rb + Rx + 変位

Rb:ベースレジスタ(汎用レジスタ使用)

Rx:インデックスレジスタ(同上)

OP Rd Rb Rx D

8 4 4 4 12

図 4.7 セグメンテーション方式

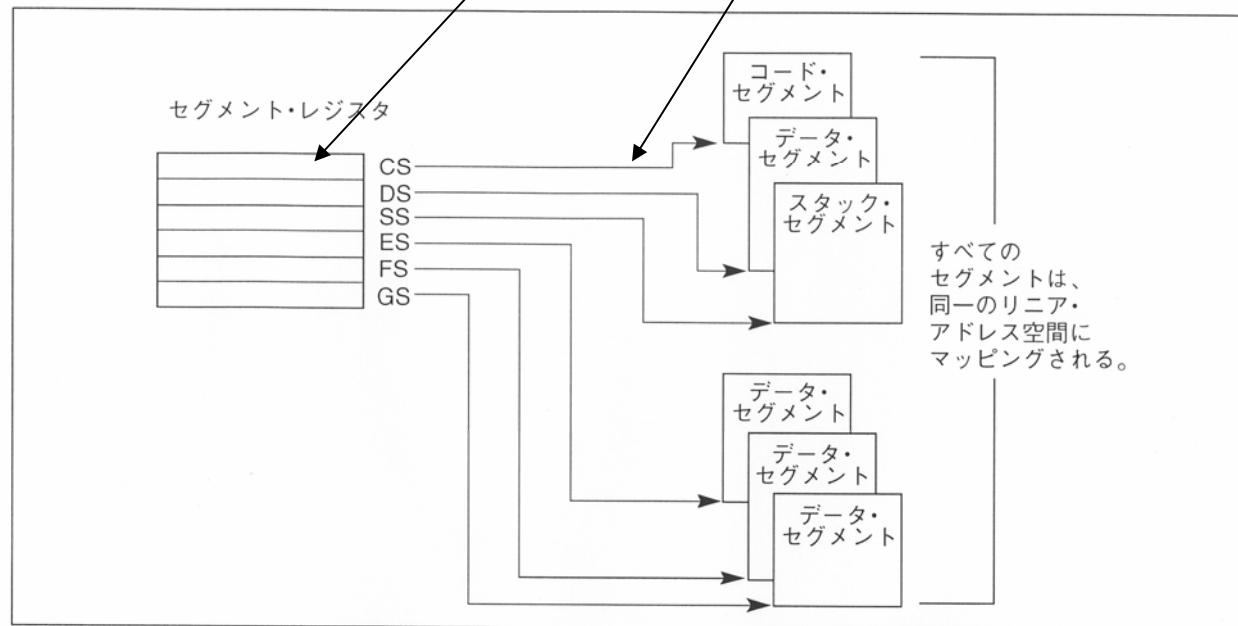

# Pentiumでのセグメンテーション セングメントの種類

コード、データ、スタック、．．．

セグメントレジスタ:セグメントセレクタを格納

CS:コード

SS:スタック

DS:データ

ES,FS,GS:予備

intel®

ここにセグメント番号(セレクタ)を入れておく

セグメントベースへの変換が必要

IA-32 基本実行環境

図 3-6. セグメント化メモリ・モデルでのセグメント・レジスタの使用法

各命令のオペランドごとに対象となるセグメントレジスタが暗黙に決まっている。

そのセグメント内でアドレッシングモードを適用

(a) ページテーブル

図 4.8 直接写像方式

(b) 多重レベル (階層) ページング

16

16

BA

セグメントテーブル

0

⋮

⋮

SN

V セグメントベース実アドレス

SBRA

実アドレス

4M

セグメントごとの

アクセス制御も

可能。R,R/W

(c) セグメンテーション方式

図 4.8 直接写像方式 (つづき)

図 4.9 セグメンテーション方式へのページング機構の導入

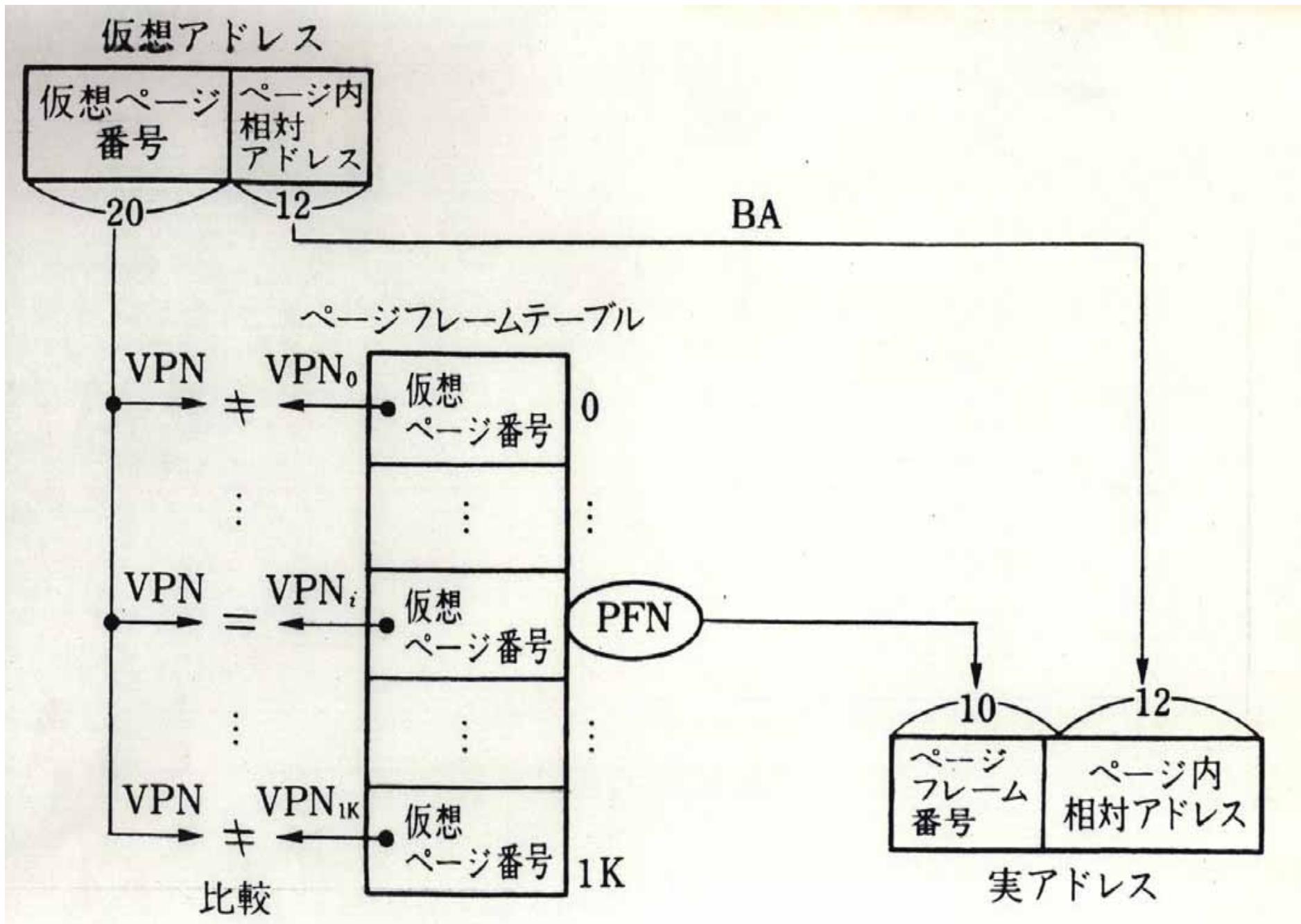

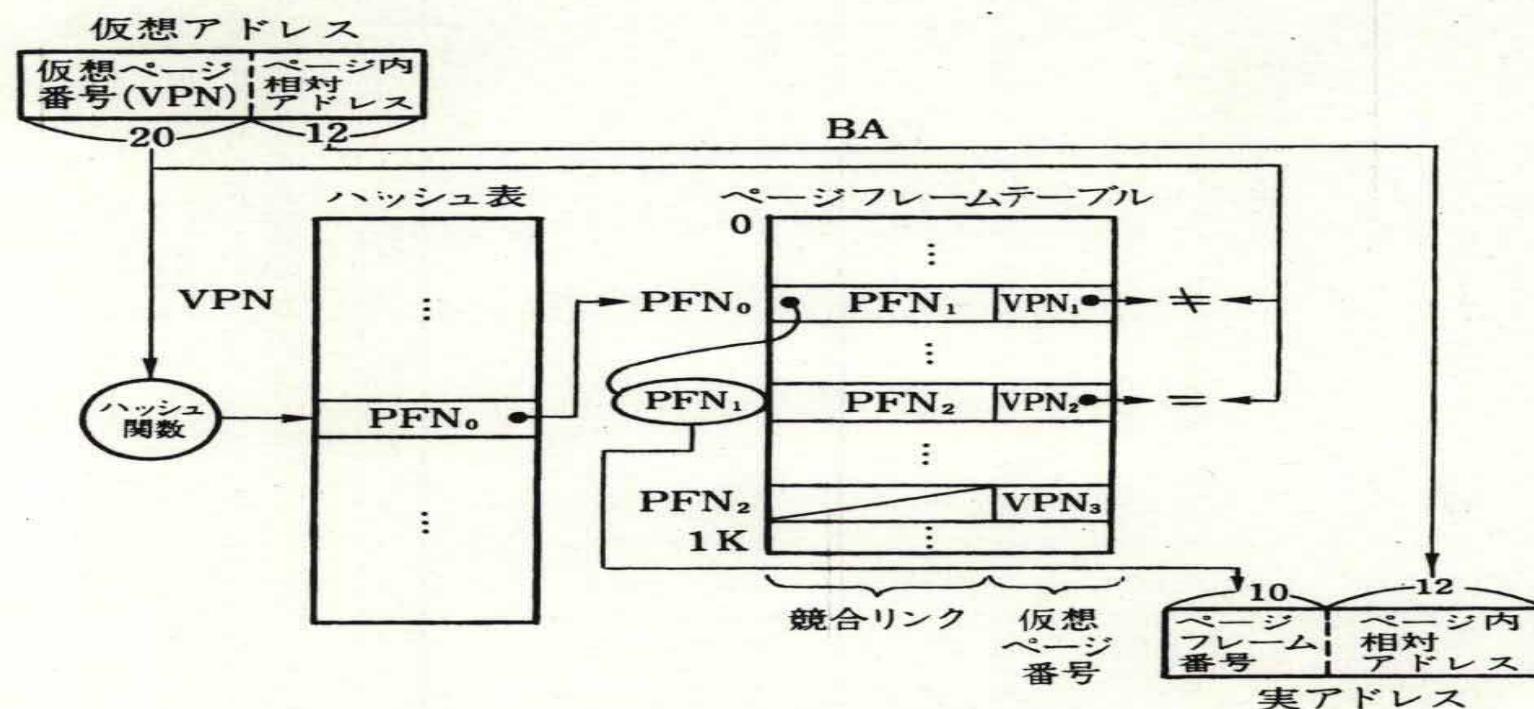

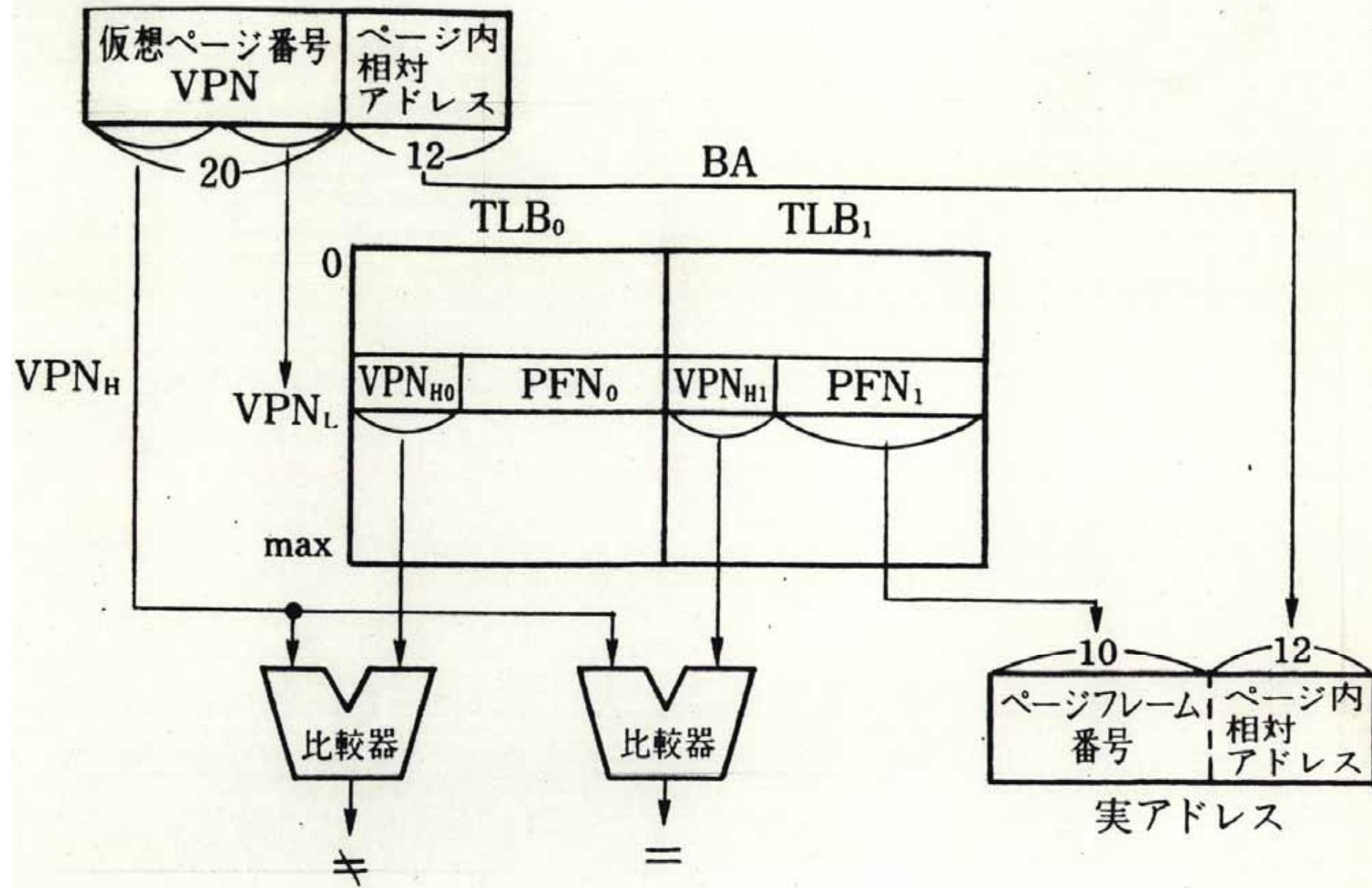

## (2)連想写像

ページフレームテーブル

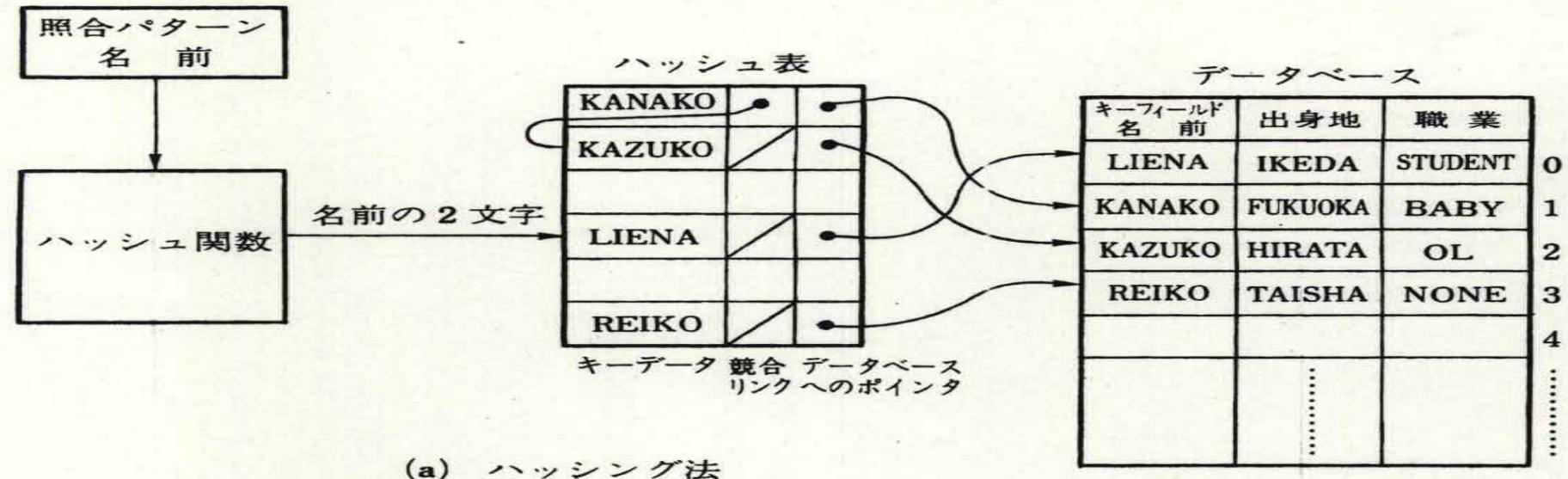

ハッシュ法

TLB法

TLBミスの対処

ハードまたはソフト

図 4.9 連想写像方式

図 4.10 ハッシングを用いた連想写像

図 4.11 TLB の構成

# 実際のアドレス空間の大きさ

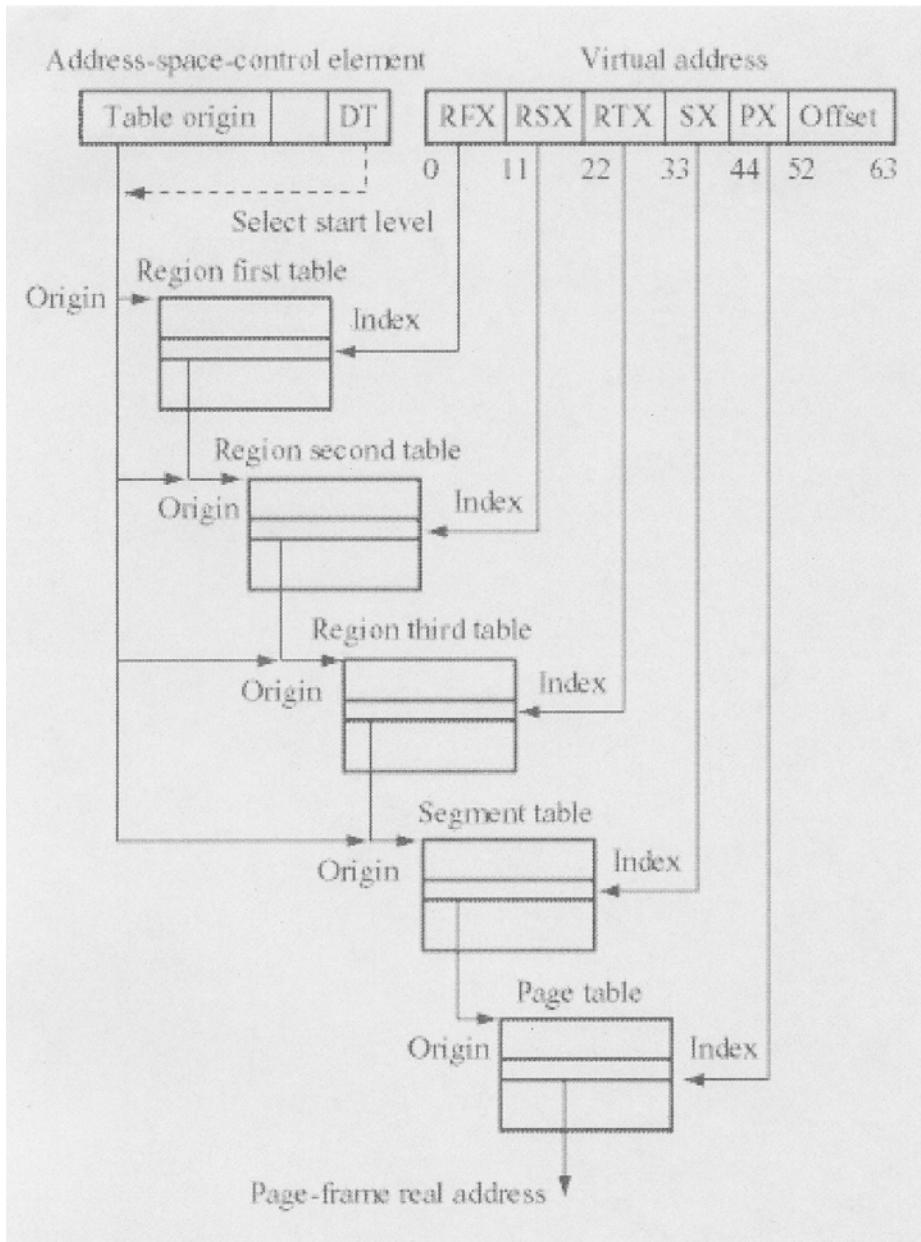

## IBMメインフレーム

1964年 S360 24ビット

1970年 S370 24ビット、仮想記憶の導入

1983年 S370-XA 31ビット

1988年 ESA/370 (Enterprise Systems

Architecture)

1990年 ESA/390

2000年 z/Architecture 64ビット

Figure 6

z/Architecture dynamic address translation.

# z/Architectureでの ページテーブル ページテーブル ウォーク

K.E.Plambeck: Development

and Attributes of

z/Architecture, IBM J.Res

Dev, 46, 4/5, 2002

Intel

マイクロプロセッサ

最大実アドレス容量

|      |             |      |       |                    |

|------|-------------|------|-------|--------------------|

| 1978 | 8086        | 1MB  | 16ビット | セグメント長最大64kB       |

| 1982 | 286         | 16MB |       |                    |

| 1985 | 386         | 4GB  | 32ビット | セグメント長最大4GB        |

| 1989 | 486         | 4GB  |       | セグメント数:16383       |

| 1993 | Pentium     | 4GB  |       |                    |

| 1995 | Pentium Pro | 64GB |       | 仮想アドレス空間           |

| 1997 | Pentium II  | 64GB |       | 14ビット:セグメント番号指定    |

| 1999 | Pentium III | 64GB |       | 32ビット:セグメント内アドレス指定 |

| 2000 | Pentium 4   | 64GB |       | 計46ビット             |

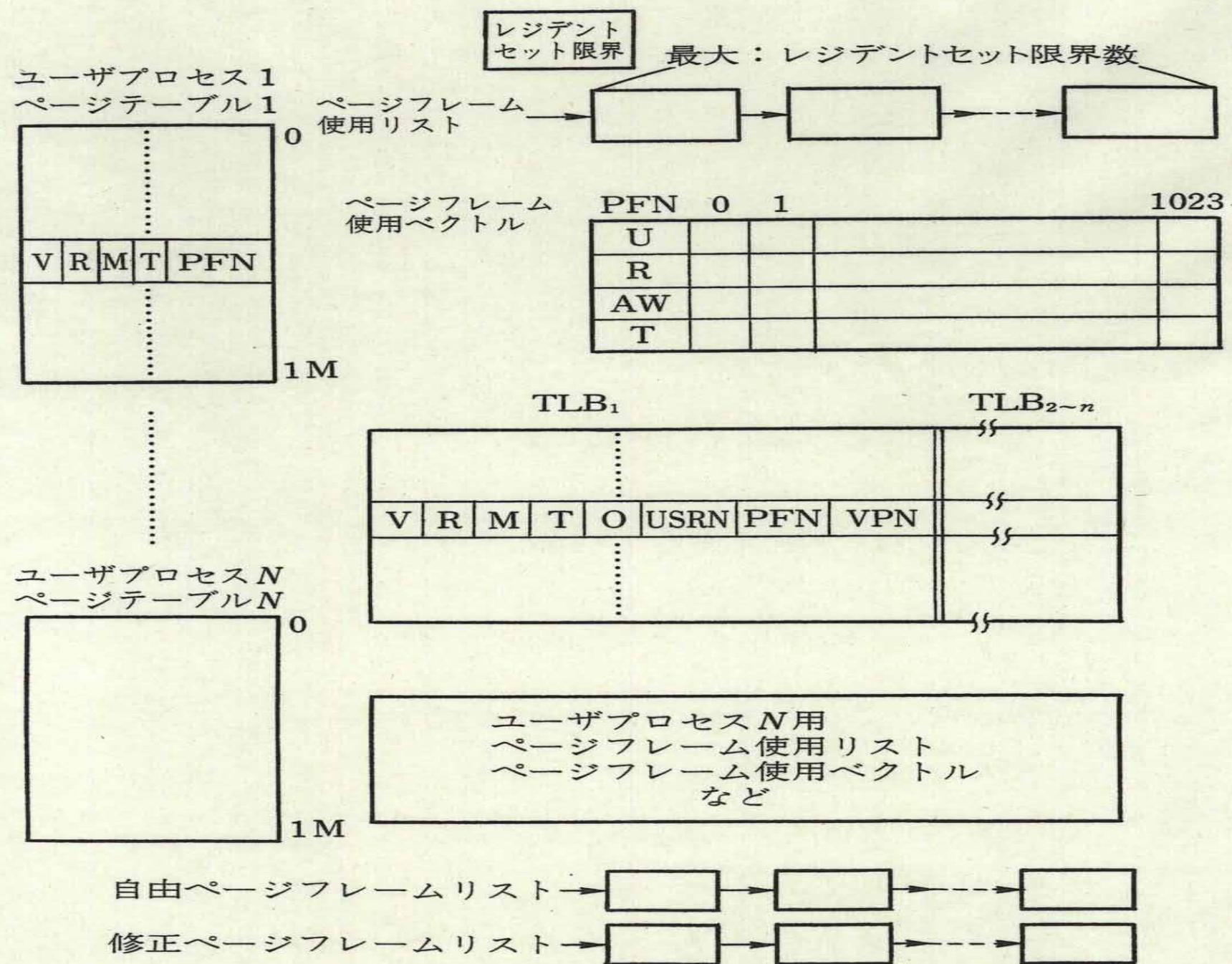

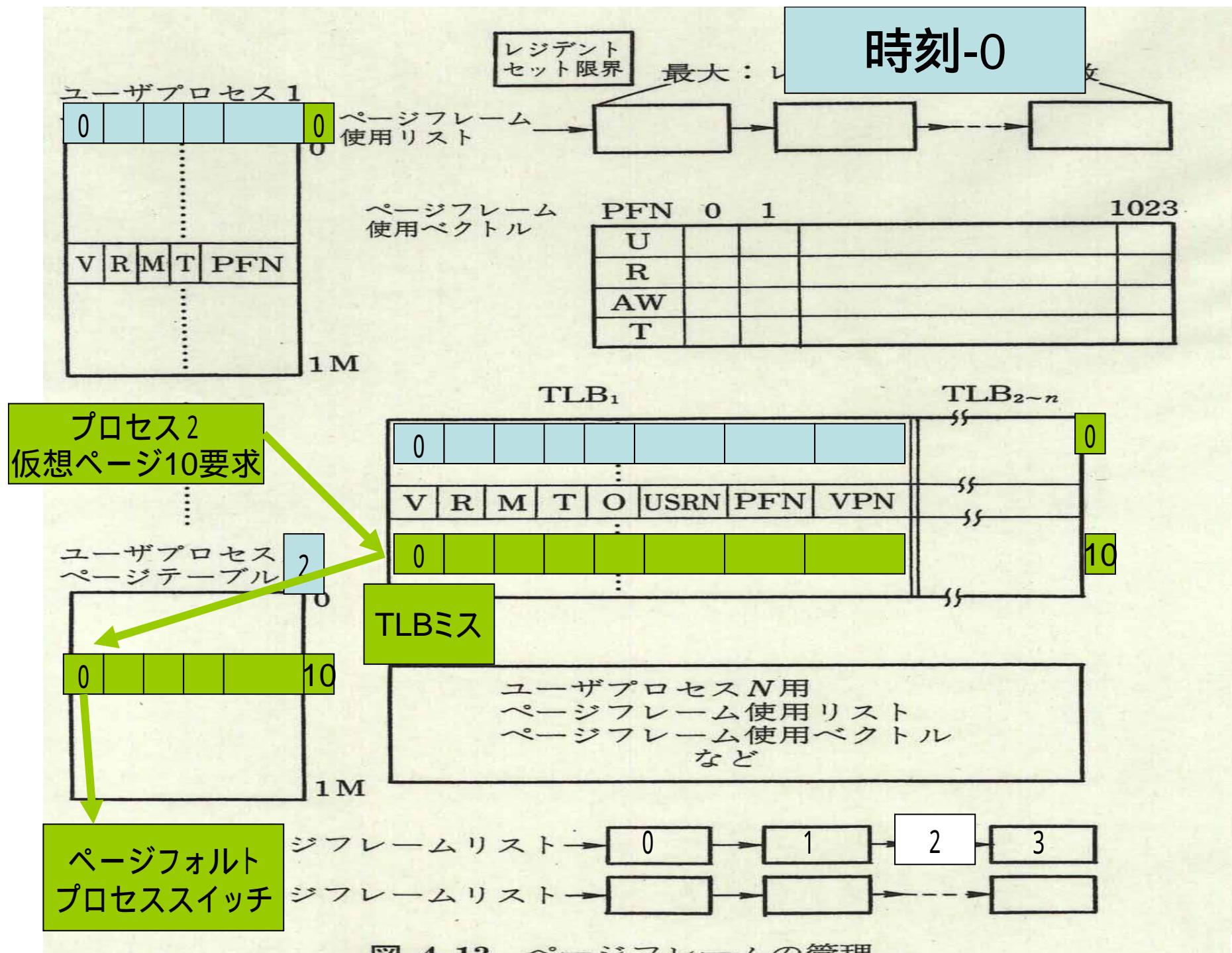

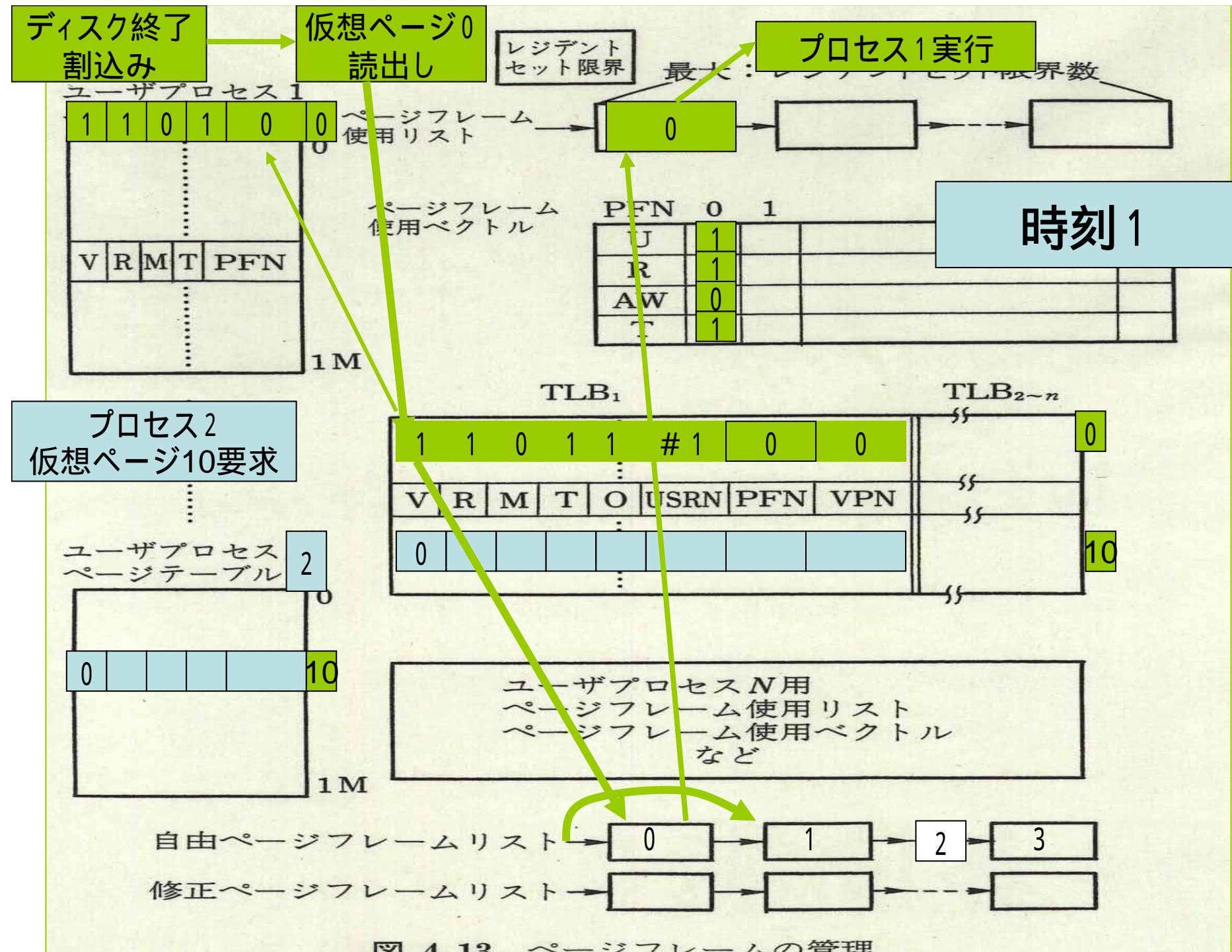

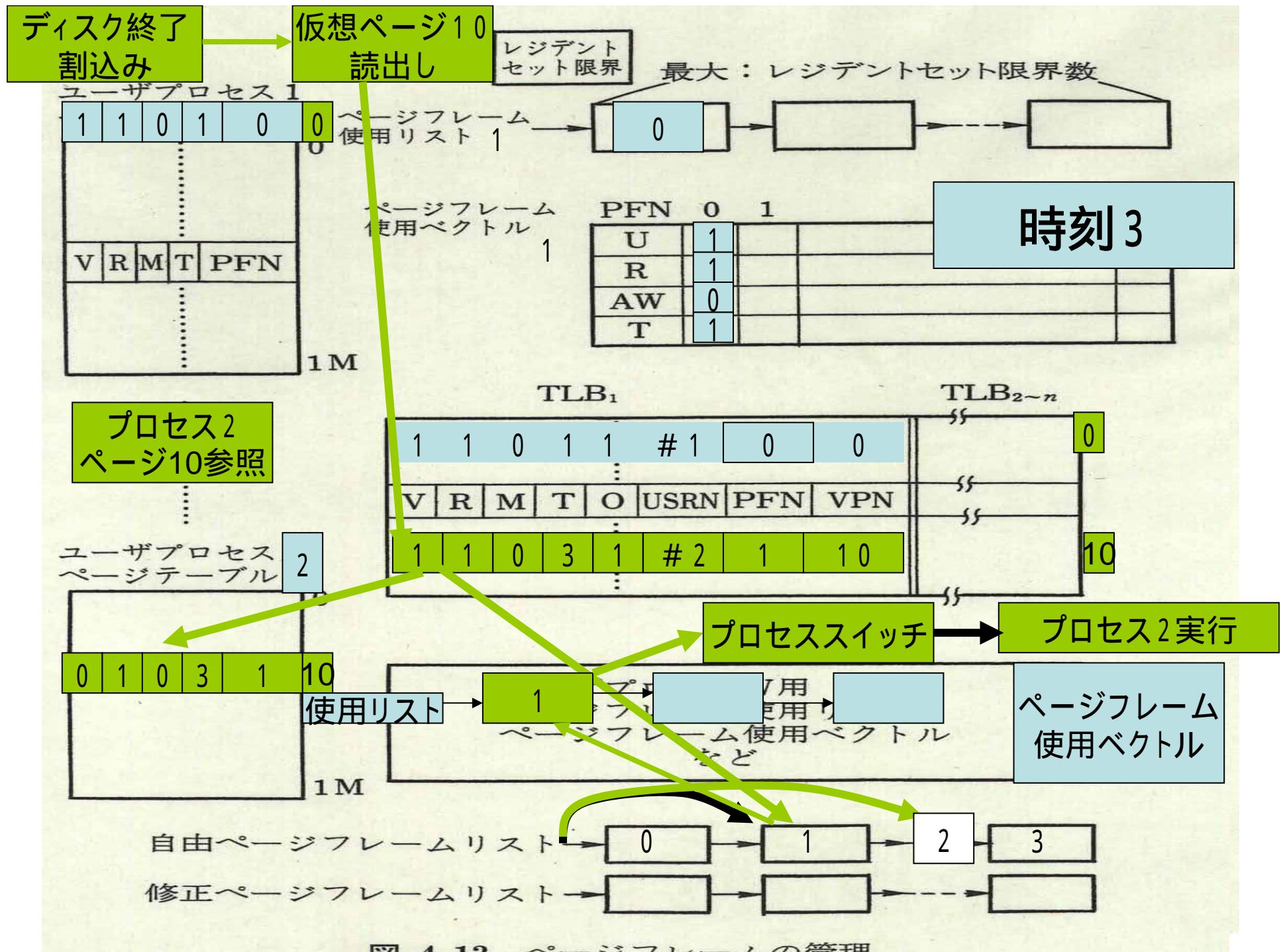

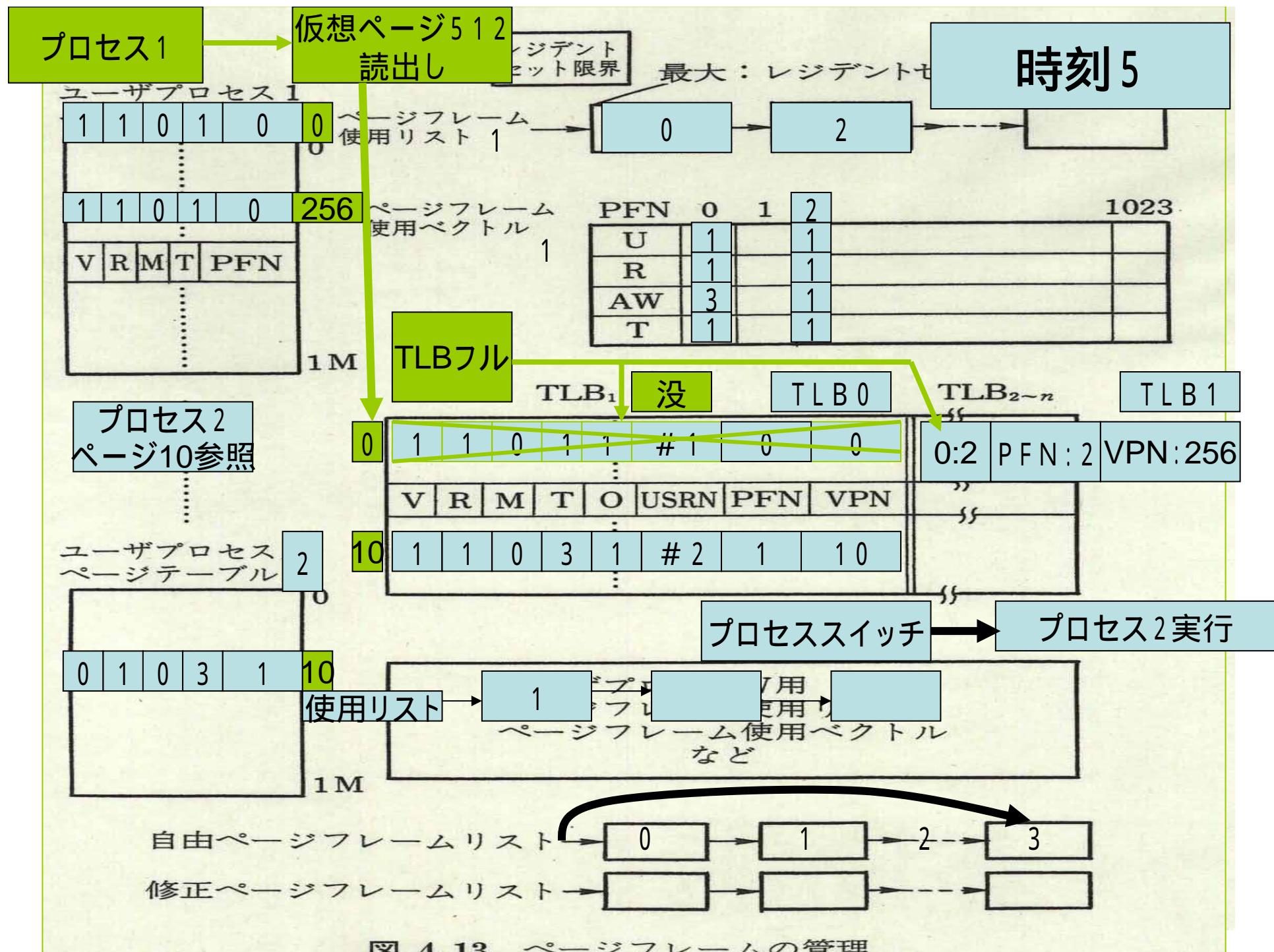

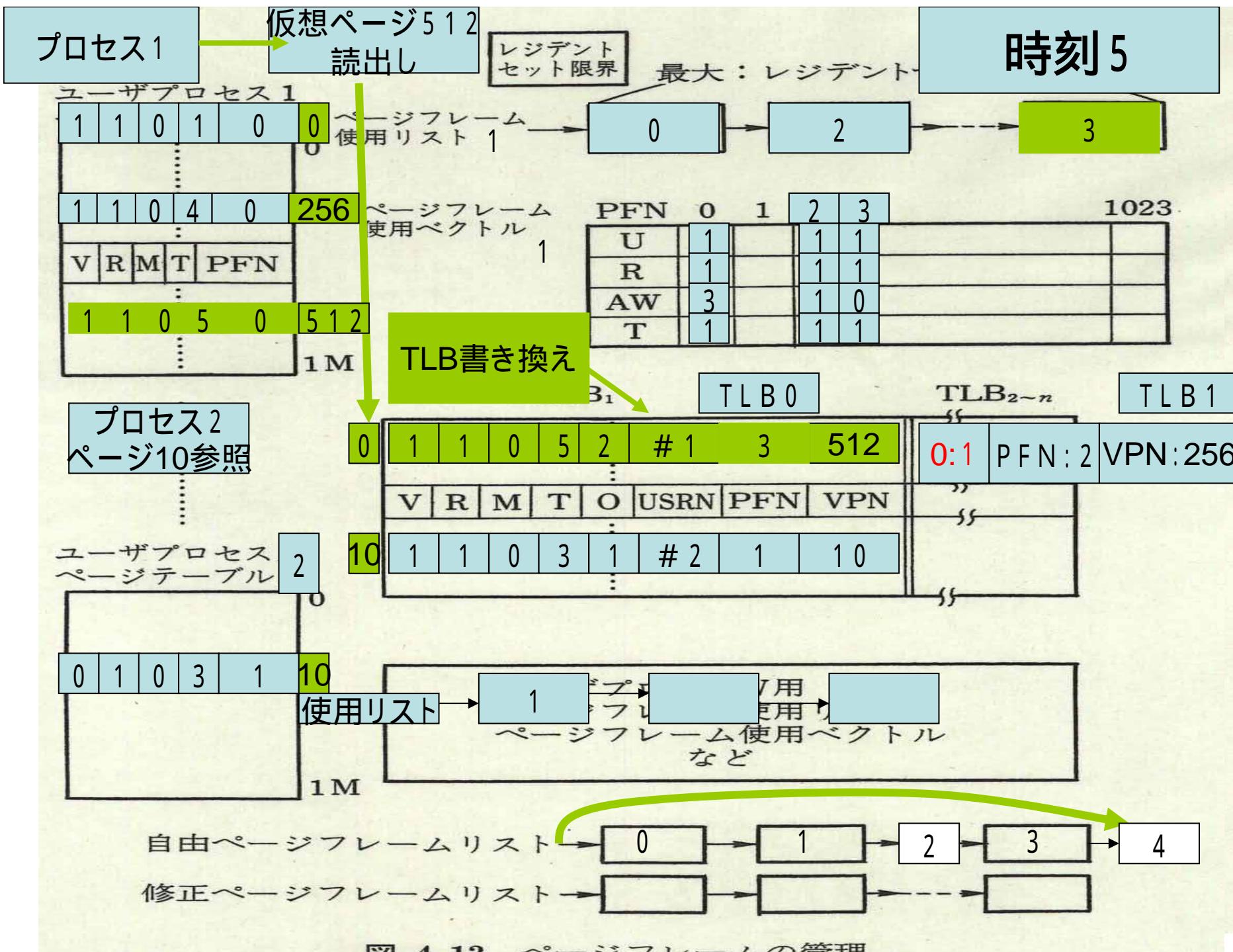

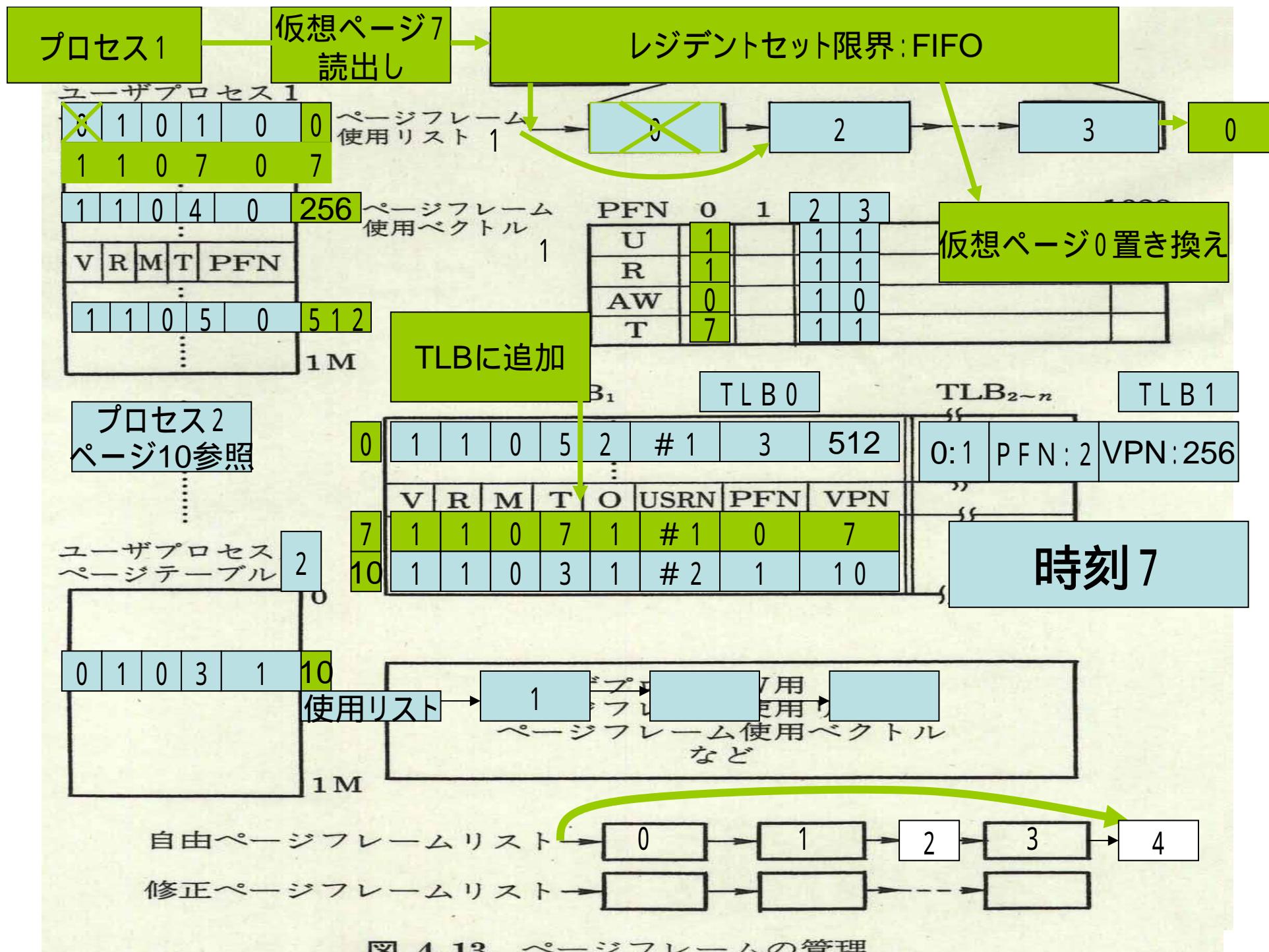

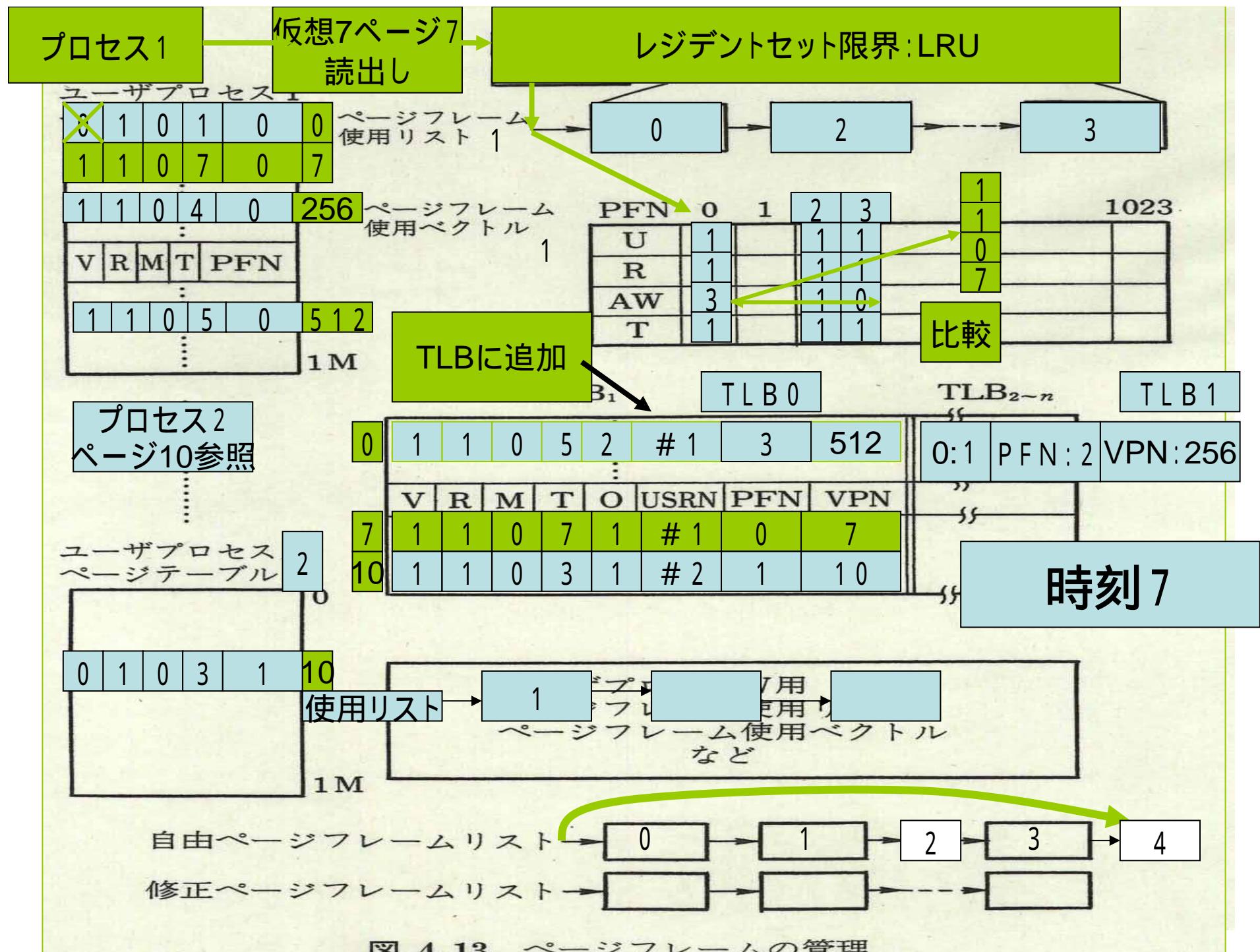

### 4.2.3 ページフレームの管理

(1)各種管理テーブル

(2)ページ置き換えアルゴリズム

FIFO:First In First Out

FINUFO:First In Not Used First Out

LRU:Least Recently Used

ワーキングセット:Working Set

(3)多重プログラミング制御と置き換えアルゴリズム

グローバルLRU法

ワーキングセット法

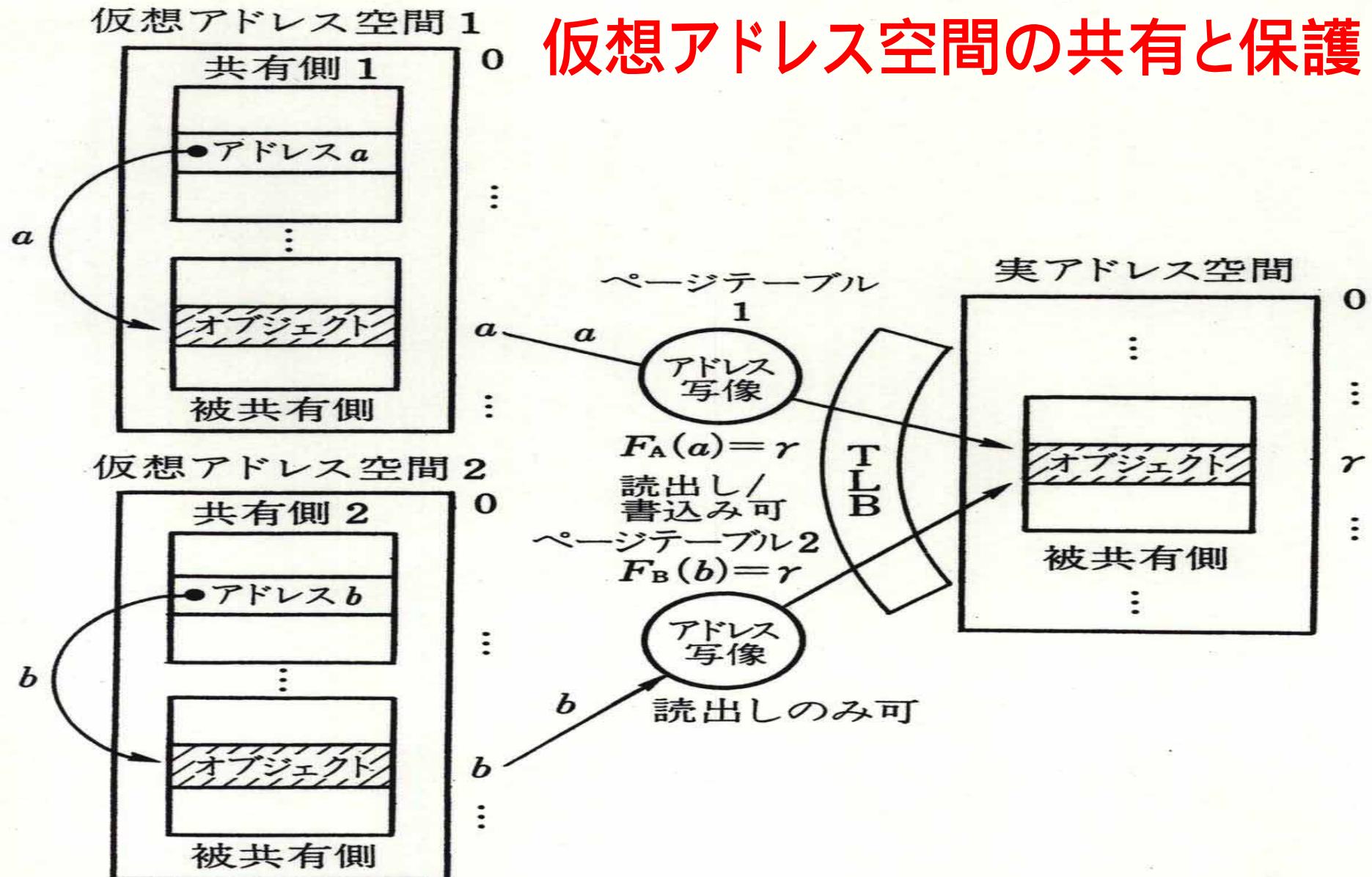

### 4.2.4 仮想空間の共有と保護

多重仮想記憶方式

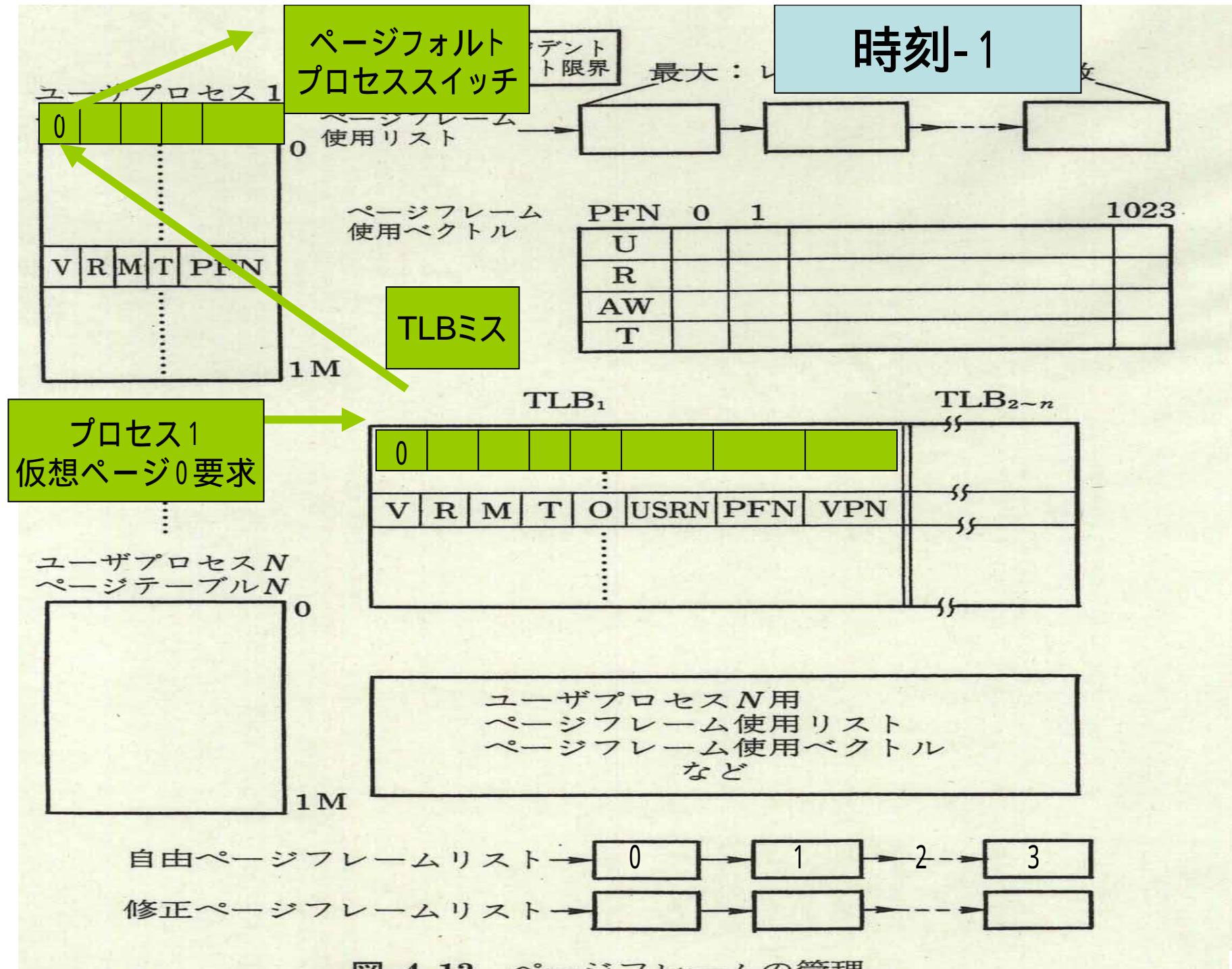

図 4.13 ページフレームの管理

# ページ要求

時刻-1、-0 プロセス0,1 仮想ページ0、仮想ページ10要求

ページフォールト

時刻1 プロセス1 仮想ページ0 ページ枠0

実行中へ

時刻3 プロセス2 仮想ページ10 ページ枠1

プロセススイッチで実行中

時刻4 プロセススイッチでプロセス1へ

仮想ページ256 ページ枠2

時刻5 プロセス1 仮想ページ512 ページ枠3

TLBフル 仮想ページ0 TLB追い出し

時刻7 プロセス1 仮想ページ7 レジデントセット限界

仮想ページ0に対応したページ枠0を置き換えて

仮想ページ7に割り付け

図 4.13 ページフレームの管理

図 4.13 ページフレームの管理

図 4.13 ページフレームの管理

# ページ置換えアルゴリズム:FIFO

|        |                                         | 時刻        | 1              | 2              | 3              | 4              | 5              | 6              | 7              | 8              | 9              | 10             | 11             | 12             |

|--------|-----------------------------------------|-----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|        |                                         | 参照仮想ページ番号 | 1              | 2              | 3              | 4              | 1              | 2              | 5              | 1              | 2              | 3              | 4              | 5              |

| 主記憶の内容 | レジデントセット<br>限界 = 3 の場合<br>ページフォールト: 9回  |           | 1 <sup>†</sup> | 2 <sup>†</sup> | 3 <sup>†</sup> | 4 <sup>†</sup> | 1 <sup>†</sup> | 2 <sup>†</sup> | 5 <sup>†</sup> | 5              | 5              | 3 <sup>†</sup> | 4 <sup>†</sup> | 4              |

|        |                                         |           | 1              | 2              | 3              | 4              | 1              | 2              | 2              | 2              | 5              | 3              | 3              |                |

| 主記憶の内容 | レジデントセット<br>限界 = 4 の場合<br>ページフォールト: 10回 |           | 1 <sup>†</sup> | 2 <sup>†</sup> | 3 <sup>†</sup> | 4 <sup>†</sup> | 4              | 4              | 5 <sup>†</sup> | 1 <sup>†</sup> | 2 <sup>†</sup> | 3 <sup>†</sup> | 4 <sup>†</sup> | 5 <sup>†</sup> |

|        |                                         |           | 1              | 2              | 3              | 3              | 3              | 4              | 5              | 1              | 2              | 3              | 4              |                |

† : ページフォールト

図 4.13 FIFO 方式における異常現象

[マドニック, ドノバン (池田克夫訳) : オペレーティングシステム, 日本コンピュータ協会 (1976)]

# ページ置換えアルゴリズム: FINUFO

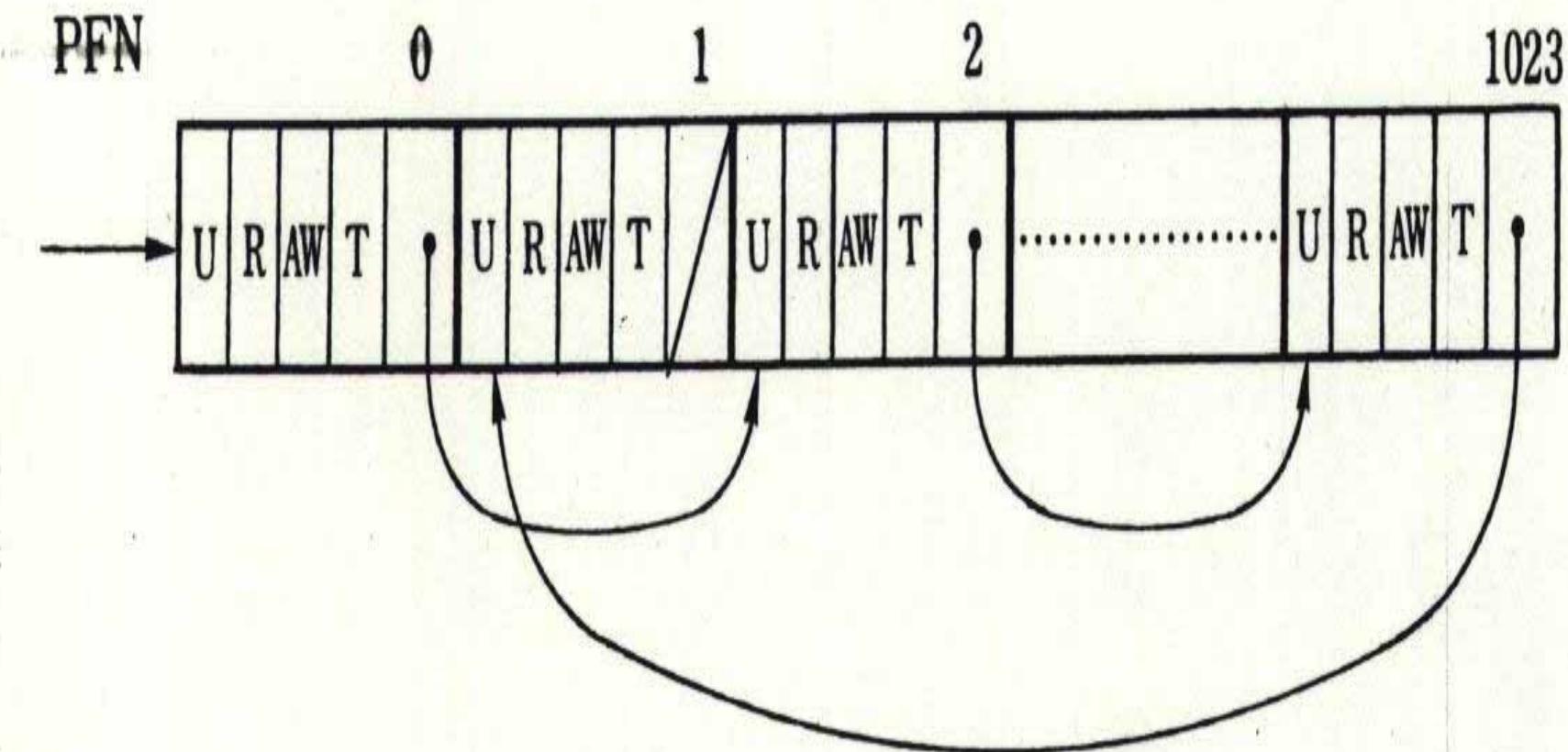

図 4.14 FINUFO のページフレーム使用ベクトル

|         | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8 | 9 | 10 | 11 | 12 |

|---------|----|----|----|----|----|----|----|---|---|----|----|----|

| $P =$   | 4  | 3  | 2  | 1  | 4  | 3  | 5  | 4 | 3 | 2  | 1  | 5  |

| $M = 3$ | 4+ | 3+ | 2+ | 1+ | 4+ | 3+ | 5+ | 4 | 3 | 2+ | 1+ | 5+ |

| $F =$   | +  | +  | +  | +  | +  | +  | +  |   |   | +  | +  | +  |

包含関係

(a)  $M = 3$

$$F = 10$$

$$f = \frac{10}{12} \approx 83\%$$

|         | 1  | 2  | 3  | 4  | 5 | 6 | 7  | 8 | 9 | 10 | 11 | 12 |

|---------|----|----|----|----|---|---|----|---|---|----|----|----|

| $P =$   | 4  | 3  | 2  | 1  | 4 | 3 | 5  | 4 | 3 | 2  | 1  | 5  |

| $M = 4$ | 4+ | 3+ | 2+ | 1+ | 4 | 3 | 5+ | 4 | 3 | 2+ | 1+ | 5+ |

| $F =$   | +  | +  | +  | +  |   |   | +  |   |   | +  | +  | +  |

(b)  $M = 4$

$$F = 8$$

$$f = \frac{8}{12} \approx 67\%$$

図 3.29 LRU 置換えアルゴリズムの例

ドノバン

### 3.6 デマンド・ページングによる記憶管理

包含関係の正式な証明は多少長たらしいので本書では示さない。証明の手がかりは、 $M(P, c, t)$  の値をどのようにして決定するかを考えることにより得られる。たとえば、 $M(P, 3, 7)$  を決定するには 7 番目のページ参照——ページ 5——から開始して、ページの軌跡を逆にたどり、最初に出てきたページ番号を 3 つ求めればよい。 $M(P, 3, 7)$  は 5, 3, 4 である。 $M(P, 4, 7)$  はページ番号を 4 つ求めればよい。このとき同じページ番号が現われても 2 回含めないことにする。その例は  $M(P, 4, 9)$  で説明される：

$$\begin{aligned} t &= 9 \ 8 \ 7 \ 6 \ 5 \ 4 \\ P(t) &= 3 \ 4 \ 5 \ 3 \ 4 \ 1 \end{aligned}$$

したがって、 $M(P, 4, 9) = 3, 4, 5, 1$  である。時刻 6 および 5 のページ番号 3 および 4 はすでに求められているので捨てられる。 $M(P, c, t)$  を求めるには、 $t$  番目のページ参照から始めページ軌跡を逆にたどり、最効に出てくる  $c$  個のページ番号を求める。 $M(P, c+1, t)$  を求めるには、最初に出てくる  $c+1$  個のページ番号を求める。この定義より、 $M(P, c, t) \subset M(P, c+1, t)$  であることは容易に理解されるであろう。すなわち、 $M(P, c, t)$  に含まれるページ番号は、 $M(P, c+1, t)$  に含まれている。この包含関係は、記憶容量を増加してもページ割込みの発生回数を増加させないことを保証する。

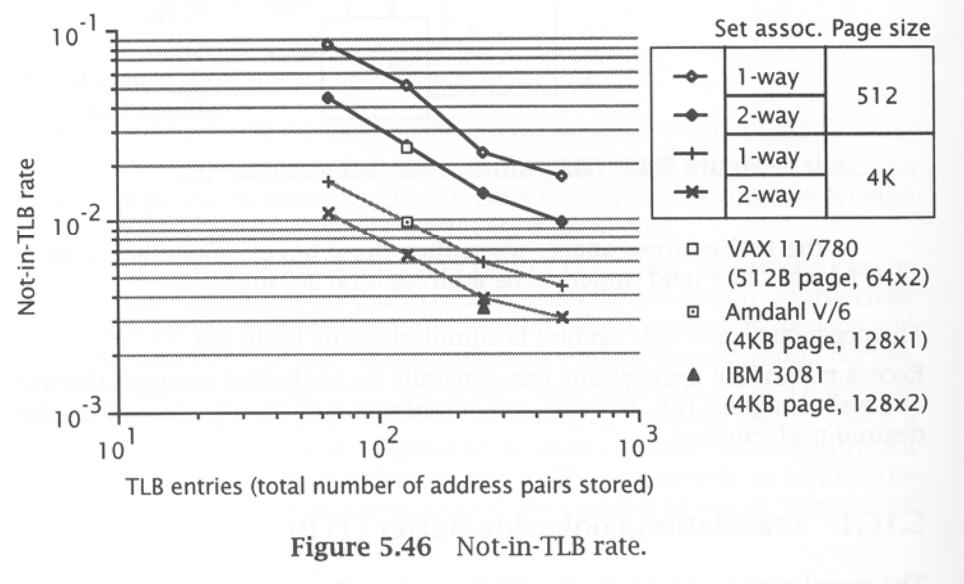

# TLB Miss と ページウォーク

ペナルティ: 15 - 30 サイクル

| For S/370 and 4 <sup>KB</sup> Pages: |                  |         |                 |

|--------------------------------------|------------------|---------|-----------------|

| Machine                              | TLB Organization | Entries | Not-in-TLB rate |

| Amdahl V/6                           | 128 × 2          | 256     | 0.3-0.4%        |

| Amdahl V/8                           | 256 × 2          | 512     | (not available) |

| IBM 3081                             | 128 × 1          | 128     | 1%              |

| IBM 3033                             | 64 × 2           | 128     | (not available) |

| For VAX and 512 <sup>B</sup> Pages: |                  |         |                 |

|-------------------------------------|------------------|---------|-----------------|

| Machine                             | TLB Organization | Entries | Not-in-TLB rate |

| VAX 11/780                          | 64 × 2           | 128     | 4.5%            |

M.J.Flynn:Computer

Architecture, Jones

& Bartlett, 1995

# 仮想アドレス空間の共有と保護

図 4.16 仮想アドレス空間の共有と保護

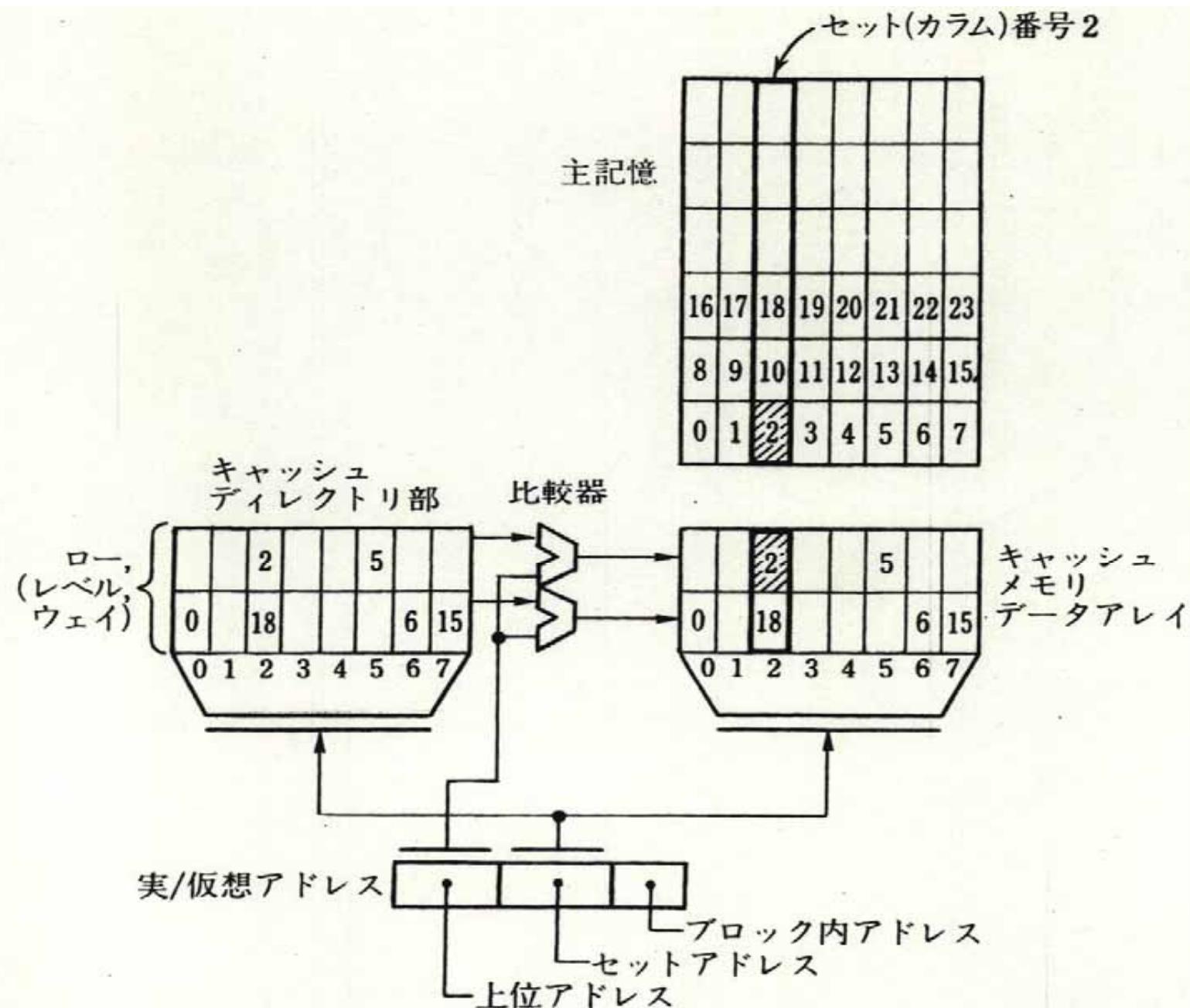

## 4.3 キャッシュ・メモリ

### 4.3.1 基本原理

参照の局所性を利用

on demand

メモリとの写像

ブロック単位で写像: 空間局所性、64B程度

セットアソシアティブ方式

セット分割

セット数1: フルアソシアティブ方式

ロード

ロード1: ダイレクトマッピング(旧プロセッサ)

図 4.16 セットアソシアティブ方式

キャッシュメモリの容量

ブロックサイズ \* セット数 \* ロード数

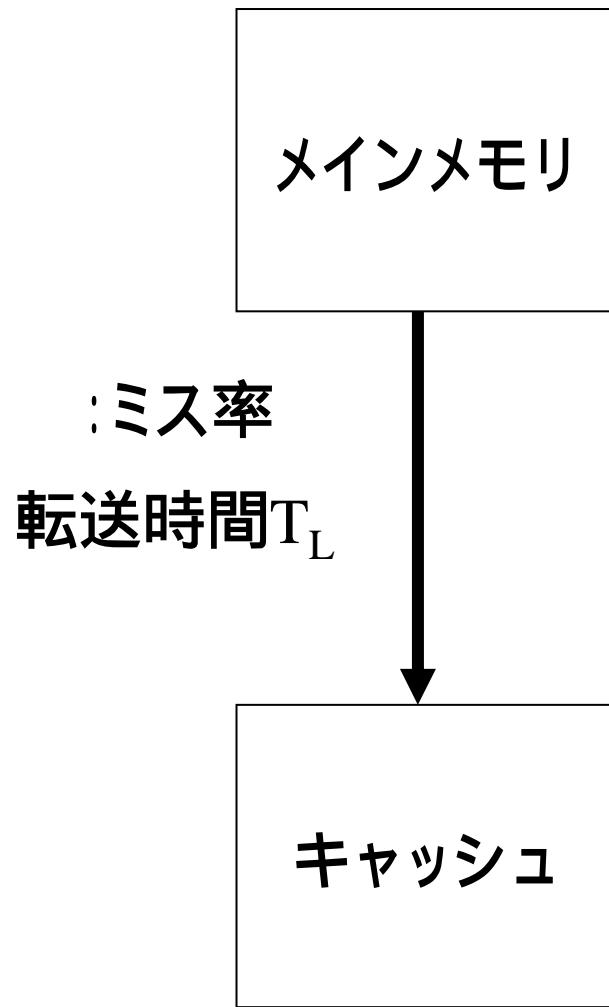

キャッシュメモリの実効アクセス時間

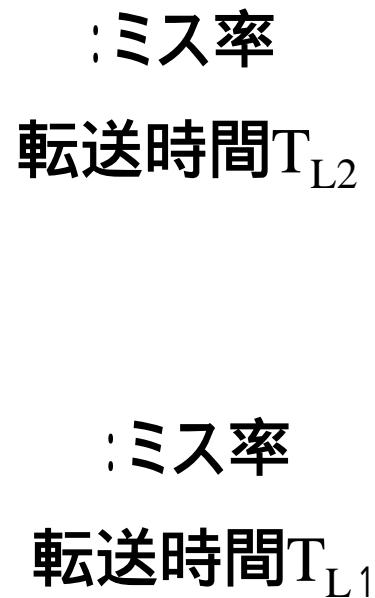

$$T_C = T_H (1 - \text{ミス率}) + (T_H + T_{L1}) = T_H + T_{L1}$$

:ミス率、 $T_{L1}$ :メモリからの転送時間

容量大 小、 $T_H$ 増大

容量: 64 kB程度

ブロックサイズ: 空間局所性

32~64 B程度

表 4.2 キャッシュミスヒット率の例<sup>9)</sup>(整数系, 浮動小数点系を単純合計)

(a) ロー数 2, ブロックサイズ 64B の場合のミスヒット率

| キャッシュ量 | 命令キャッシュ | データキャッシュ | 統合キャッシュ |

|--------|---------|----------|---------|

| 2 KB   | 0.0115  | 0.1708   | 0.0697  |

| 4 KB   | 0.0082  | 0.1400   | 0.0517  |

| 8 KB   | 0.0054  | 0.0942   | 0.0342  |

| 16 KB  | 0.0032  | 0.0454   | 0.0173  |

| 32 KB  | 0.0022  | 0.0289   | 0.0101  |

| 64 KB  | 0.0009  | 0.0215   | 0.0067  |

| 128 KB | 0.0001  | 0.0164   | 0.0045  |

(b) キャッシュ容量 64 KB, 統合キャッシュの場合のミスヒット率

| ブロックサイズ | ロー数 1  | ロー数 2  | ロー数 4  | ロー数 8  |

|---------|--------|--------|--------|--------|

| 16 B    | 0.0204 | 0.0160 | 0.0150 | 0.0145 |

| 32 B    | 0.0135 | 0.0096 | 0.0089 | 0.0086 |

| 64 B    | 0.0106 | 0.0067 | 0.0059 | 0.0057 |

| 128 B   | 0.0102 | 0.0054 | 0.0047 | 0.0046 |

| 256 B   | 0.0115 | 0.0050 | 0.0042 | 0.0040 |

命令実行数 ( $N_I$ ) : 132,594,094,021, データ参照回数 : 45,165,001,895

### 4.3.2置換えアルゴリズム

各セットでLRU(Least Recently Used)

### 4.3.3実記憶への書き込み

(1)ストアスルー(store through、write through)

書き込み時:メモリにも同時に書き込み

(2)ストアイン(store inまたはwrite back)

書き込み時:メモリにはすぐには書かず、

置換え時に格納

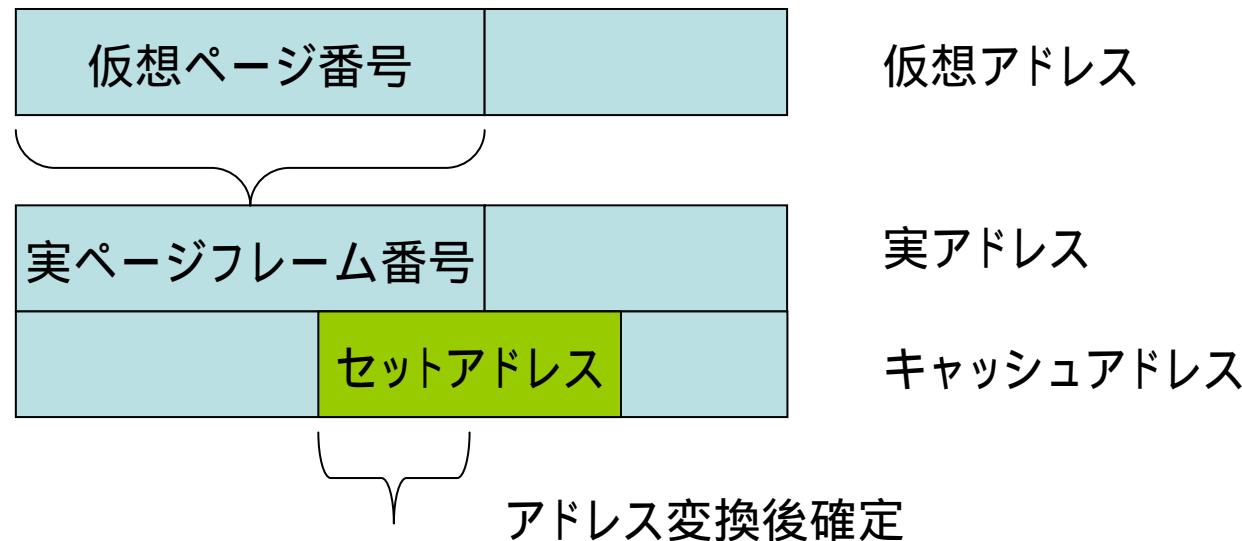

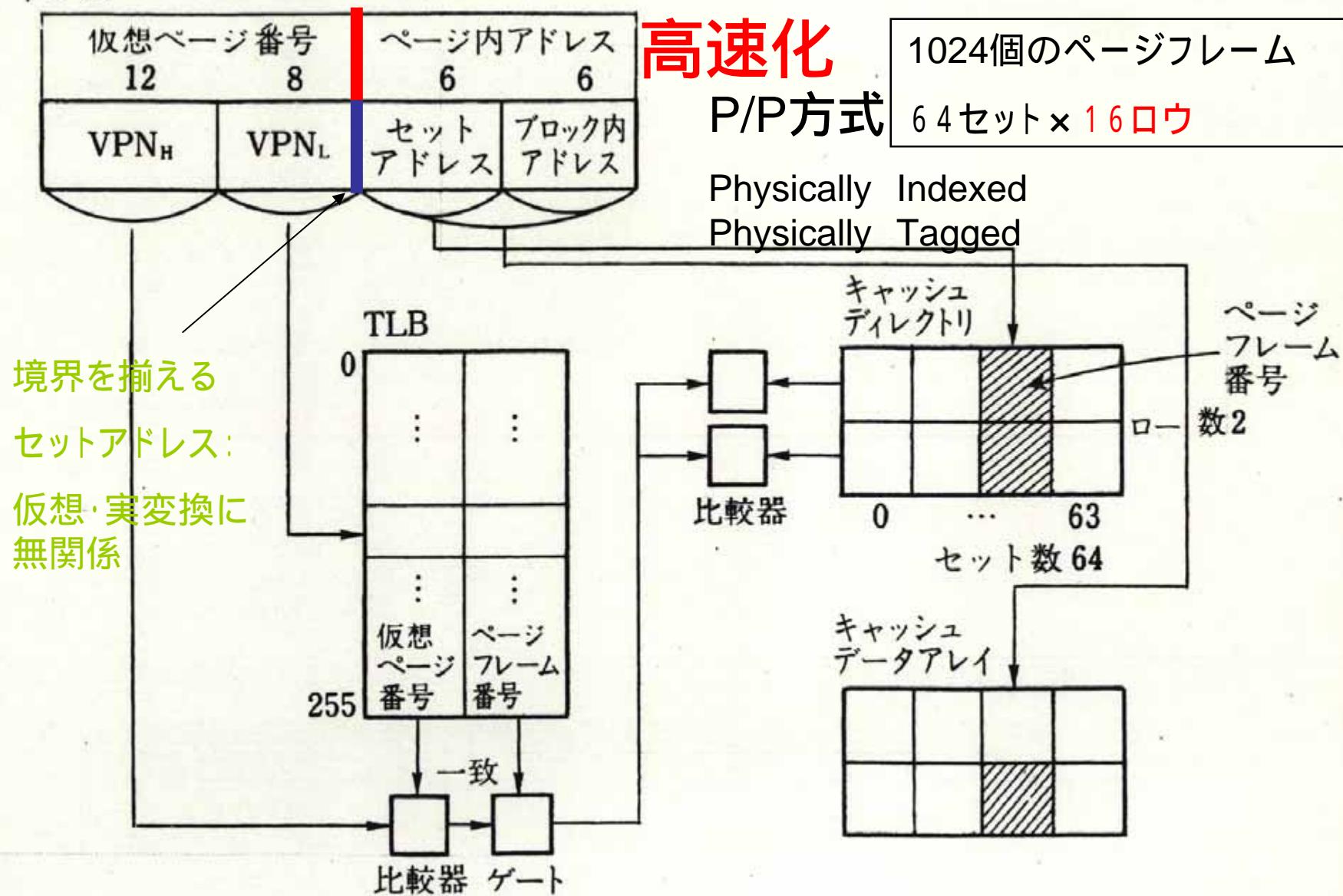

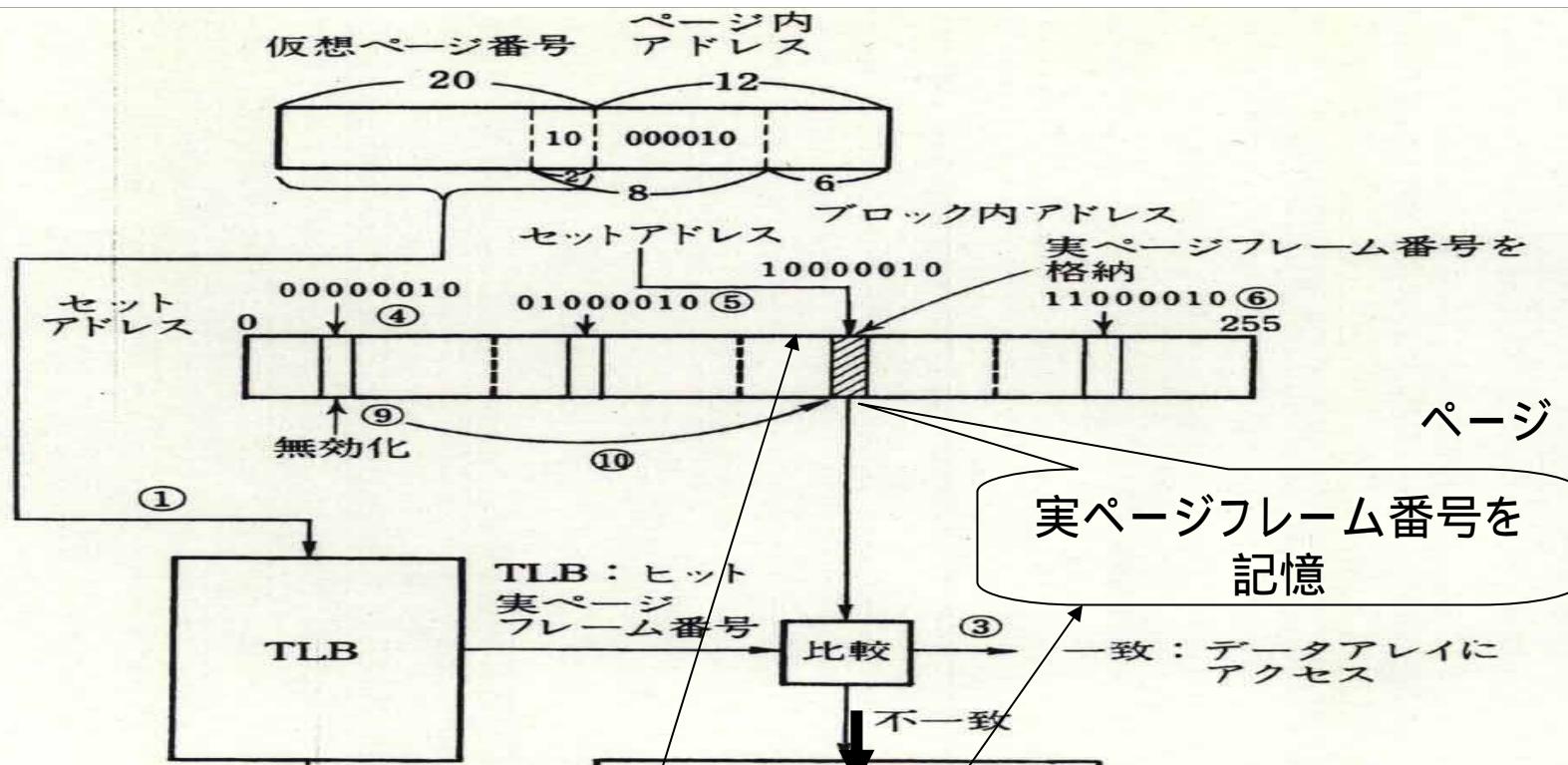

#### 4.3.4 仮想アドレスキャッシュと 実アドレスキャッシュ

- ・キャッシュディレクトリへのアドレスの与え方

仮想アドレス : Virtually Indexed

実アドレス : Physically Indexed

- ・キャッシュディレクトリ内の情報

仮想アドレス(ページ番号) : Virtually Tagged

実アドレス(ページフレーム番号) : Physically Tagged

- ・実アドレスキャッシュ : P/P

- ・仮想アドレスキャッシュ : V/V, V/P

## (1) 実アドレスキャッシュ

仮想アドレス TLB 実アドレス

キャッシュディレクトリ データアレイ

高速化: ページ境界とセット境界同一化

シノニム問題なし

キャッシュコヒーレンス容易

# 実アドレスキャッシュの 高速化

1024個のページフレーム

64セット × 16ロウ

Physically Indexed

Physically Tagged

図 4.18 実アドレスキャッシュの高速化

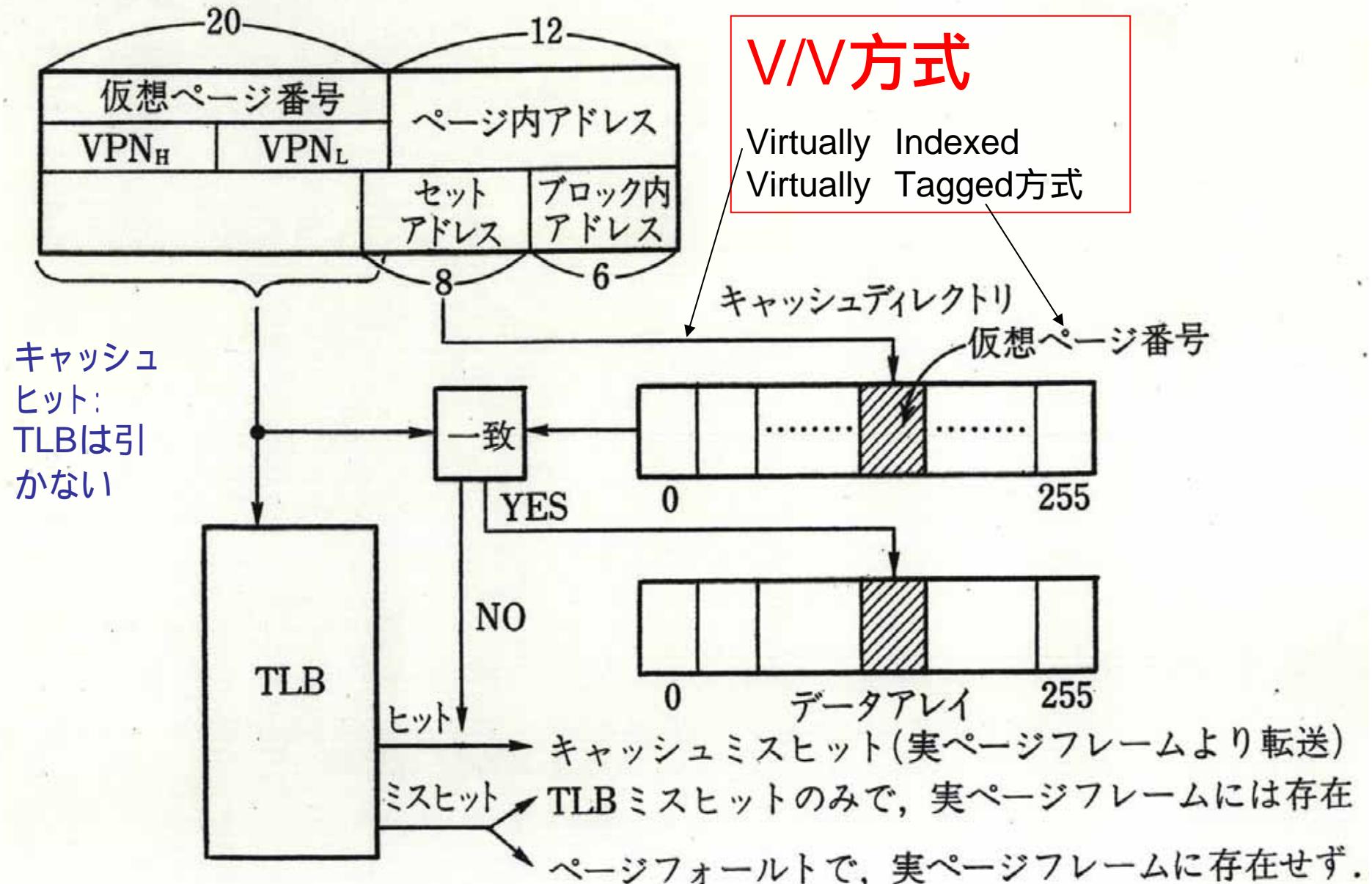

## (2)仮想アドレスキャッシュ(V/V方式)

高速で、

TLBを通常引く必要がない

しかし

シノニム問題が生じる

仮想アドレス

# 仮想アドレスキャッシュ

図 4.19 仮想アドレスキャッシュの構成

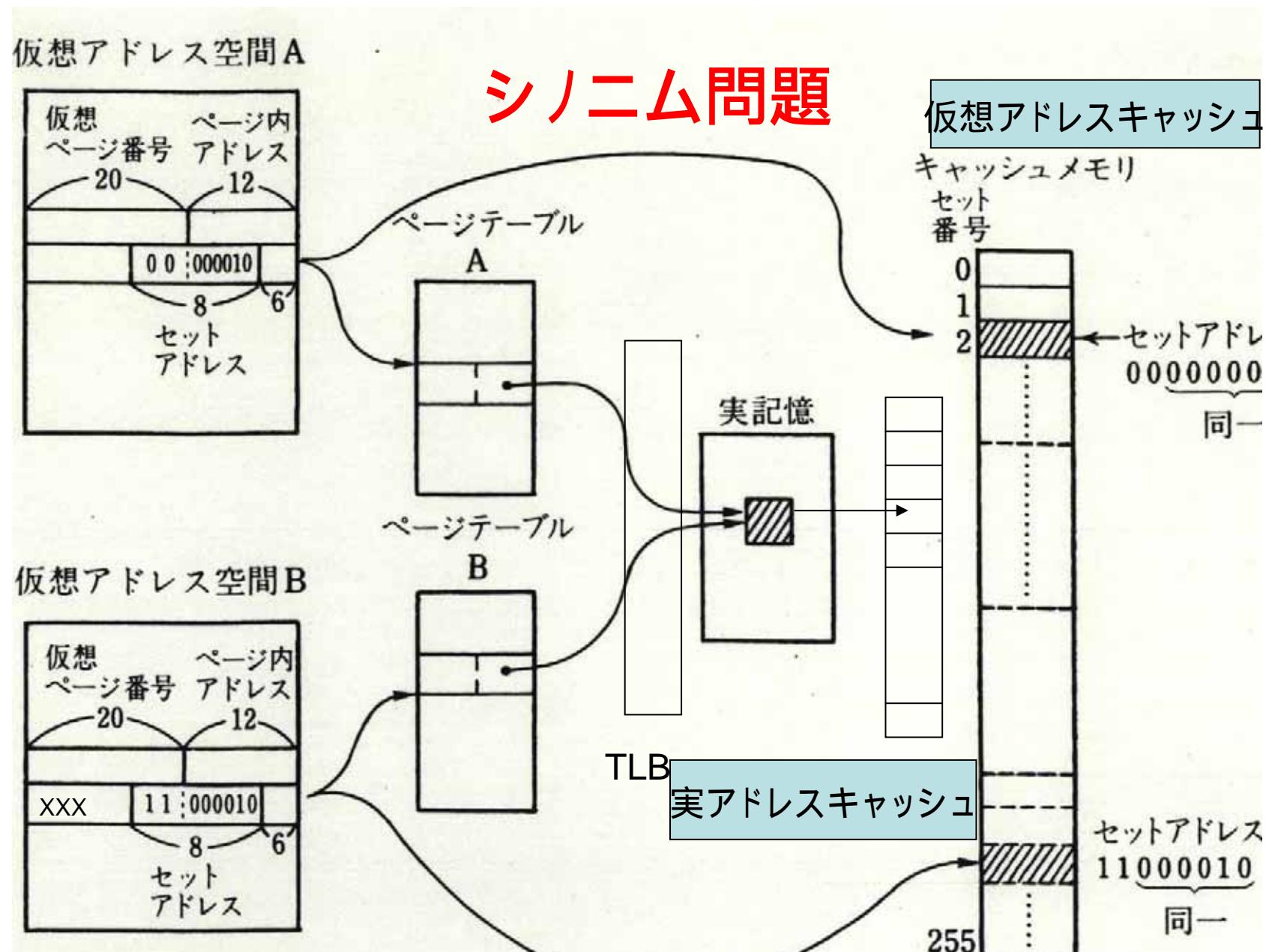

# シノニム問題

図 4.20 シノニムの発生

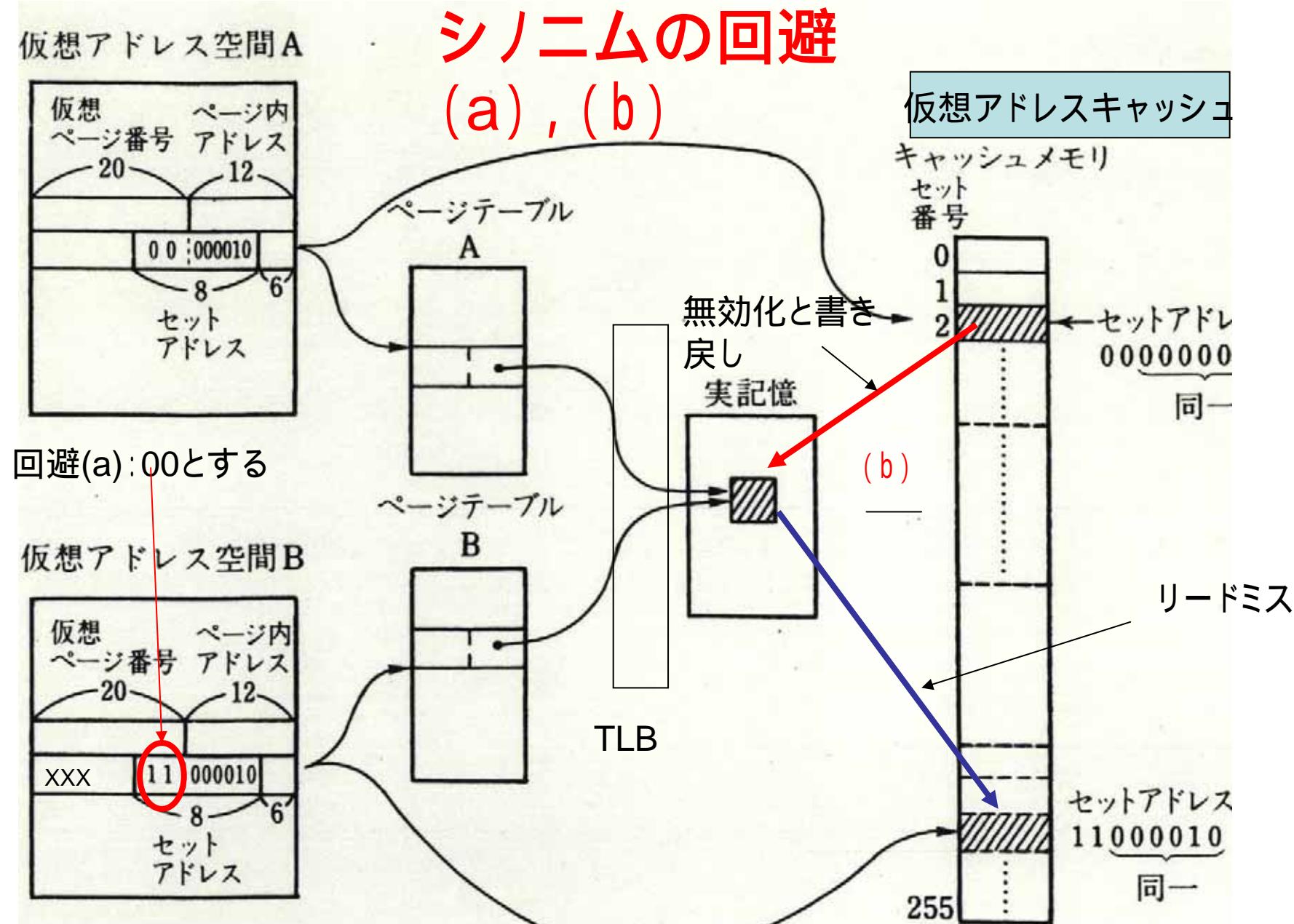

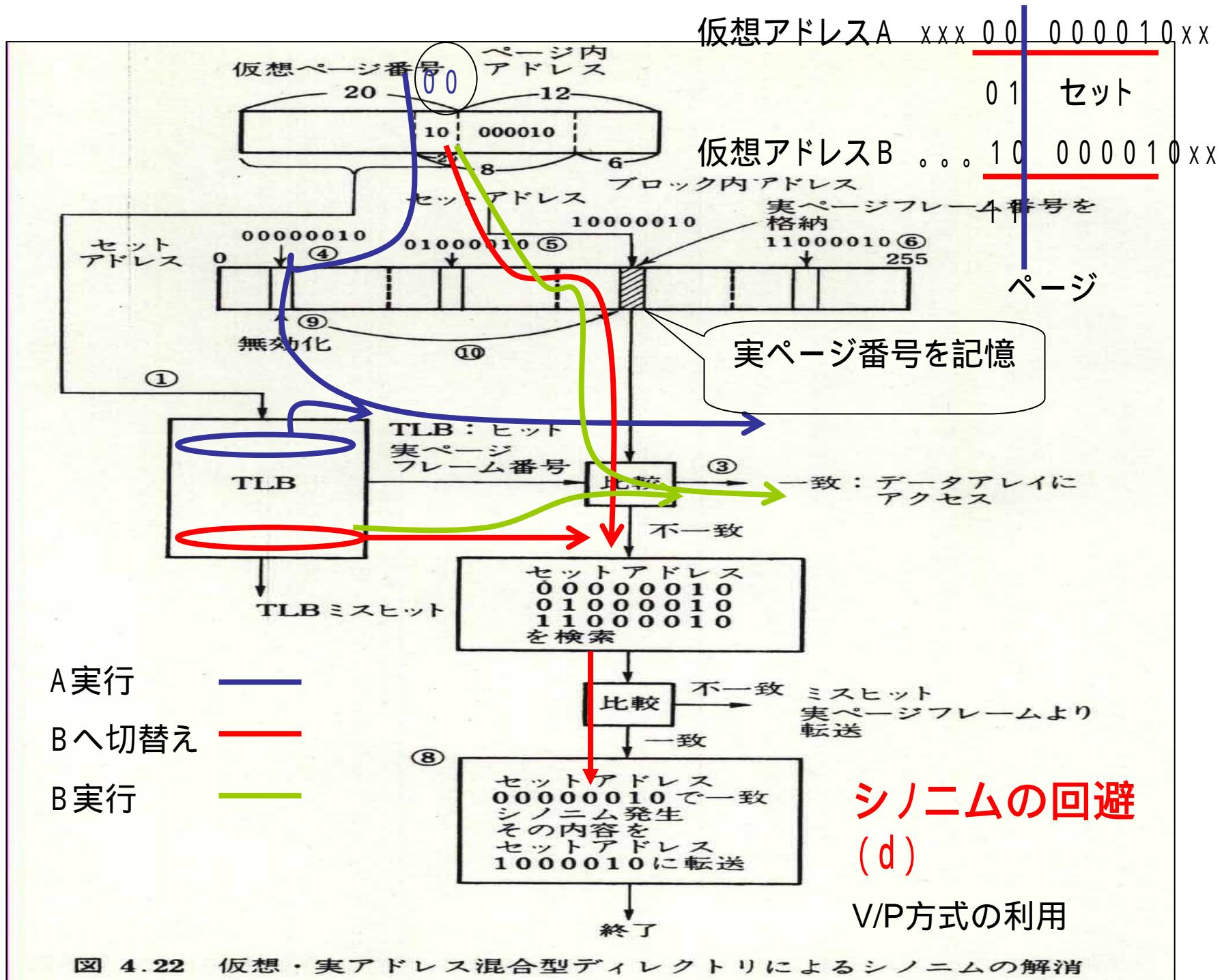

## シノニム問題の回避

### V/V方式

- (a)共有空間を同一仮想アドレスに設定(ソフト的):セットアドレスを含むビット

- (b)全キャッシュページ法

プロセス切り替え時にキャッシュを無効化

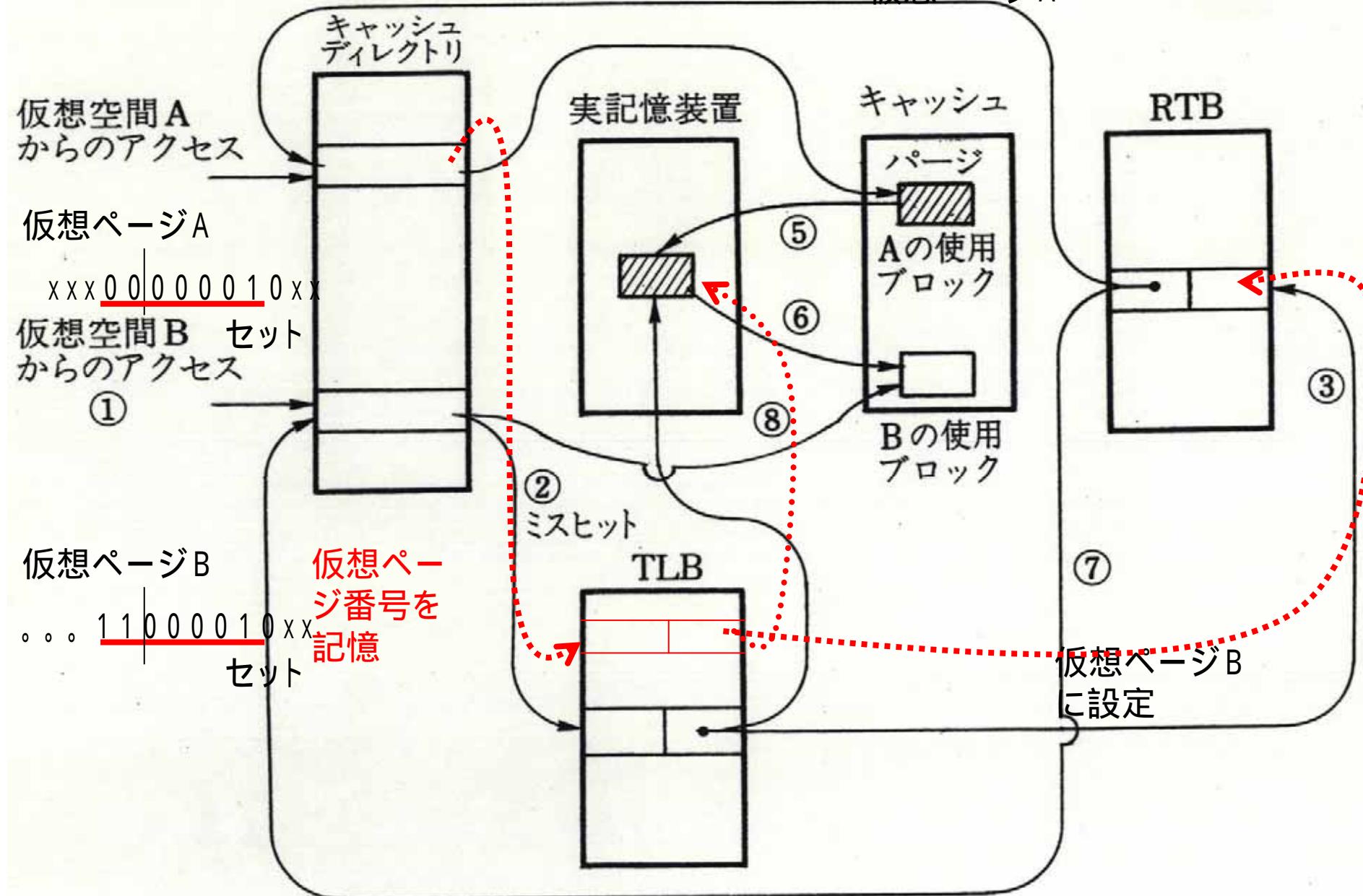

- (c)逆変換バッファ法(RTB)

### V/P方式

- (d)仮想実アドレスの混合型

# シノニムの回避 (a), (b)

図 4.20 シノニムの発生

## シノニムの回避(い)

④

仮想ページA

図 4.21 RTB 法によるシノニムの防止

TLBとキャッシュ

ディレクトリを同時に

にアクセス

**V/P方式**

Virtually Indexed

Physically Tagged

**仮想アドレスキャッシュ**

図 4.22 仮想アドレスキャッシュによるページマッピング

# ソフトウェア管理のアドレス変換 TLBは必要ない？

V/V型仮想アドレスキャッシュ

キャッシュヒット時: TLB参照の必要なし

セカンドキャッシュ: 数MB

ほとんどセカンドキャッシュでヒット

セカンドキャッシュミスヒットのとき

ページテーブルウォークをする

OS起動あるいは

ハードウェア支援

TLB: ARMで17%電力消費

TABLE 1

Qualitative Comparison of Cache-Access/Address-Translation Mechanisms

| Event                      | Frequency of Occurrence |         | Actions Performed by Hardware and Operating System per Occurrence of Event         |                                                                    |

|----------------------------|-------------------------|---------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|                            | I-side                  | D-side  | TLB + Virtual cache                                                                | Software-Mgd Addr Translation                                      |

| L1 hit, TLB hit            | 96.7%                   | 95.8%   | L1 access<br>(w/ TLB access in parallel)                                           | L1 access                                                          |

| L1 hit, TLB miss           | 0.01%                   | 0.06%   | L1 access<br>+ page table access<br>+ TLB reload                                   | L1 access                                                          |

| L1 miss, L2 hit, TLB hit   | 3.2%                    | 3.9%    | L1 access<br>+ L2 access                                                           | L1 access<br>+ L2 access                                           |

| L1 miss, L2 hit, TLB miss  | 0.03%                   | 0.09%   | L1 access<br>+ page table access<br>+ TLB reload<br>+ L2 access                    | L1 access<br>+ L2 access                                           |

| L1 miss, L2 miss, TLB hit  | 0.008%                  | 0.12%   | L1 access<br>+ L2 access<br>+ memory access                                        | L1 access<br>+ L2 access<br>+ page table access<br>+ memory access |

| L1 miss, L2 miss, TLB miss | 0.0001%                 | 0.0009% | L1 access<br>+ page table access<br>+ TLB reload<br>+ L2 access<br>+ memory access | L1 access<br>+ L2 access<br>+ page table access<br>+ memory access |

B.Jacob,T.Mudge: Uniprocessor Virtual Memory without TLBs,

IEEE Trans Computers,50,5,pp.482-499,2001

TABLE 5

Level-2 Cache Misses per 1,000 Instructions

| Benchmark      | L2 I/I cache size | L2 icache misses per 1000 instrs | L2 dcache misses per 1000 instrs |

|----------------|-------------------|----------------------------------|----------------------------------|

| GCC/Alpha      | 512K/512K         | 2.10                             | 1.94                             |

|                | 1024K/1024K       | 1.37                             | 1.88                             |

|                | 2048K/2048K       | 1.18                             | 1.85                             |

| VORTEX/PowerPC | 512K/512K         | 1.10                             | 8.80                             |

|                | 1024K/1024K       | 0.83                             | 7.96                             |

|                | 2048K/2048K       | 0.71                             | 7.54                             |

| WINWORD/x86    | 512K/512K         | 1.01                             | 6.61                             |

|                | 1024K/1024K       | 0.41                             | 5.84                             |

|                | 2048K/2048K       | 0.19                             | 5.78                             |

L2キャッシュミス: 1000命令で5回(0.5%)

L2キャッシュミスのときのペナルティ: 10 - 40サイクル

1000命令で50 - 200サイクル

オーバヘッドCPI: 0.05 - 0.2

TLBを用いた場合と遜色がない

### 4.3.5高速化技法

#### (1)命令キャッシュとオペランドキャッシュの分離

物理的に使用する場所が異なる

キャッシュミスの時の性能への影響

命令キャッシュには、書込み操作がない。

#### 分離型キャッシュの場合

命令キャッシュ, データキャッシュ

ミスヒット率:  $I^S$ ,  $D^S$

実行命令数  $N_I$ , 内ミスヒット回数  $N_{IM}$

データ参照回数  $N_D$ , 内ミスヒット回数  $N_{DM}$

$k = N_D / N_I$ : 1命令での平均データアクセス回数

ロード命令とストア命令の出現頻度

1命令を実行するのに必要とされる

キャッシュに関係した実行時間  $T_s$

$$N_I T_s = T_H * \text{Max}(N_I, N_D) + (N_{IM} + N_{DM}) T_L$$

より、

$$T_s = T_H + (N_I^S + k N_D^S) T_L$$

統合型キャッシュの場合

キャッシュメモリヒット時

命令とデータアクセスで競合

$N_I$ の命令の実行で  $N_I + N_D$  個の

キャッシュアクセス、

優先度が低い  $N_D$  個は待たされ、

$2T_H$  必要

ミスヒット率:

1命令を実行するのに必要とされる

キャッシュに関係した実行時間  $T_u$  は

$$N_I T_u = T_H * N_I + T_H * N_D + (N_{IM} + N_{DM}) T_L \text{ より,}$$

$$T_u = T_H + k T_H + (N_I + N_D) / N_I$$

$$* (N_{IM} + N_{DM}) T_L / (N_I + N_D)$$

$$= T_H + k T_H + (1 + k) T_L$$

表 4.2 キャッシュミスヒット率の例<sup>9)</sup>(整数系, 浮動小数点系を単純合計)

(a) ロー数 2, ブロックサイズ 64B の場合のミスヒット率

| キャッシュ量 | 命令キャッシュ | データキャッシュ | 統合キャッシュ |

|--------|---------|----------|---------|

| 2 KB   | 0.0115  | 0.1708   | 0.0697  |

| 4 KB   | 0.0082  | 0.1400   | 0.0517  |

| 8 KB   | 0.0054  | 0.0942   | 0.0342  |

| 16 KB  | 0.0032  | 0.0454   | 0.0173  |

| 32 KB  | 0.0022  | 0.0289   | 0.0101  |

| 64 KB  | 0.0009  | 0.0215   | 0.0067  |

| 128 KB | 0.0001  | 0.0164   | 0.0045  |

(b) キャッシュ容量 64 KB, 統合キャッシュの場合のミスヒット率

| ブロックサイズ | ロー数 1  | ロー数 2  | ロー数 4  | ロー数 8  |

|---------|--------|--------|--------|--------|

| 16 B    | 0.0204 | 0.0160 | 0.0150 | 0.0145 |

| 32 B    | 0.0135 | 0.0096 | 0.0089 | 0.0086 |

| 64 B    | 0.0106 | 0.0067 | 0.0059 | 0.0057 |

| 128 B   | 0.0102 | 0.0054 | 0.0047 | 0.0046 |

| 256 B   | 0.0115 | 0.0050 | 0.0042 | 0.0040 |

命令実行数 ( $N_I$ ) : 132,594,094,021, データ参照回数 : 45,165,001,895

# 分離型と統合型キャッシュの性能比較

$T_H = 1$  サイクル,  $T_L = 30$  サイクル

32 KB, 32 KB 分離型

64 KB 統合型

命令パイプライン

分離型キャッシュ:

$$(0.0022 + 0.34 \times 0.0289) \times 30 = 0.36$$

統合型キャッシュ:

$$0.34 + (1 + 0.34) \times 0.0067 \times 30 = 0.61$$

大きい: 数命令同時読み出

してカバー可能

## (2) 2階層キャッシュメモリ 基本原理

$$\begin{aligned}T_C &= T_H + T_{L1} + T_{L2} \\&= 0.02, \quad = 0.2,\end{aligned}$$

$T_{L1} / T_H = 5$ ,  $T_{L2} / T_H = 50$  の場合

$$T_C = 1.3 T_H$$

## (3) キャッシュバイパスバッファ キャッシュ内のアクセスバイトから転送

$$T = T_H + T_L = 2T_H$$

$$= 0.02, T_H = 1 \text{ ns}, T_L = 50T_H$$

$$T = T_H + T_{L1} + T_{L2} = 1.3T_H$$

$$= 0.2, T_{L1} = 5T_H$$

# Power4の記憶階層

Table 3: Storage hierarchy organization and size

| Component            | Organization                                           | Capacity per Chip            | latency |

|----------------------|--------------------------------------------------------|------------------------------|---------|

| L1 Instruction Cache | Direct map, 128-byte line managed as 4 32-byte sectors | 128 KB (64 KB per processor) |         |

| L1 Data Cache        | 2-way, 128-byte line                                   | 64 KB (32 KB per processor)  | 4       |

| L2                   | 8-way, 128-byte line                                   | ~ 1.5 MB                     | 1 2     |

| L3                   | 8-way, 512-byte line managed as 4 128-byte sectors     | 32 MB<br>16 MB eDRAM外<br>付け  | ?       |

| Memory               | ---                                                    | 0-16 GB                      | 3 4 0   |

Pentium4の記憶階層

L1 Data 8 KB レイテンシ 2

L2 256 KB レイテンシ 18

**Table 1. Features of the Itanium 2 processor.**

| <b>Design</b>            |                                                 |                         |

|--------------------------|-------------------------------------------------|-------------------------|

| Frequency                | 1 GHz                                           |                         |

| Pipe stages              | 8 in-order                                      |                         |

| Issue/retire             | 6 instructions                                  |                         |

| Execution units          | 2 integer, 4 memory, 3 branch, 2 floating-point |                         |

| <b>Silicon</b>           |                                                 |                         |

| Technology               | 180 nm                                          |                         |

| Core                     | 40 million transistors                          |                         |

| L3 cache                 | 180 million transistors                         |                         |

| Size                     | 421 mm <sup>2</sup>                             |                         |

| <b>Caches</b>            |                                                 |                         |

| L1 instruction           | Size                                            | 16 Kbytes               |

|                          | Latency                                         | 1 cycle                 |

|                          | Protection                                      | Parity                  |

| L1 data                  | Size                                            | 16 Kbytes               |

|                          | Latency                                         | 1 cycle                 |

|                          | Protection                                      | Parity                  |

| L2                       | Size                                            | 256 Kbytes              |

|                          | Latency                                         | 5, 7, or 9+ cycles      |

|                          | Protection                                      | Parity or ECC*          |

| L3                       | Size                                            | 3 Mbytes                |

|                          | Latency                                         | 12+ cycles              |

|                          | Protection                                      | ECC                     |

| <b>Benchmark results</b> |                                                 |                         |

| Spec CPU2000 score       | 810                                             | IEEE Micro, March, 2003 |

| Spec FP2000 score        | 1,431                                           |                         |

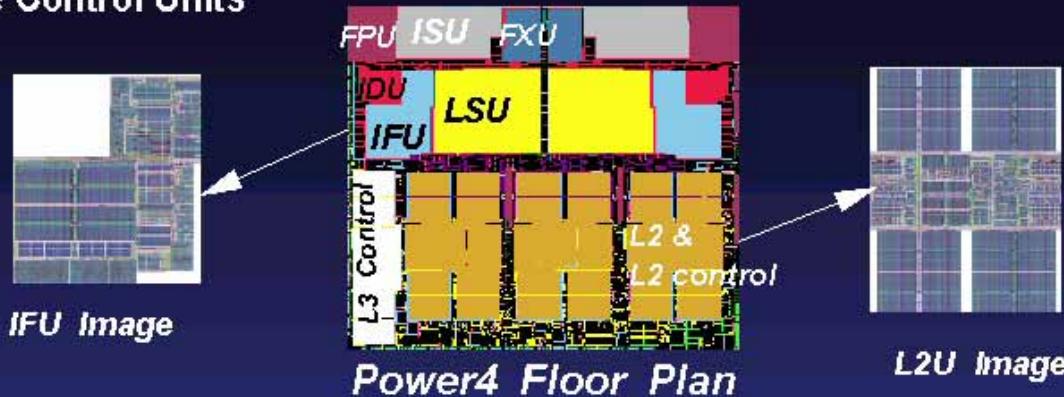

# Power4 Processor Design

- ▶ Power4 Floor Plan and Images of the Instruction Fetch (IFU) & L2 Cache Control Units

- ▶ Power4 Processor Chip Features

- ▶ Two microprocessors, 3-level cache hierarchy

- ▶ >30 GB/s (>500 MHz) interconnection fabric

- ▶ 2200 signal I/O; 170M transistors

- ▶ Configured for 8-way system on MCM

- ▶ CMOS 8S2-SOI technology & copper wiring

- ▶ Microprocessor core

- ▶ > 1GHz clock frequency; 64KB L1 instruction cache

- ▶ 64-bit PowerPC for RS6000 & AS400 systems

- ▶ Out-of-order, speculative, 8-issue superscalar design

- ▶ Memory sub-system

- ▶ 1.5 MB shared L2 caches

- ▶ 32 MB off-chip L3 (on-chip control); Bandwidth > 10GB/s

Figure 2. Power5 chip (FXU = fixed-point execution unit, ISU = instruction sequencing unit, IDU = instruction decode unit, LSU = load/store unit, IFU = instruction fetch unit, FPU = floating-point unit, and MC = memory controller).

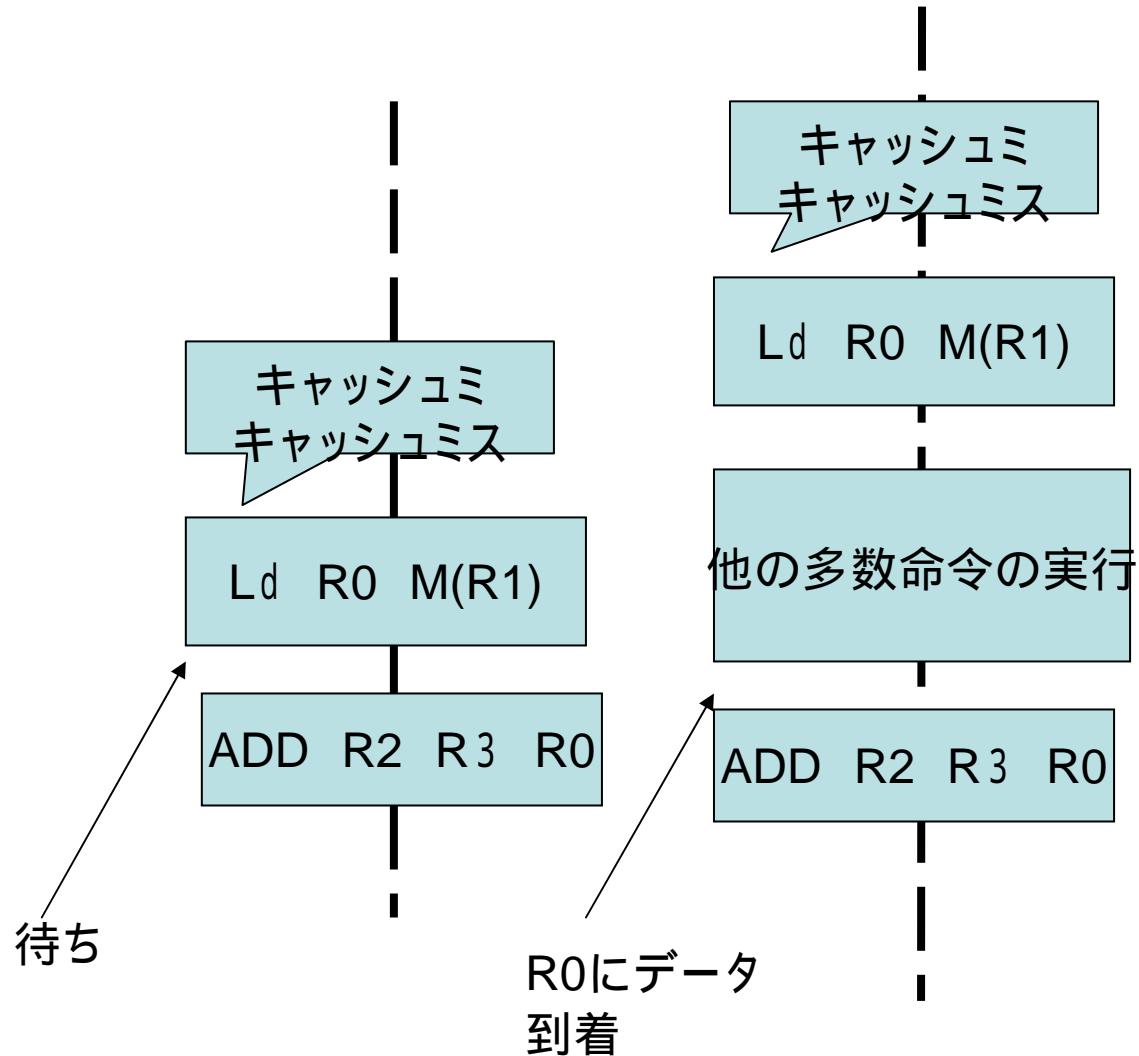

#### (4) ノンブロッキングキャッシュ

先行命令でキャッシュミスでも

後続命令どんどん実行

パイプラインバブル減少

データの先読みによる遅延時間

(レイテンシ)減少: **コンパイラによる**

**キャッシュ制御VSオンデマンド制御**

#### (5)ストアバッファ

ストアスルーでメモリ書き込みを待たないで

先実行: 置いてきぼり制御

#### (6)命令バッファ

命令キャッシュから数命令同時フェッチ

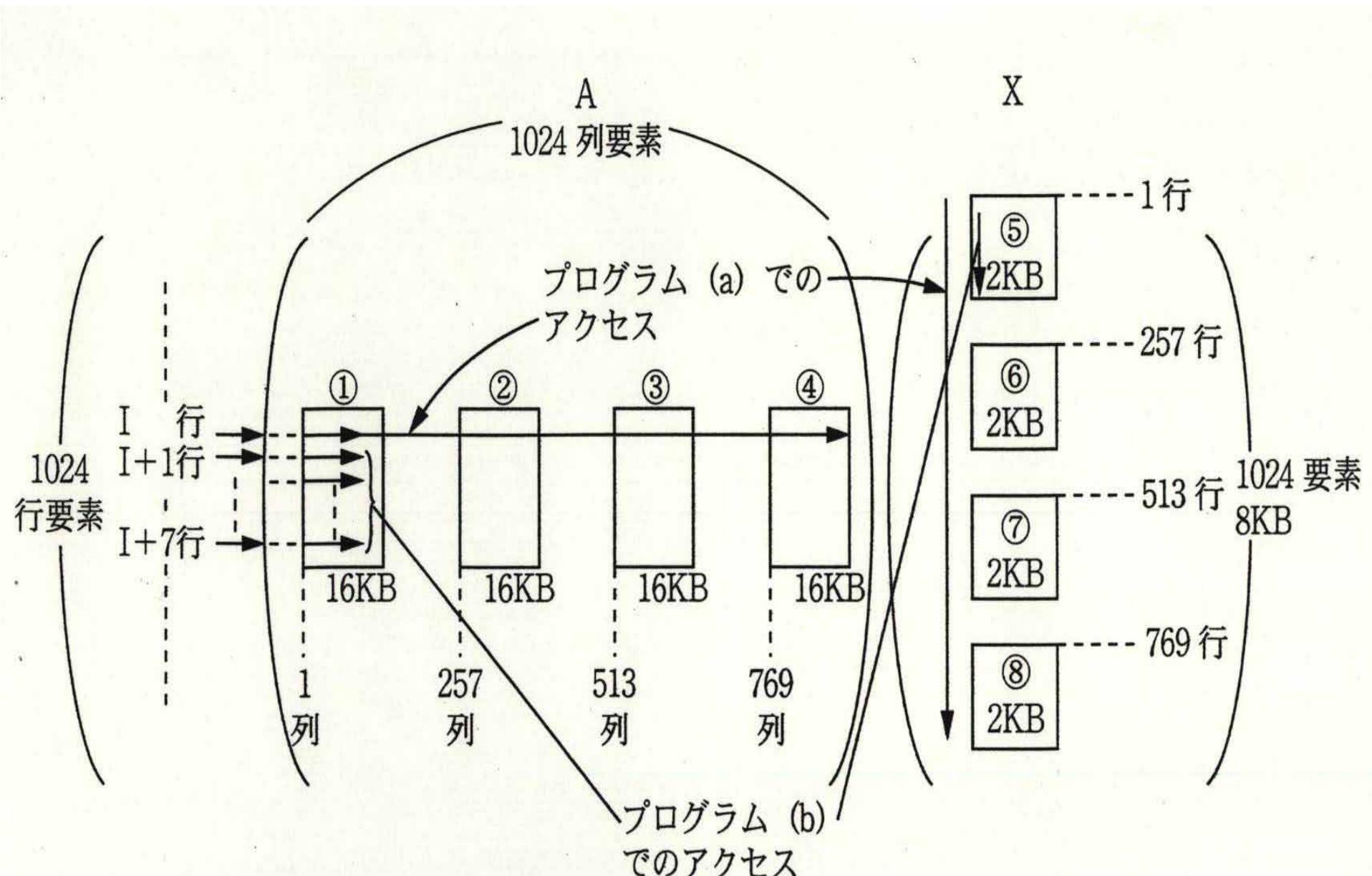

#### 4.3.6 キャッシュメモリの有効性

1024×1024の2次元配列AとベクトルXの積B

$$B_i = \sum_j A_{ji} X_j$$

各要素データは8B

キャッシュブロックのサイズは64B

(すなわち8要素の格納が可能)

キャッシュ容量: 18KB

## 単純なプログラム

```

DO 10 I=1,1024

DO 10 J = 1 , 1024

B(I) = A(I, J) * X(J)

10 CONTINUE

```

## 改良プログラム

```

DO 10 I = 1 , 1017 , 8

DO 10 K = 1 , 4

DO 10 J = 256 (K - 1) + 1 , 256 K

B(I) = B(I) + A(I, J) * X(J)

B(I + 1) = B(I + 1) +

A(I + 1, J) * X(J)

.....

B(I + 7) = B(I + 7) +

A(I + 7, J) * X(J)

10 CONTINUE

```

タイミング法

図 4.23 行列ベクトル積

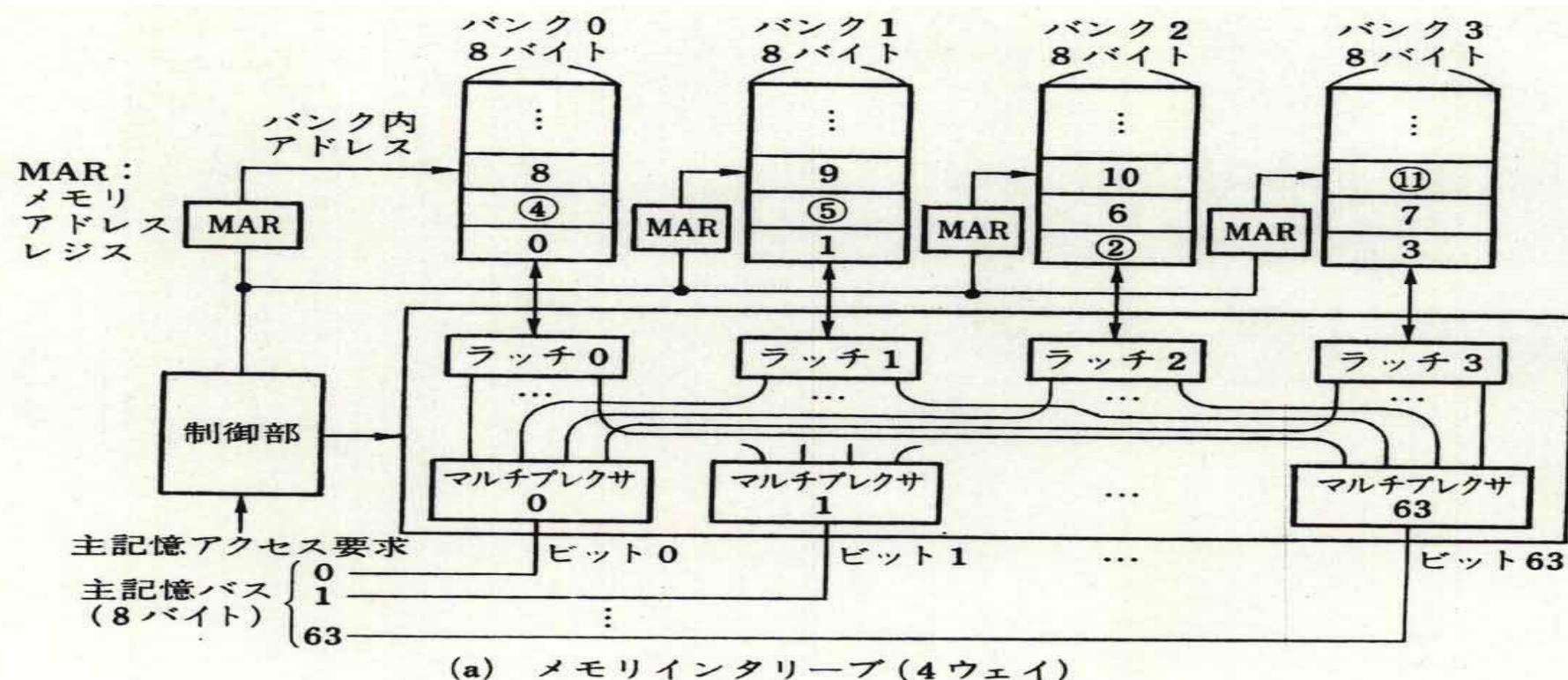

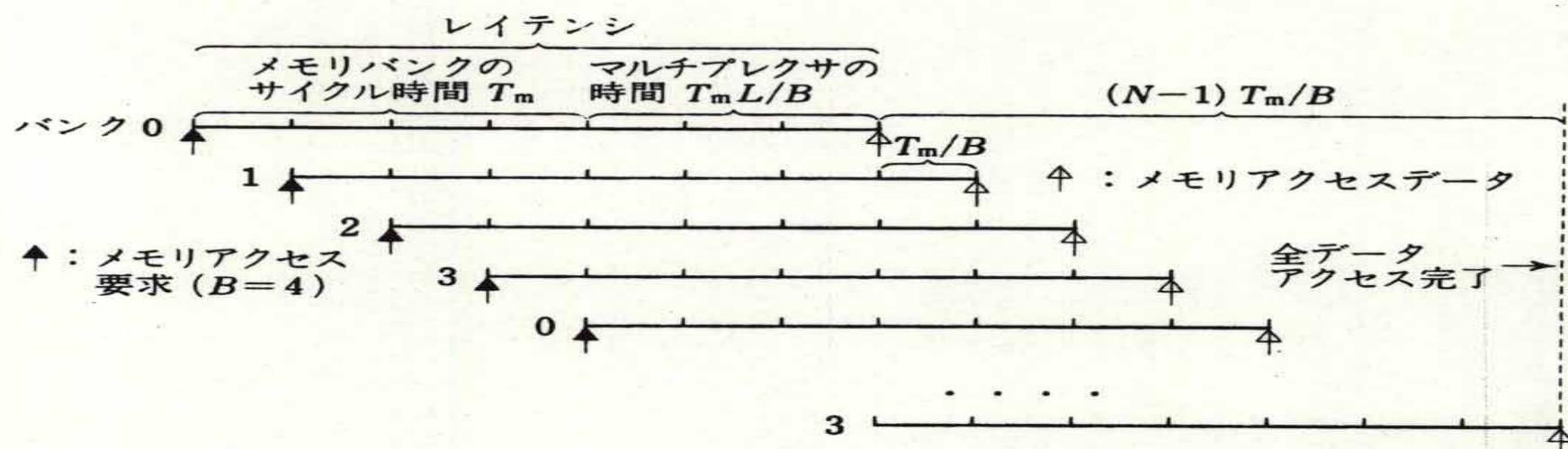

## 4.6 主記憶装置

インターリープ

ストアスルーの時: 同時書き込み可能で

高速化

ストアインの時: メモリバス幅が

太ければよい

ブロック単位の転送

(a) メモリインタリープ (4 ウェイ)

(b) レイテンシとメモリバンド幅

図 4.30 主記憶インタリープ方式

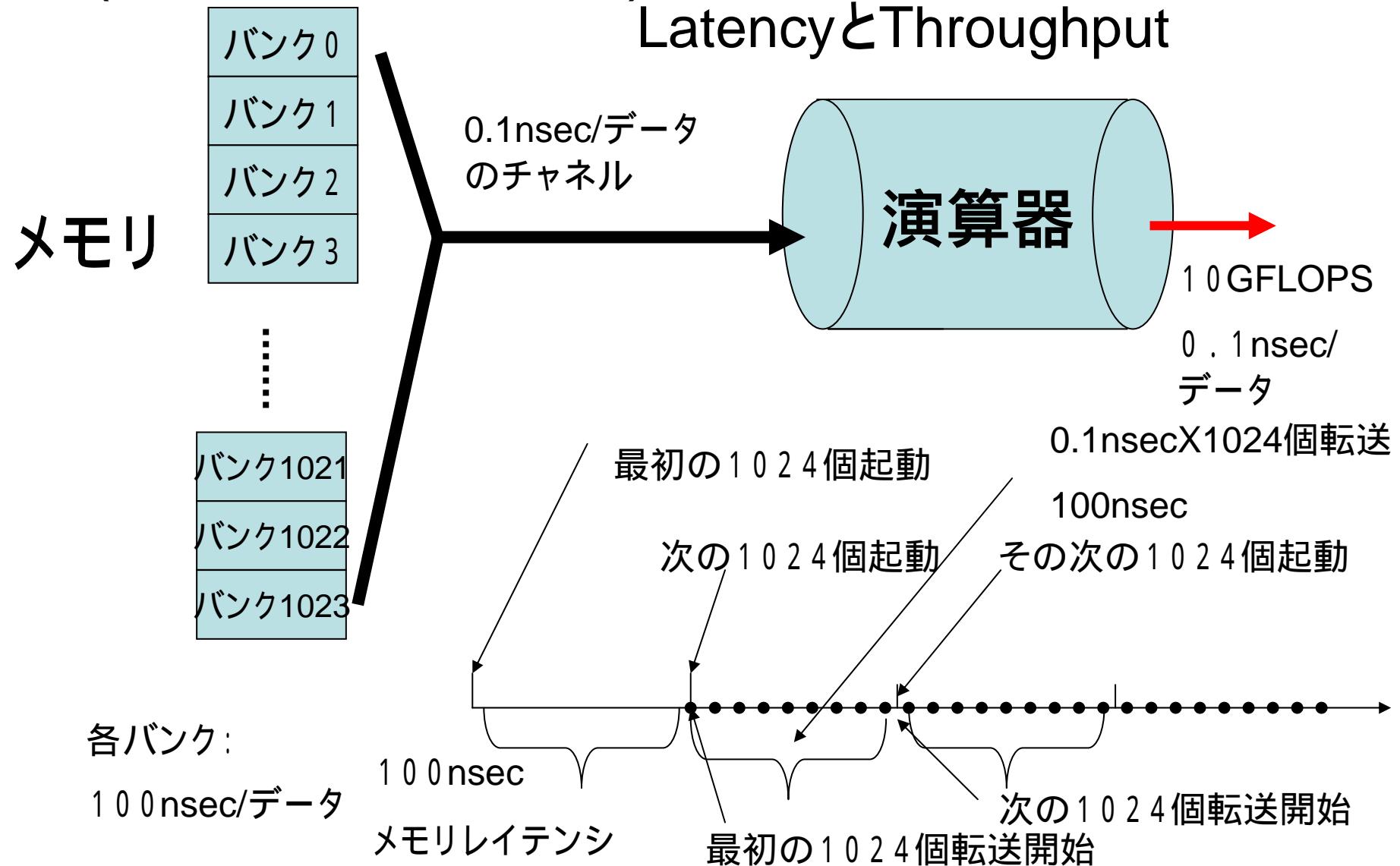

# スーパコンピュータ: 1024バンク構成 (ベクトルプロセッサ)

## スクエードメモリ(直交メモリ化)

|          |   |          |          |          |          |

|----------|---|----------|----------|----------|----------|

| バンク内アドレス | 3 | $a_{41}$ | $a_{42}$ | $a_{43}$ | $a_{44}$ |

|          | 2 | $a_{31}$ | $a_{32}$ | $a_{33}$ | $a_{34}$ |

|          | 1 | $a_{21}$ | $a_{22}$ | $a_{23}$ | $a_{24}$ |

|          | 0 | $a_{11}$ | $a_{12}$ | $a_{13}$ | $a_{14}$ |

|          |   | 0        | 1        | 2        | 3        |

メモリバンク

(a)

|          |   |          |          |          |          |

|----------|---|----------|----------|----------|----------|

| バンク内アドレス | 4 | $a_{42}$ | $a_{43}$ | $a_{44}$ | $a_{45}$ |

|          | 3 | $a_{33}$ | $a_{34}$ | $a_{35}$ | $a_{41}$ |

|          | 2 | $a_{24}$ | $a_{25}$ | $a_{31}$ | $a_{32}$ |

|          | 1 | $a_{15}$ | $a_{21}$ | $a_{22}$ | $a_{23}$ |

|          | 0 | $a_{11}$ | $a_{12}$ | $a_{13}$ | $a_{14}$ |

メモリバンク

(b)

図 4.33 スキュードメモリ方式