# 第6章 機械命令レベルでの並列処理

## 6.1 機械命令の依存関係

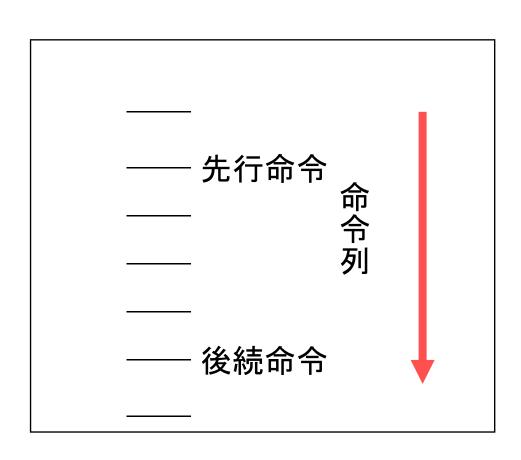

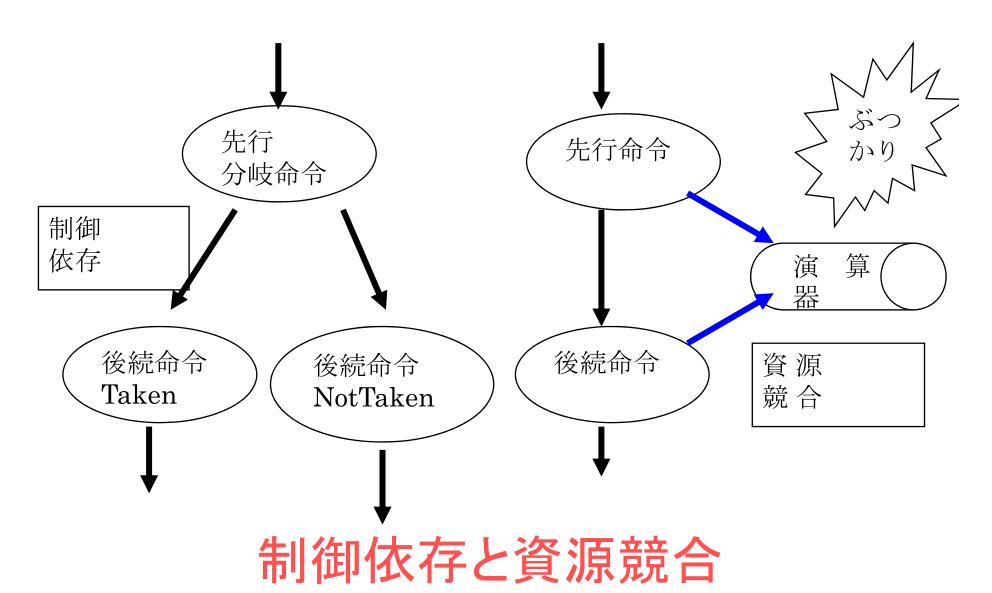

先行/後続命令の並列実行を 阻むもの

> データ依存 制御依存 資源競合

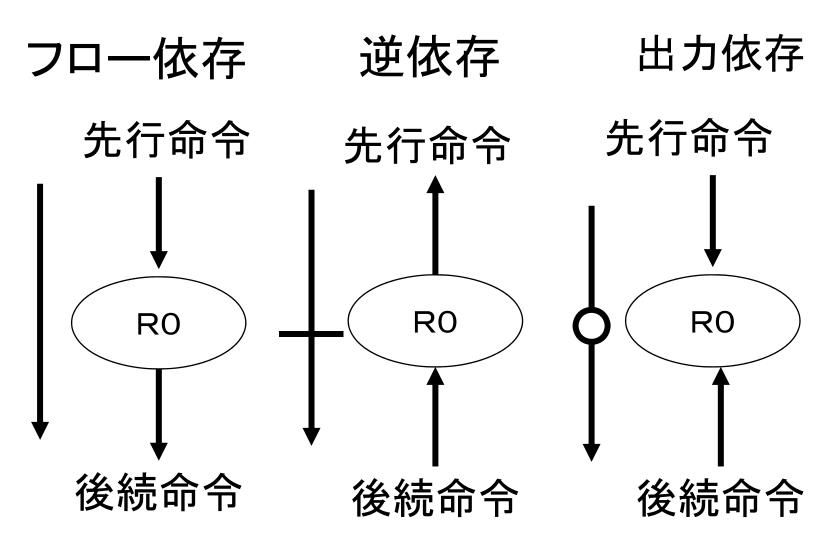

データ依存

# リネーミング

逆依存 出力依存 先行命令 先行命令 R0 RO R1 R1 後続命令 後続命令

```

リネーミング

```

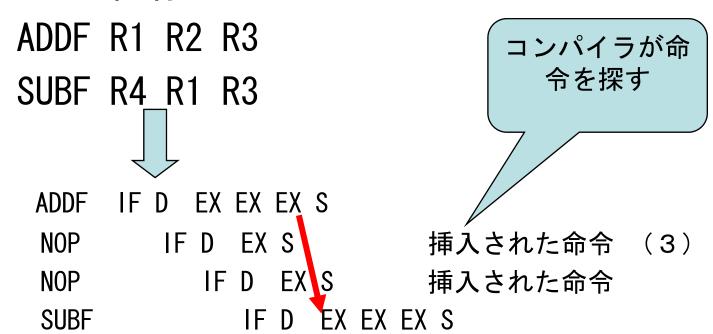

ADDF R1 R2 R3

SUBF R4 R1 R3

ADDF R1 R5 R6 (1)

MULF R7 R1 R2

ADDF R1 R2 R3

SUBF R4 R1 R3

ADDF (R8) R5 R6 (2)

MULF R7(R8)R2

R1をR8にリネーミング

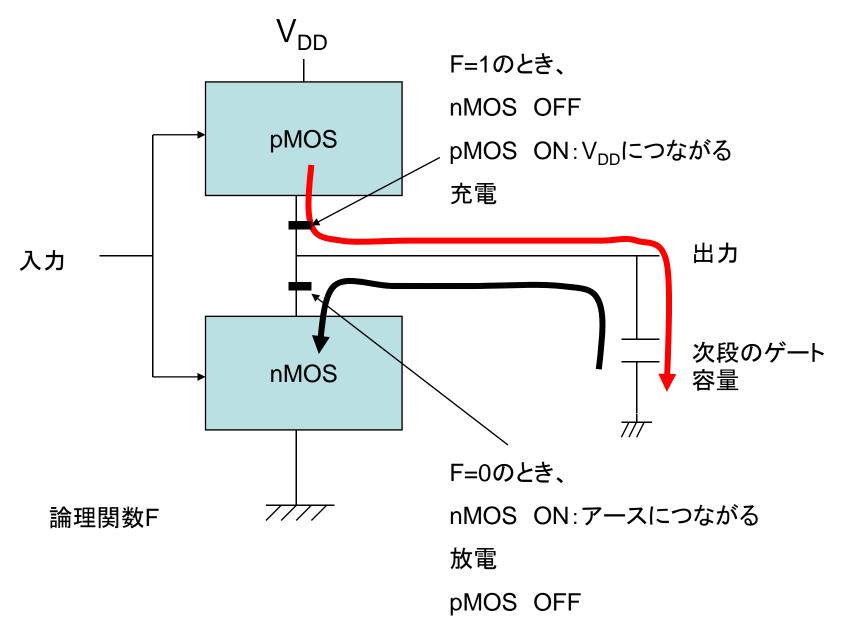

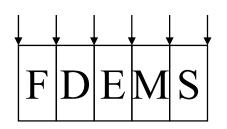

## 6. 1. 2命令レベルでの並列処理の分類 命令パイプラインのモデル

- ① I F (命令フェッチ)

- ②D(デコード):命令デコード、レジスタ読出し

- ③ E X (実行):

整数演算は1サイクル

浮動小数点加算、乗算は、3ステージのパイプ

演算器バイパス機構が存在

ロードストア命令2サイクル

分岐命令の分岐先アドレス:M(R+D)

EXステージで確定し、直ちにIFステージへ

④S (結果の格納)

### 命令レベルでの並列処理の分類項目

- (1) 静的/動的命令スケジュール

- ①ハードウェアに命令の依存関係を検出する機構 がないとき:静的

データ依存

#### 遅延分岐

遅延スロットは2である。 ADDF R1 R2 R3 BRCZ M(R10)

ADDF IF D EX EX EX S

NOP IF D EX S

NOP IF D EX S

BRCZ IF D EX S 分岐命令(4)

NOP IF D EX S 遅延スロット

NOP IF D EX S 遅延スロット

IF D EX EX EX S

分岐先命令

插入命令

#### 静的スケジュールの特徴

- ・ハードウェア:単純、高速化。

- NOPが多用、プログラムサイズ増大、キャッシュメモリとの親和性悪化

- ・遅延スロット数の後継コンピュータでの変更: 互換性喪失

②ハードウェアに命令の依存解析をする能力があるとき:動的

データ依存

ADDF IF D EX EX EX S

SUBF IF D - EX EX EX S (5)

ハードウェアによる データ待ち合わせ 分岐

①分岐条件が確定するまで分岐先命令のフェッチを 開始しない方式では、

ADDF IF D EX EX EX S

BRCZ IF D EX - S 分岐命令(6)

IF D EX S 分岐先命令

②分岐予測を採用しているときには、

ADDF IF D EX EX EX S

BRCZ IF D EX - S

分岐命令

IF D EX S分岐先命令(予測側)(7)

IF D EX S (予測失敗のとき)

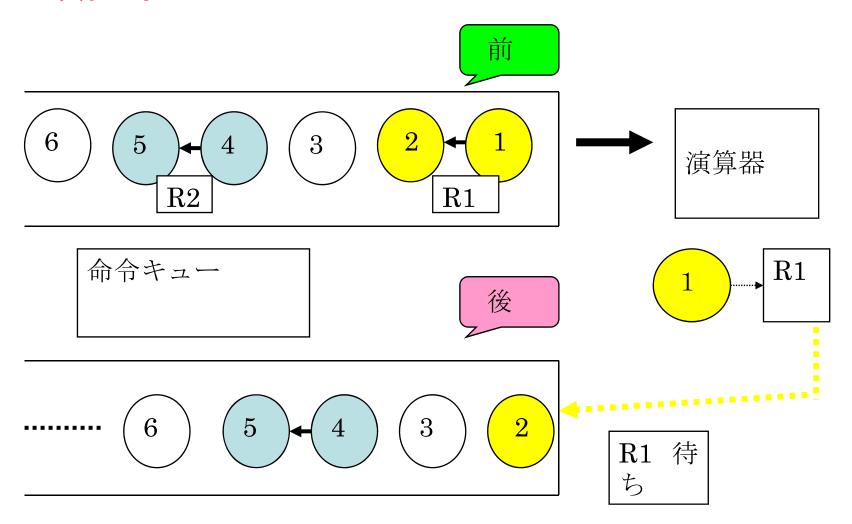

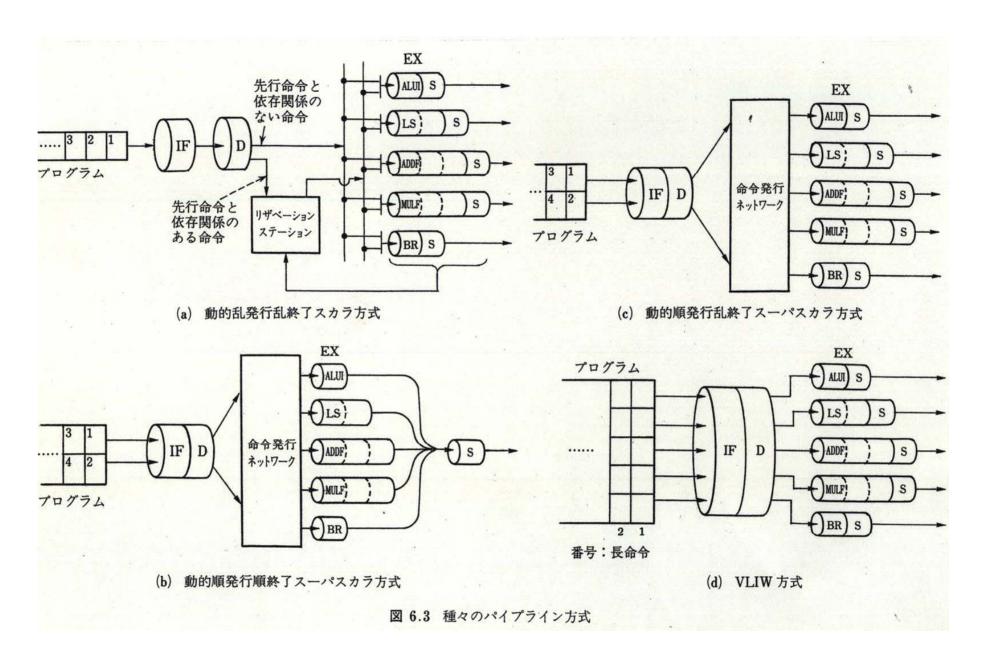

#### (2)命令の発行順序と終了順序

命令の発行:命令パイプラインのDステージからEX ステージに命令実行ステージを移すこと

#### ①順発行

先行命令と依存関係にある後続命令がくると、その命令およびそれ以降の命令の発行を停止する。後続命令は先行命令がEXステージに入ってはじめて発行できる。

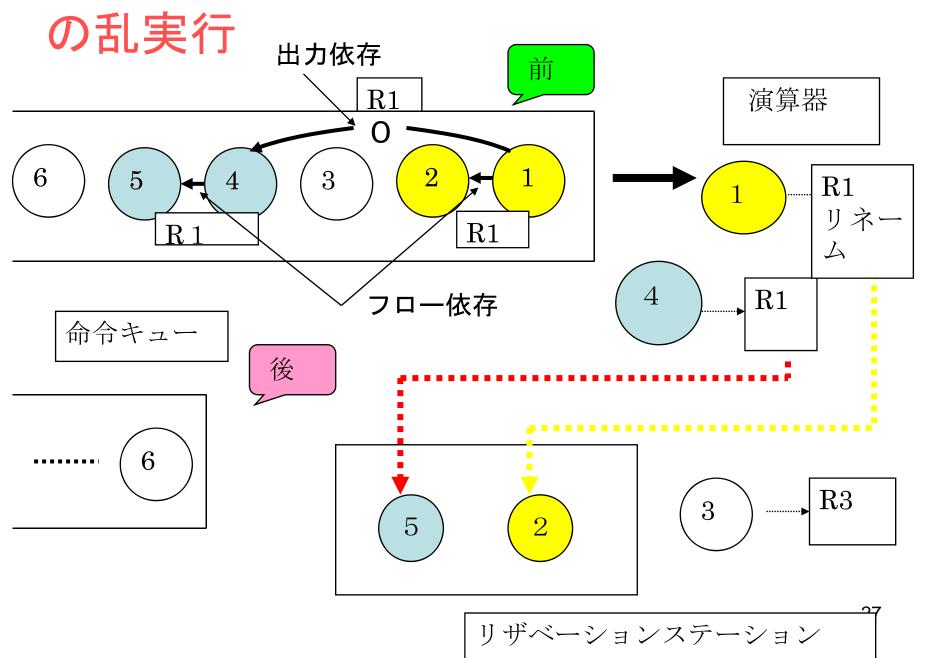

#### ②乱発行

依存関係にある命令はリザベーションステーションに 格納され、その命令の後続命令が発行される。した がって、プログラムに並んだ順番とは異なった順番で 命令が発行される。

命令の終了とは、Sステージの実行終了を指す。

①順終了 ②乱終了

# 順発行

# 乱発行

### ①順発行順終了

### ②順発行乱終了

### ③乱発行順終了

### 4 乱発行乱終了

```

リネーミングあり

IF D EX EX EX S

ADDF R1 R2 R3

SUBF R4 R1 R3

IFD - FXFXFXS

(11)

MULF R8 R5 R6

IF D EX EX EX S

ADDF R7 R8 R2

IFD - - EXEXEXS

ADDI R10 R11 R13

IF D EX S

SUBI R14 R10 R11

IF D EX S

ADDF R1 R2 R3

IF D EX EX EX S

同時終了でも乱終了

SUBF R4 R1 R3

IF D - - EX EX EX S

と同一性能

MULF R8 R5 R6

IF D EX EX EX - S

- - EX EX EX S

ADDF R7 R8 R2

IF D

IF D EX -

ADDI R10 R11 R13

IF D EX - - S

SUBI R14 R10 R11

18

```

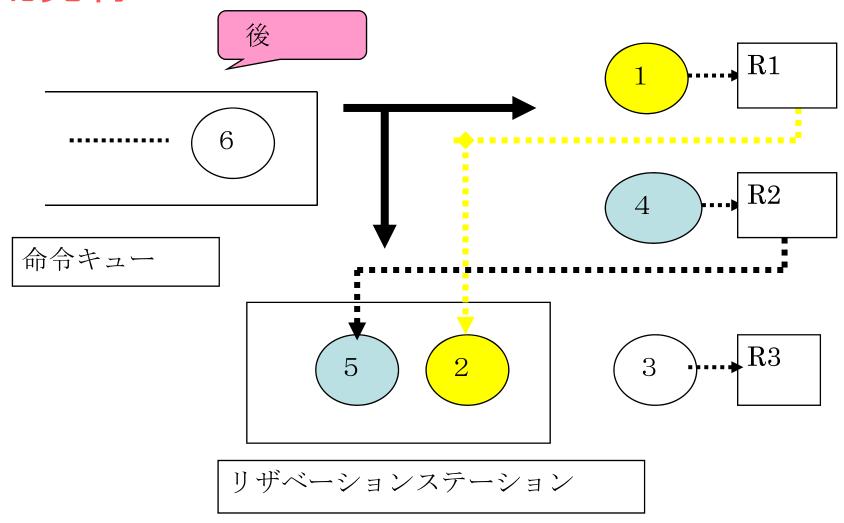

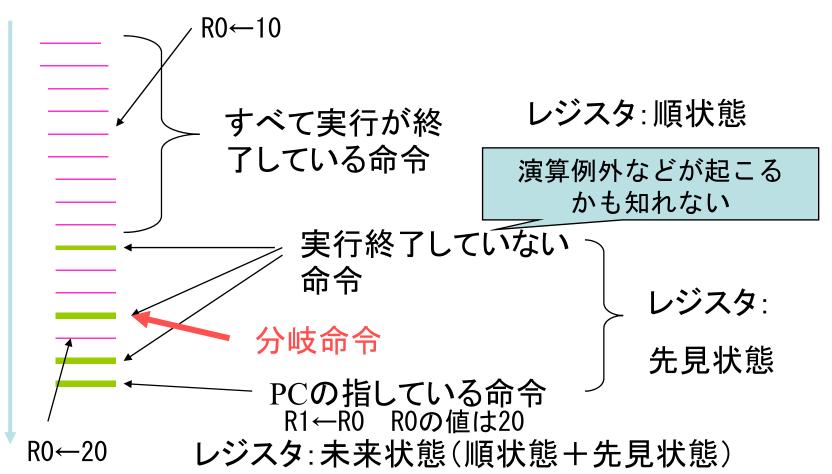

#### 正確な割込み

旧コンピュータ: PCの指した命令のSステージ終了時に割込み (例外)発生。状態保存し、再実行可能

#### 不正確な割り込み

乱終了:例外を起こした命令よりずっと先の命令をPCは指している。命令実行終了のもの未終了のもの混在。状態保存困難、再実行困難。例外発生命令のPC≠例外を受け付けた命令のPC

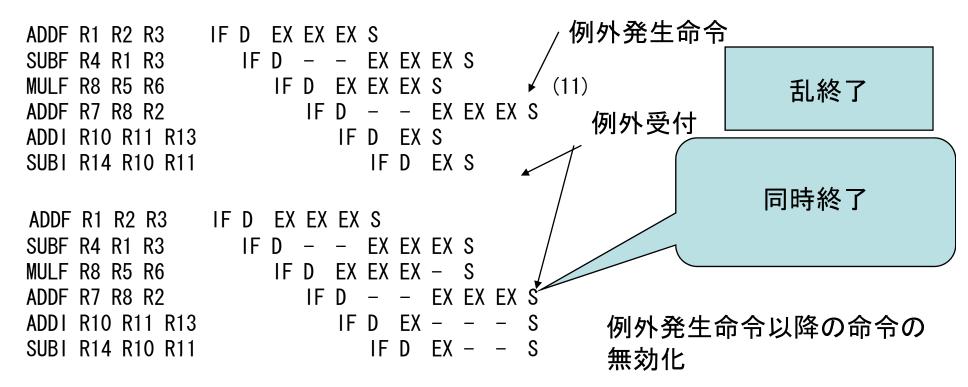

### (3) 命令フェッチ方法

- ①スカラ方式

- ②スーパスカラ方式

- ③VLIW方式

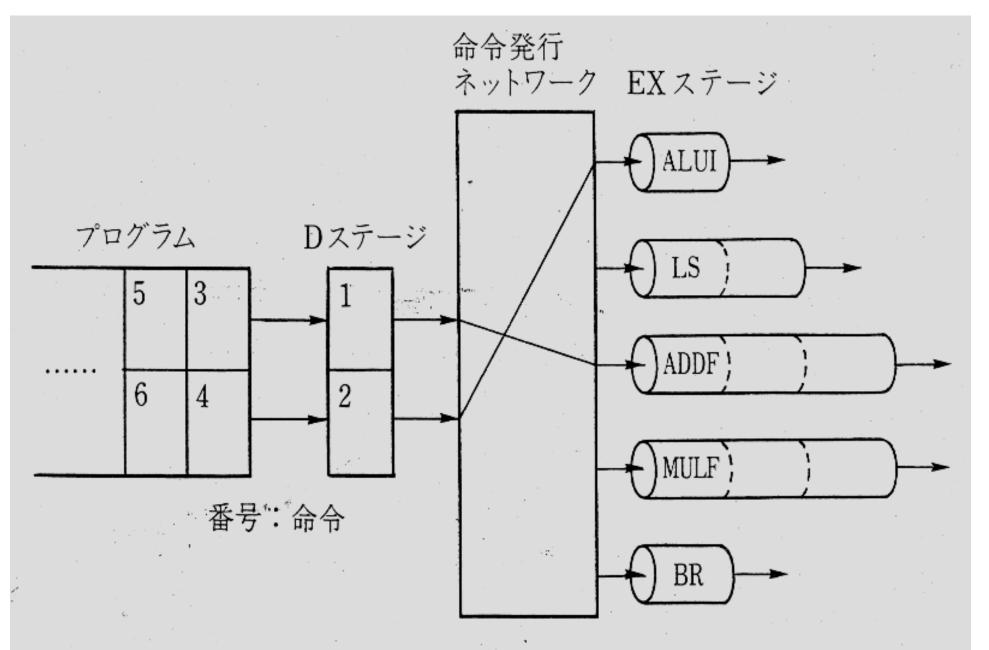

# スーパスカラ

命令発行

ネットワーク EXステージ

(a) スーパスカラ方式での命令と演算装置の対応

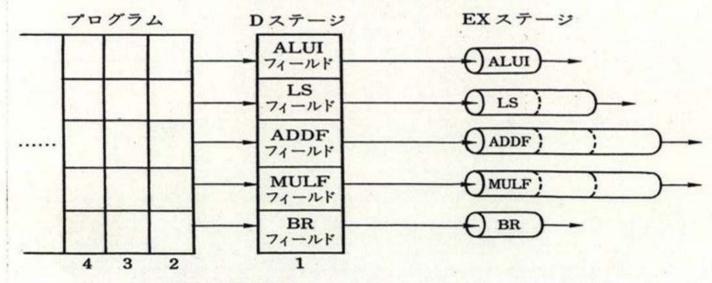

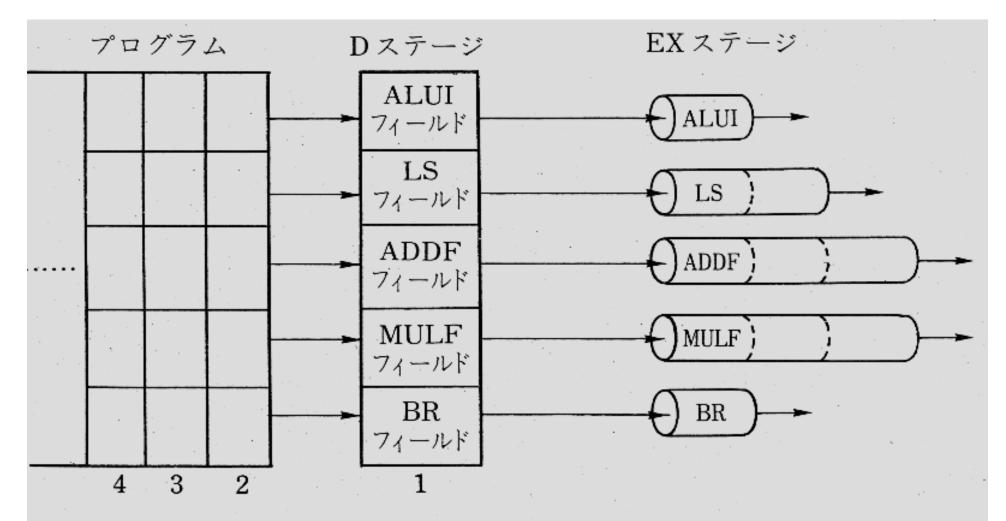

**VLIW**

番号:長命令

(b) VLIW 方式での命令と演算装置の対応

ALUI:整数, LS:ロードストア, ADDF:浮動小数点加算,

MULF:浮動小数点乗算, BR:分岐

図 6.2 スーパスカラ/VLIW 方式での命令と演算装置の対応

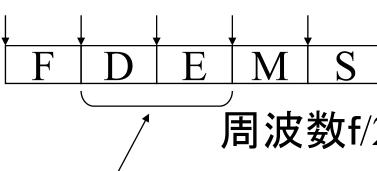

### 6.2動的乱終了スカラ方式

- 6.2.1動的順発行乱終了スカラ方式

- ①レジスタへの同時書込みマルチポートのレジスタ必要

- ②EX、Sステージでの制御複雑

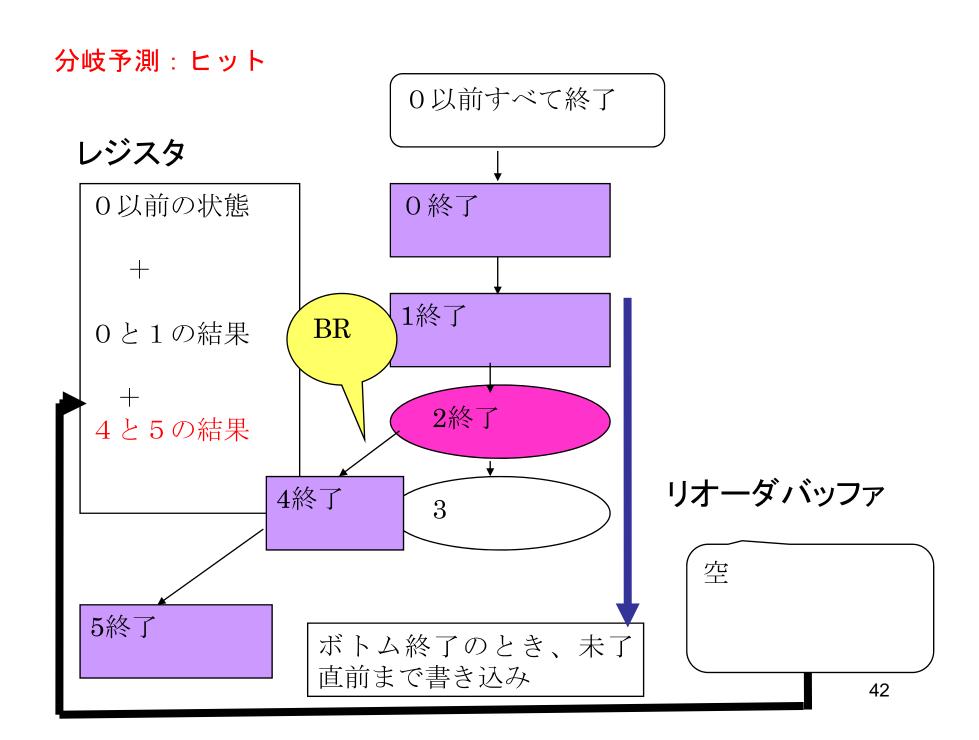

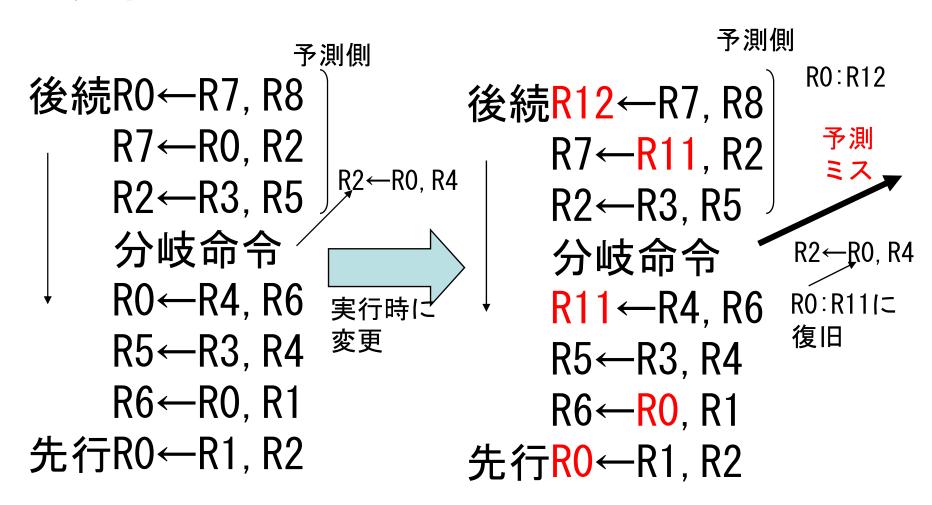

- ③分岐予測を採用する際 予測された側の命令系列を命令パイプラインに投入 分岐命令のSステージが終了後、予測された側の命 令系列を終了させる

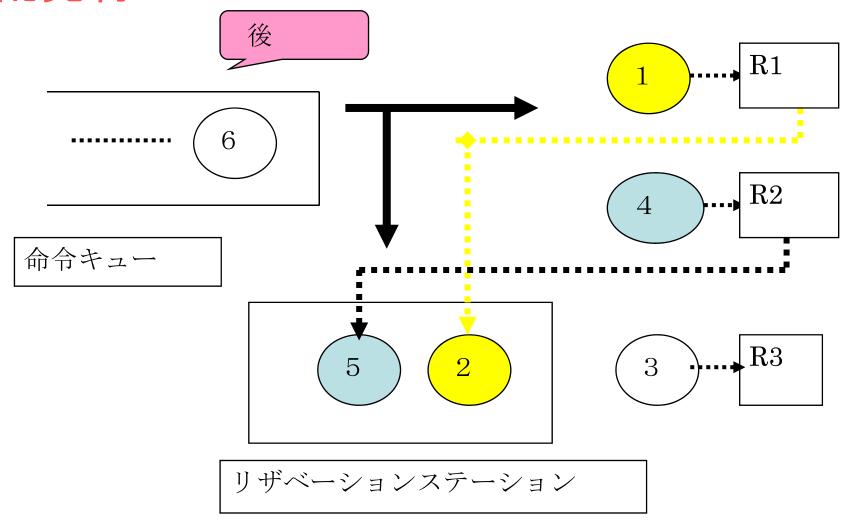

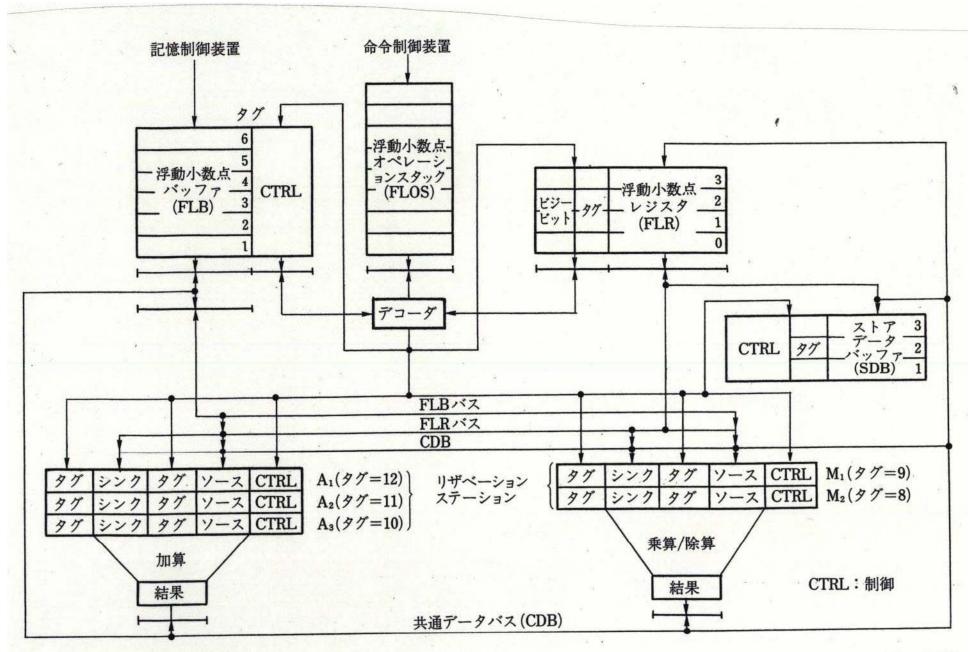

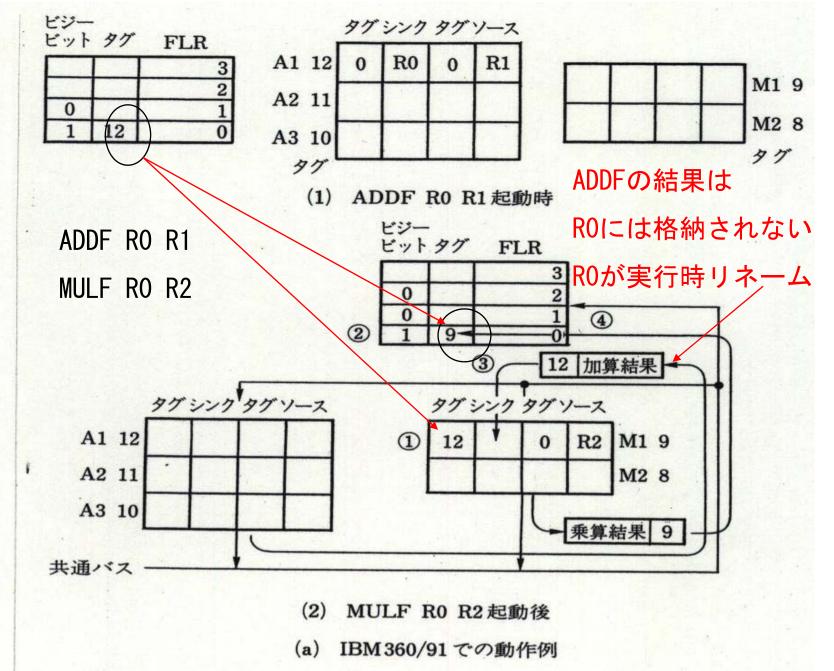

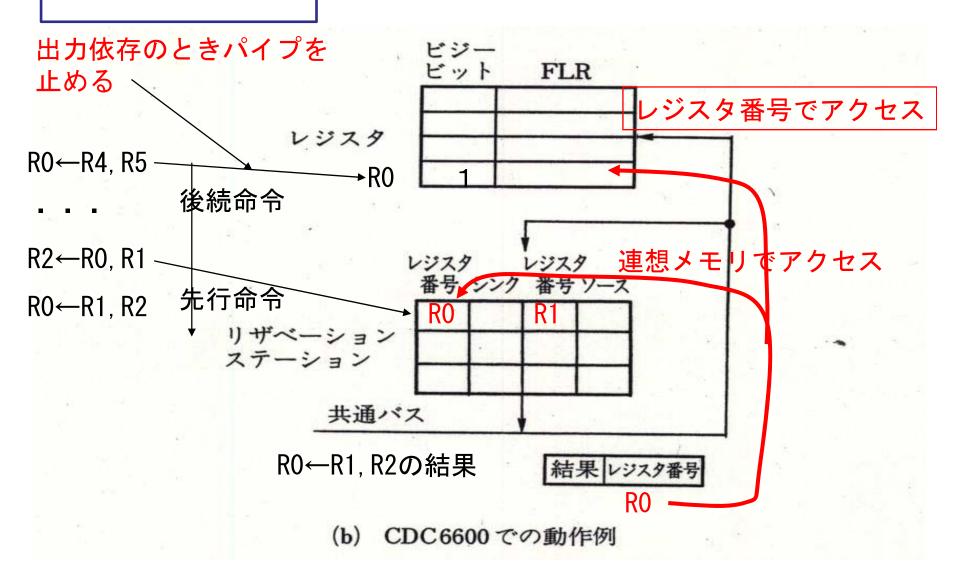

## 6.2.2動的命令乱発行乱終了スカラ方式

- (1) I BM360/91: 1967年稼働

- (2) I BM360/91の動作 リザベーションステーション レジスタリネーミング 共有バス

- ①逆依存

- ②フロー依存

- ③出力依存

- (3) CDC6600のスコアボード方式 出力依存のときインターロック

- 6.2.3不正確な割込み

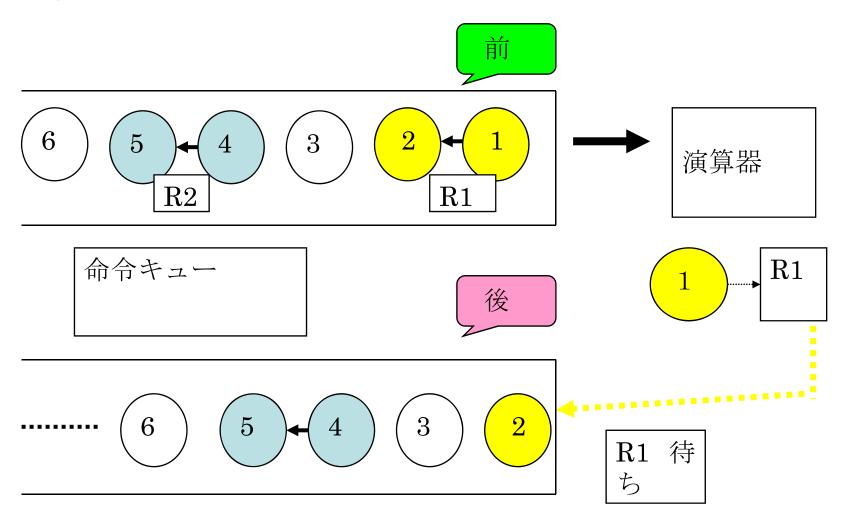

# 順発行

# 乱発行

連想メモリ

26

## Tomasulo方式

図 6.4 IBM 360/91 の演算装置の構成 [R. M. Tomasulo: An Efficient Algorithm for Exploiting Multiple Arithmetie Units, IBM Journal, pp. 25-33 (1967)]

CDC6600: 1964年稼働 S. Cray RISCの原型 3 ーオペランド

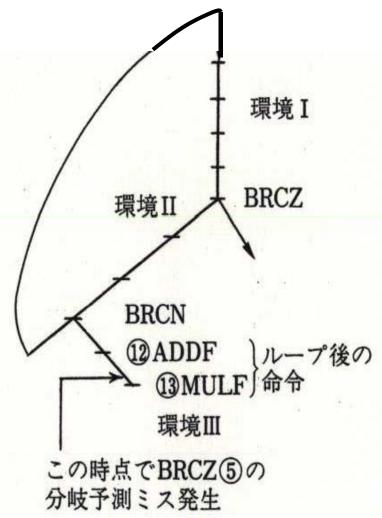

#### 6.3投機的命令実行方式

6.3.1基本方式

分岐命令を越えて投機的実行を行う利点

```

DO 10 I=1, N

Z(I)=X(I)/Y(I)

IF (Z(I). EQ. 0) GOTO 20 (12)

10 CONTINUE

A=A+B

D=A*D

20 ----

```

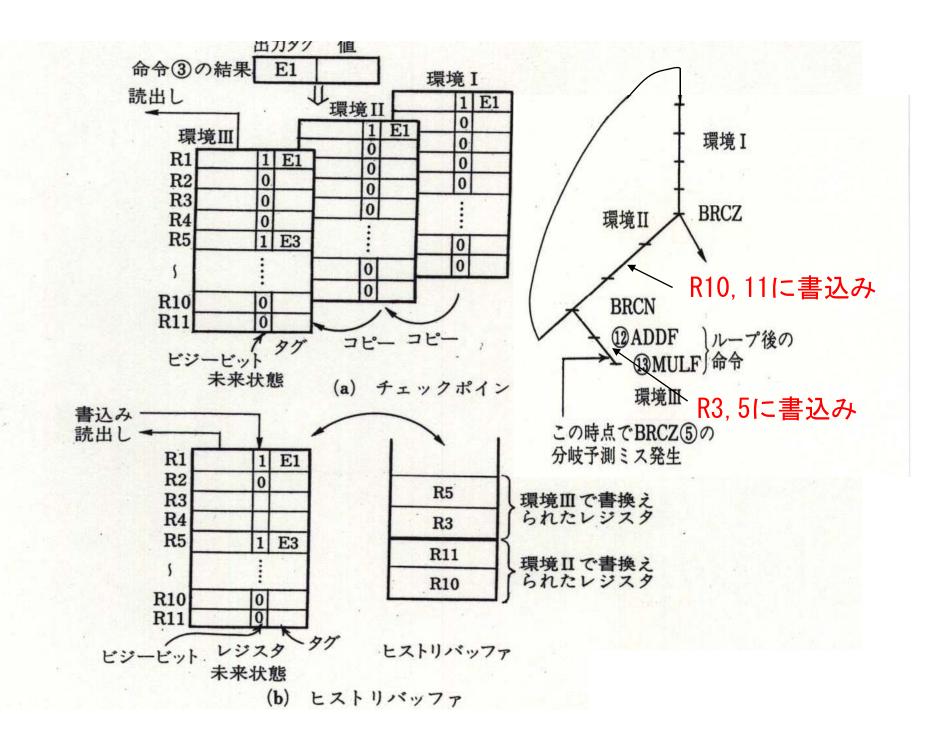

(b) 分岐予測の誤り

図 6.6 レジスタの状態

```

L LOAD R1 M(R10+D1)

LOAD R2 M(R10+D2)

DIVF R1 R2

STORE M(R10+D3) R1

BRCZ M (PC+10)

Jに分岐

(13)

ADDI R10 #11

ADDI R11 #11

M(PC-16)

BRCN

Lに分岐

ADDF R3 R4

MULF R5 R3

除算に12マシンサイクル必要

```

# レジスタの状態

先行命令

- 1) LOAD IF D EX EX S

- 2 LOAD IF D EX EX S

- 4 STORE IF D - - - EX EX S

- 5 BRCZ IF D EX - - - S

- 6 ADDI IF D EX S

- 7 ADDI IF D EX S

- 8 BRCN IF D EX S (14)

- 9 LOAD

- 10 LOAD

- ① DIV EX . .

- IF D EX EX S 2回目の反復

- IF D EX EX S

- $\mathsf{IF}\;\mathsf{D}\;-\;-\;\;\mathsf{EX}\;\mathsf{EX}$

- 12 ADDF

- (13) ADDF

- IF D EX EX EX S ループ終了

- IF D - EX EX EX S

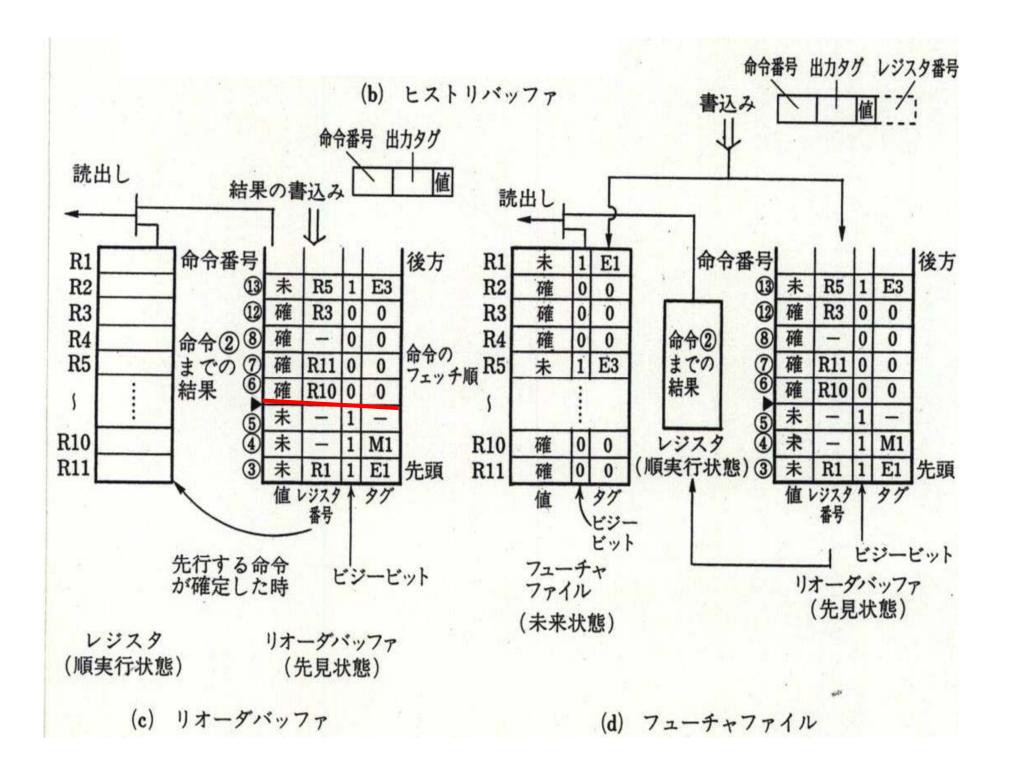

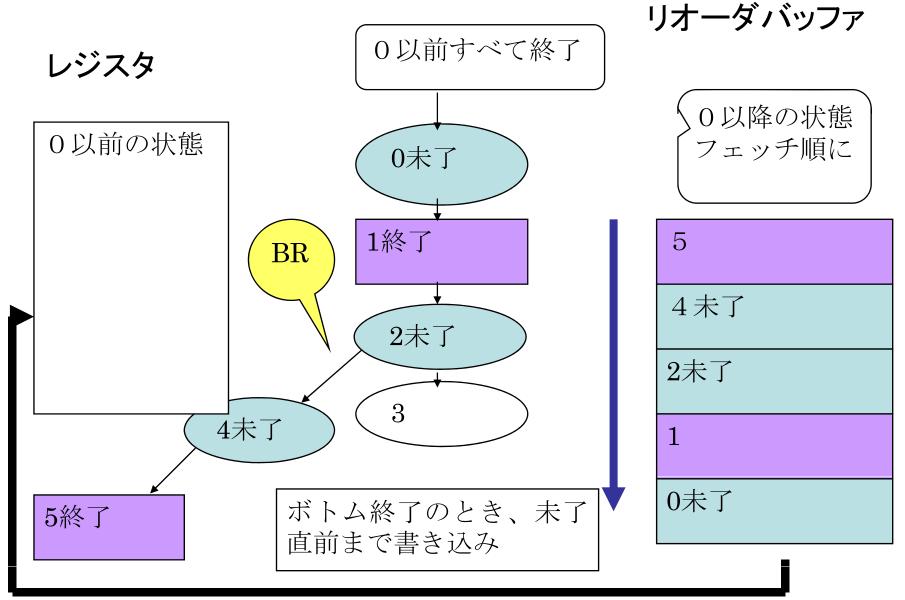

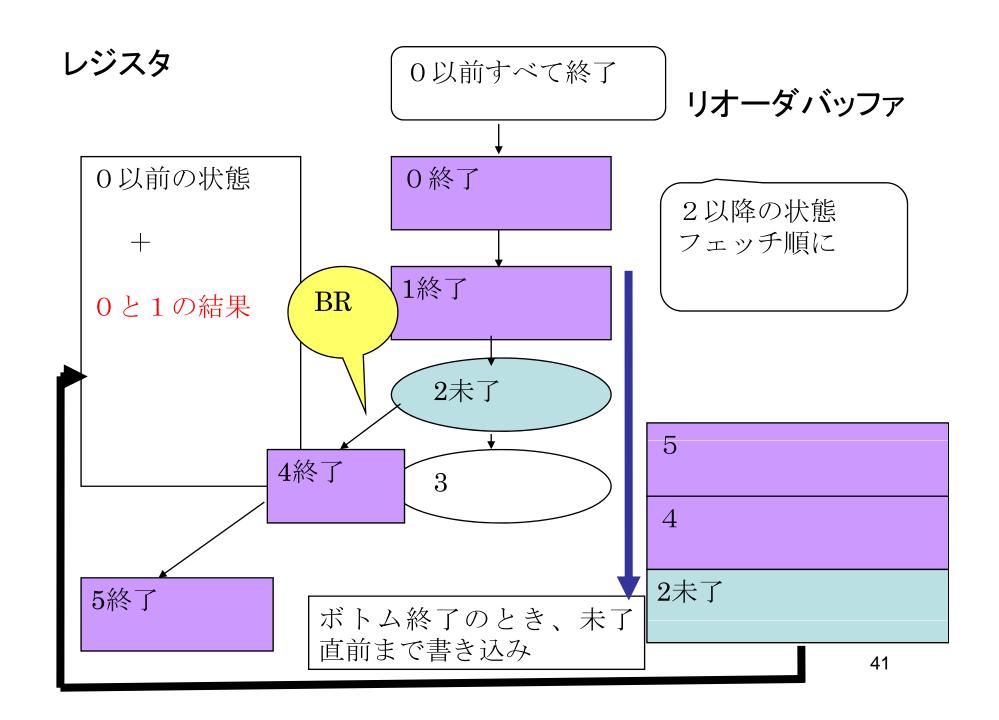

- 6.3.2レジスタの復旧機構

- ①チェックポイントリペア(Check point repair)

- ②ヒストリバッファ (History buffer)

- ③リオーダバッファ (Reorder buffer)投機実行正確な割込みも保証

データ呼出し:連想記憶

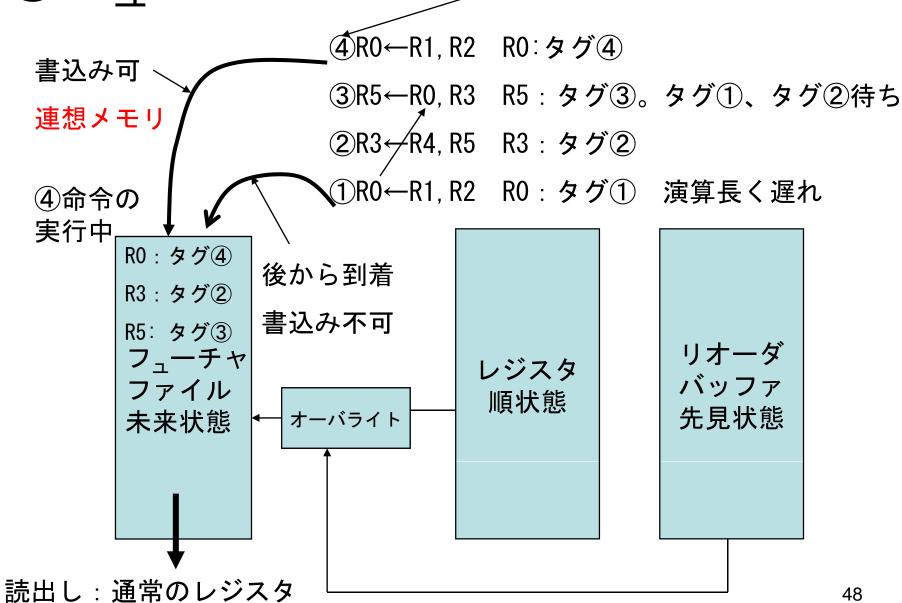

- ④フューチャファイル(Future file) リオーダバッファ フューチャファイル:未来状態を保持

- ⑤リネーミングレジスタ

## 投機実行のメカニズム

レジスタリネーミング法

- ①リオーダバッファを利用する方法

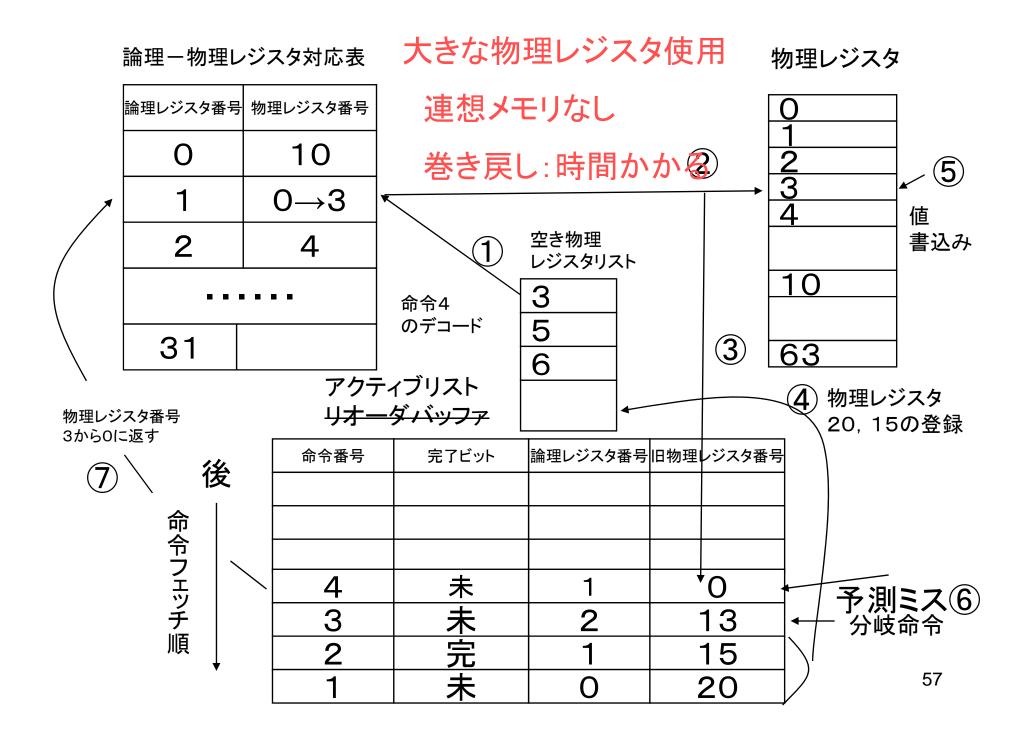

- ②大きな物理レジスタを利用する方法 (狭義のレジスタリネーミング法)

## ①リオーダバッファ法

#### 分岐予測:ミス リオーダバッファ 0以前すべて 終了 レジスタ 3以降の状態 O以前の状態 0終了 フェッチ順に 1終了 В 0と1の結果 R 2終了 2終了 予測ミス 4 無 効 3未了 5無効化 3未了 ボトム終了のとき、未 了直前まで書き込み 43

#### リオーダバッファの構成

後続命令

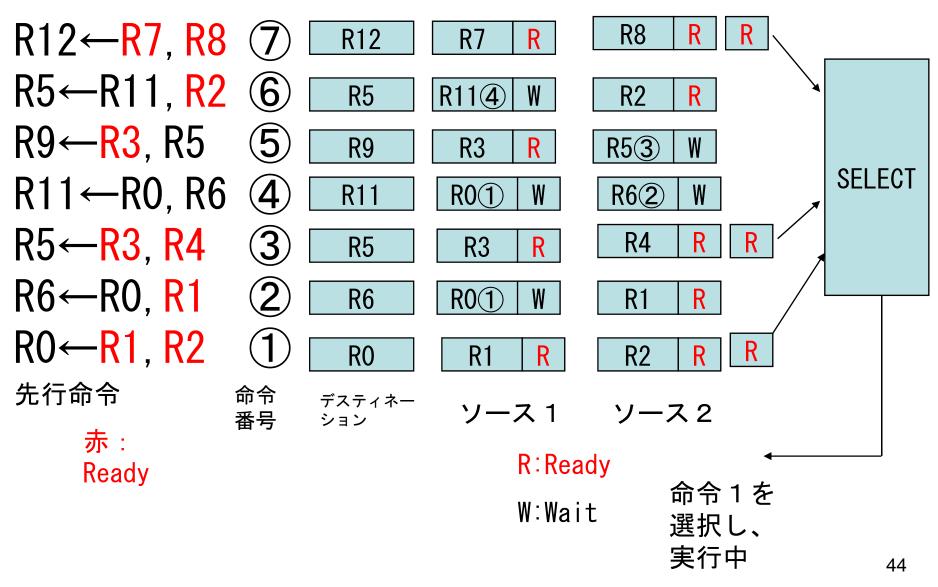

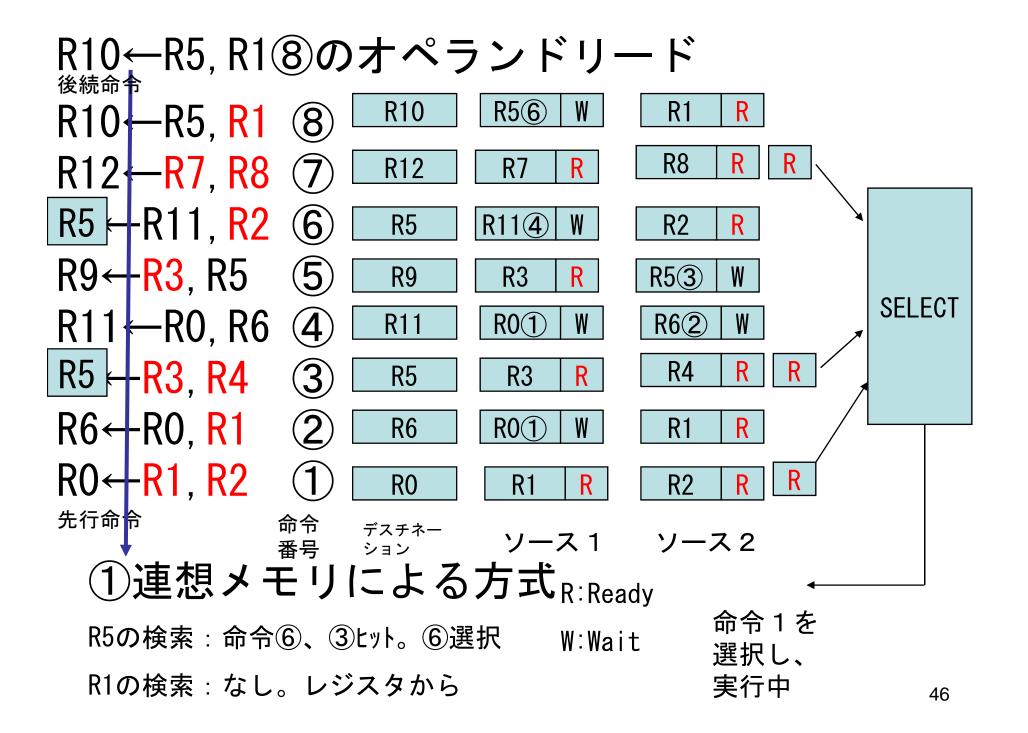

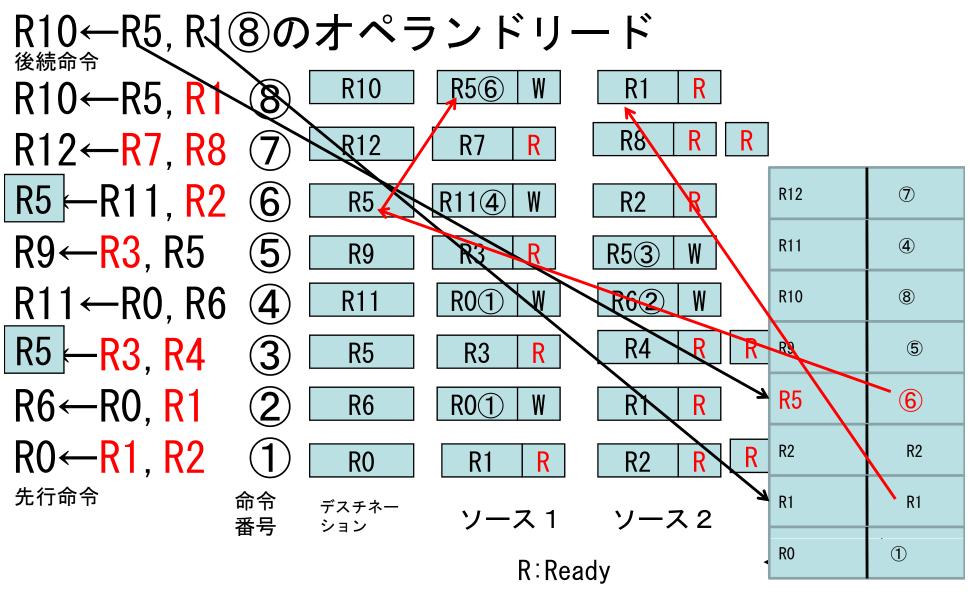

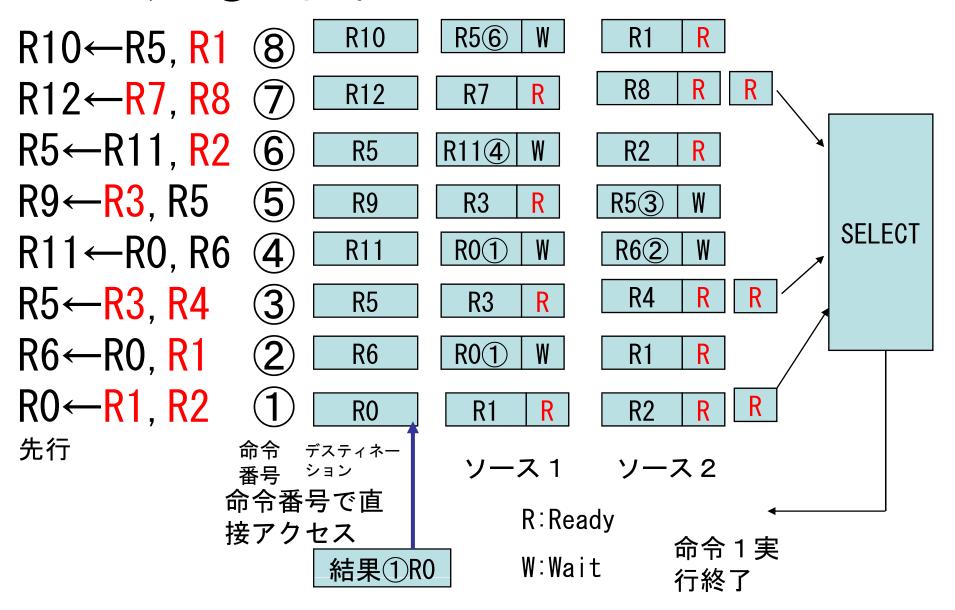

## オペランドリードの方法

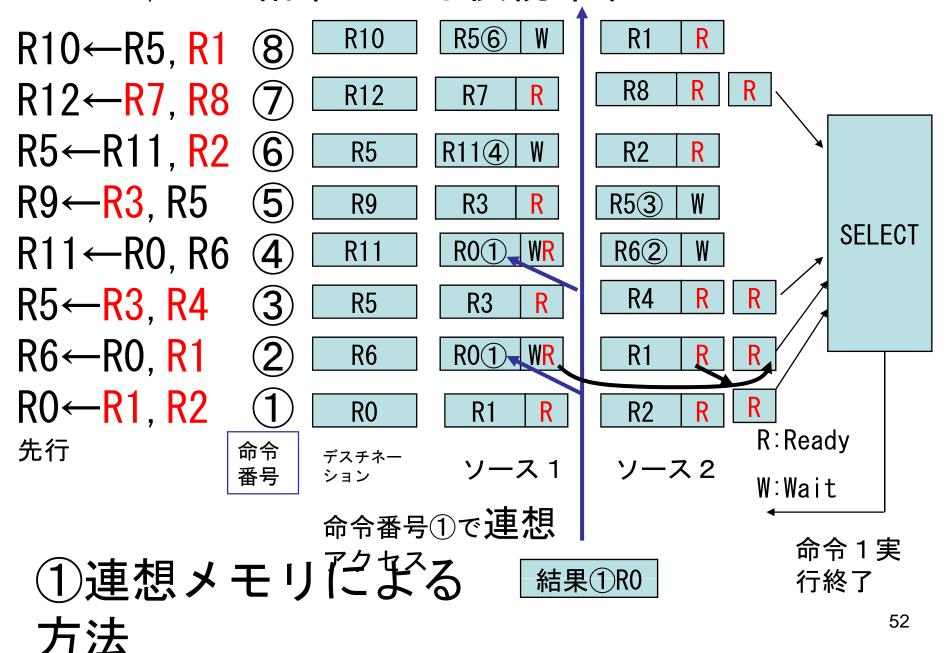

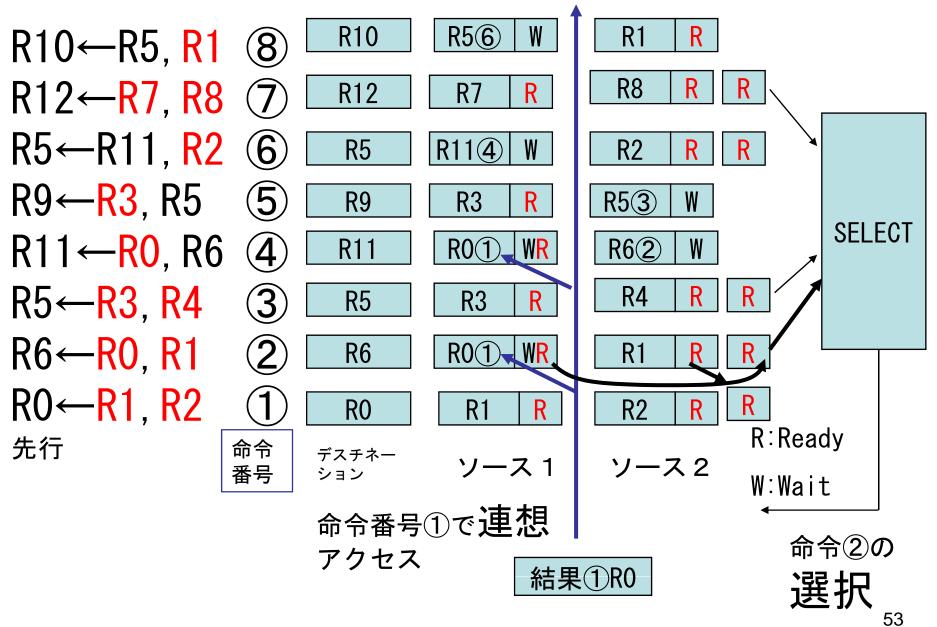

- ①連想メモリの方法

- ②レジスタと命令番号の対応表をとる 方法

- ③フーチャファイル

W:Wait

②レジスタと命令番号の対応表をとる方式

47

## ③フューチャファイル 命令番号:ダグ

と同様に高速

# 連想メモリの簡略化

リオーダバッファでの エントリ番号 \ 結果 レジスタ番号 命令番号 データ

レジスタ番号で直接アクセスし、命令番号比較

一致:書込み、不一致:破棄

**R31** 命令番号 データ R31 命令番号 R2 命令番号 データ 命令番号 R2 命令番号 R1 データ **R1** 命令番号 R0 命令番号 データ 命令番号 R0

レジスタ-命令 番号変換表

レジスタ

後続命令のWake-Up、リザベーションステーション:困難

## 結果のライトと次命令Wake-Up方法

- ①連想メモリを使用する方法

- ②依存行列テーブル法

#### R0←R1, R2①の結果のライト

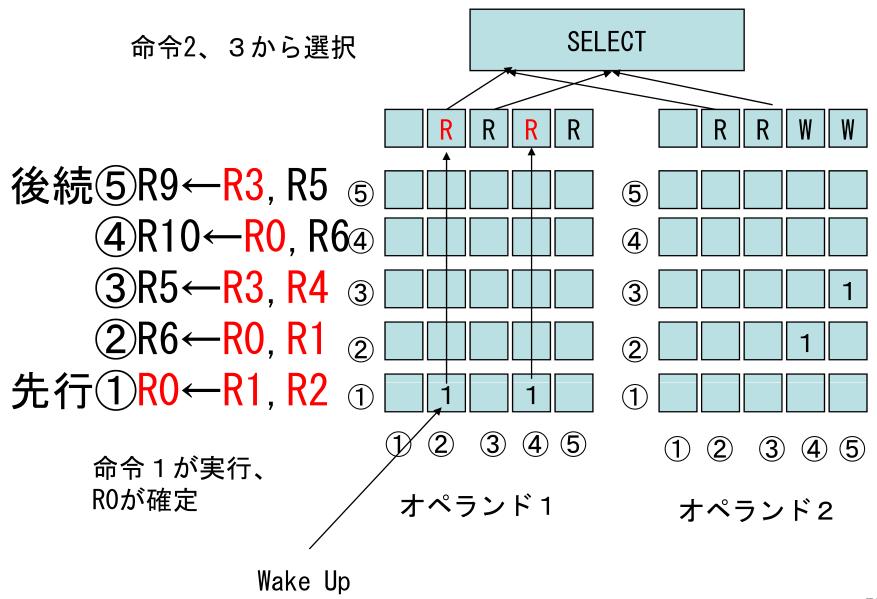

#### R0←R1, R2の結果による後続命令のWake-UP

#### R0←R1, R2の結果による後続命令のSelect

レジスタ-命令番号 ②依存行列テーブル (DMT) 法 変換表 命令番号④ R9 命令番号⑤ 命令1,3か **SELECT** ら1が選択 |命令番号② <u>R5 | 命令番号③</u> R R RO | 命令番号(1) 後続(5)R9←R3, R5 ⑤ **(5)** (4)R10←R0, R64 (3)R5←R3, R4 ③ (3) ②R6←R0, R1 先行(1)R0←R1, R2 ① 3 4 5 2 3 4 5 オペランド1 オペランド2 命令1の結果R0を オペランド1で使

用する命令番号

(1)

54

# ②大きな物理レジスタによる方式(狭義レジスタリネーミング方式)

| 命令番号 | 完了ビット  | 論理レジスタ番号 | 旧物理レジスタ番号 |

|------|--------|----------|-----------|

|      |        |          |           |

|      |        |          |           |

|      |        |          |           |

| 4    | 未      | 1        | 0         |

| 3    | 未      | 2        | 13        |

| 2    | 未<br>完 | 1        | 15        |

| 1    | 未      | 0        | 20        |

2

(3)

R1:物理3を利用

R1←R7, R8

後続

R1←R5, R6 ↑ R0←R3, R4

R0←R3, R4

ァ 先行 R1←R5, R6

②のROが順状態と なれば①のRO, R1は 必要なくなる

RO:物理10を利用

R1:物理Oを利用

1

RO:物理20を利用

R1:物理15を利用

58

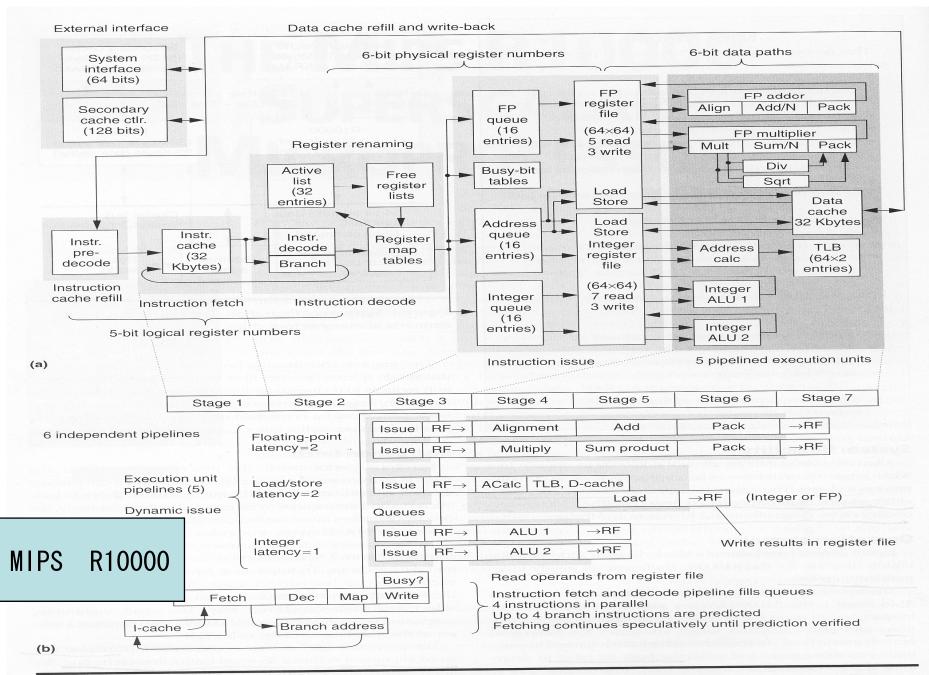

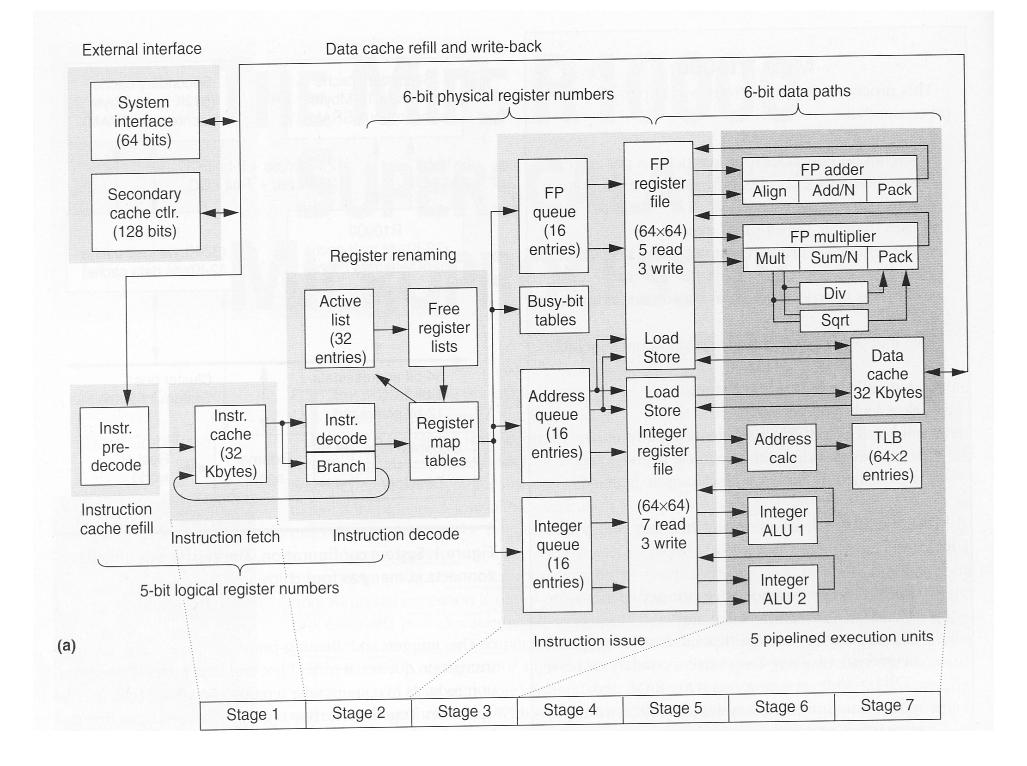

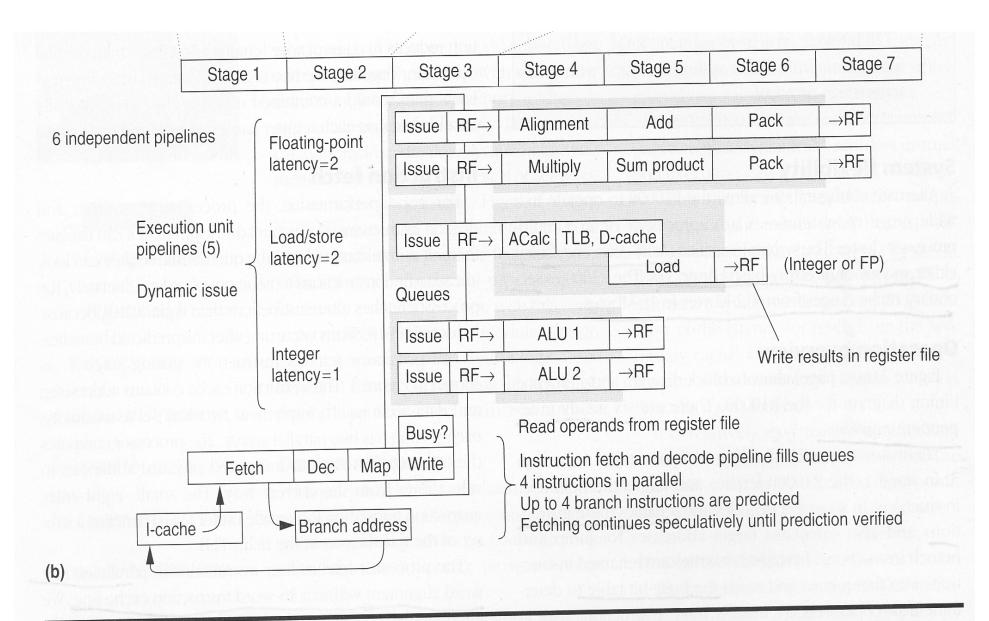

Figure 2. R10000 block diagram (a) and pipeline timing diagram (b). The block diagram shows pipeline stages left to right to correspond to pipeline timing.

| The block diagram shows pipeline stages left to right to correspond to pipeline timing.

Figure 2. R10000 block diagram (a) and pipeline timing diagram (b). The block diagram shows pipeline stages left to right to correspond to pipeline timing.

- 6.4スーパスカラ方式

- 6.4.1基本方式

- ①実行時での並列性検出

- ②互換性

- ③機械命令のビット使用率

- 順発行乱終了スーパスカラ方式のハードウェアの増加

- ①命令発行ネットワーク

- ②同時に読出し書込みのできるマルチポートレジスタ

- ③演算装置の多重化

- ④ロードストア装置の多重化とキャッシュメモリ強化 乱発行順終了(リオーダバッファ)

- ①リザベーションステーションでの待合わせ

- ②投機実行,正確な割込みのためのリオーダバップァ

(a) スーパスカラ方式での命令と演算装置の対応

```

DO 10 I=1, N

Z(I) = X(I) *Y(I)

IF (Z(I). EQ. 0) GOTO 20 (12)

10 CONTINUE

A=A+B

D=A*D

20

```

#### 順発行乱終了スカラ

```

(1)

LOAD IF D EX EX S

LOAD

IF D EX EX S

2

MULF

IF D - EX EX EX S

STORE

IF D

– – EX EX S

3

BRCZ

IF D

- EX S

(16)

ADD I

IF D

IFD - EXS

4

ADD I

IF D

BRCN

- - EX S

分岐予測

2回目の反復

ヒットでっ

IF D - -

EX EX S

LOAD

9

のバブル

IF D

LOAD

- - EX EX S

(10)

```

#### 順発行乱終了スーパスカラ

```

LOAD IF D EX EX S

(1)

LOAD IF D EX EX S

(2)

MULF

IF D - EX EX EX S

STORE

IF D - - - EX EX S

3

BRCZ

\mathsf{IF}\;\mathsf{D}\;-\;-\;-\;\mathsf{EX}\;\mathsf{S}

(15)

ADDI

\mathsf{IF} \mathsf{D} \mathsf{---} \mathsf{EX} \mathsf{S}

- IF D - - - EX S

4

ADD I

- IF D - - - EX S

BRCN

2回目の反復

- IF D - - - EX EX S

LOAD

9

LOAD

- IF D

– – – EX EX S

(10)

```

#### 乱発行乱終了スーパスカラ

```

LOAD IF D EX EX S

(1)

LOAD IF D EX EX S

2

MULF

IF D - EX EX EX S

IF D -

STORE

– – EX EX S

(3)

BRCZ

IF D EX - - S

IF D EX S

ADD I

(17)

4

ADD I

- IF D EX S

- IF D EX S

BRCN

2回目の反復

9

LOAD

EX EX S

- IF D

- IF D

(10)

LOAD

EX EX S

```

- 6. 4. 3初期のスーパスカラ方式 表6. 1

- 6.4.4 最新のマイクロプロセッサ 表6.2: Pentium4、Power4、UltraSparcIII

|                     |                | 表 6.1 初期の     | スーパスカラ方        | 式                  |                     |

|---------------------|----------------|---------------|----------------|--------------------|---------------------|

|                     | DECα<br>21064  | HP-PA<br>7100 | VR 4000        | Pentium            | Power PC<br>601     |

| トランジスタ数             | 168万           | 85万           | 130万           | 310万               | 280 万               |

| ピン数                 | 431            | 504           | 447            | 273                | 304                 |

| 電力                  | 30 W           | 23 W          | 10 W           | 16W                | 9.1W                |

| マシンサイクル             | 200 MHz        | 100MHz        | 50 MHz         | 66MHz              | 80 MHz              |

|                     |                |               | (内部 100 MH     | (z)                |                     |

| 命令長                 | 32 ビット         | 32 ビット        | 32 ビット         | 多様                 | 32 ビット              |

| パイプライン              |                |               |                |                    | 02 6 7 1            |

| 方式                  | スーパスカラ         | スーパスカラ        | スーパ            | スーパスカラ             | スーパスカラ              |

| 多重度                 | 2 多重           | 2 多重          | パイプライン         | 12                 | 3 多重                |

| ステージ数               |                |               |                |                    |                     |

| 整数                  | 7              | 5             | 8              | 5                  | 4                   |

| 浮動小数点               | 10             | 8             | ?              | 8                  | 6                   |

| 内蔵キャッシュ(フ           | アーストキャッ        | <b>ッシュ</b> )  |                |                    |                     |

| 命令                  | 8KB            | なし            | 8KB            | 8KB                | 統合                  |

| データ                 | 8KB            | なし            | 8KB            | 8KB                | 32 KB               |

| 方式                  | ダイレクト<br>マッピング |               | ダイレクト<br>マッピング | 2ウェイセット<br>アソシアティブ | 8 ウェイセット<br>アソシアティブ |

|                     | ストアスルー         |               | ストアイン          | ストアイン              | ストアイン               |

|                     | 実アドレス・         |               | 仮想・実           | ?                  | 実アドレス               |

| Santa are seen best |                |               | アドレス混合         |                    |                     |

| TLBエントリ数            | 40             | 136           | 48             | 96                 | 280                 |

| 分岐                  | 分岐予測           | 遅延分岐          | 遅延分岐           | 分岐予測               | 分岐予測                |

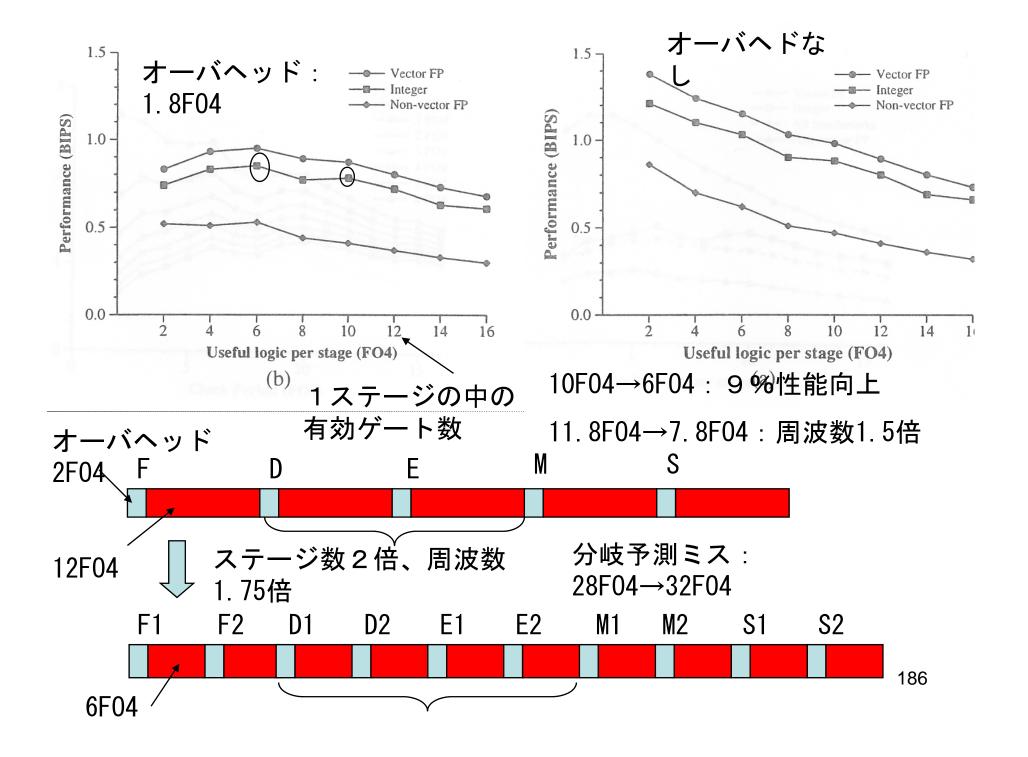

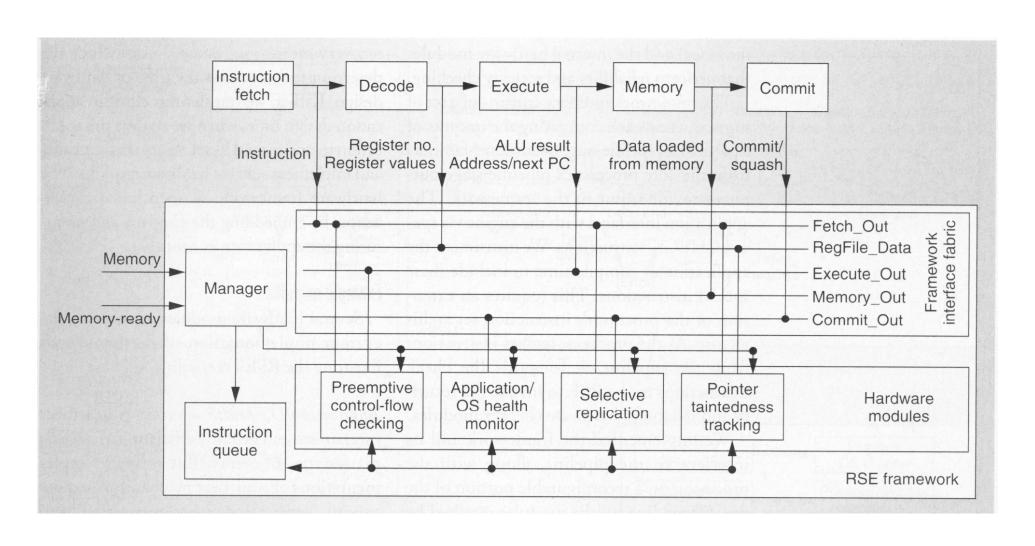

#### 深/浅パイプライン

深:ステージ機能低い, 周波数高

浅:ステージ機能高い、周波数低

Pentium III : 10段, 1GHz

Pentium 4 : 20段, 1.5GHz

性能: 1. 2倍

## 12 高性能マイクロプロセッサの現状

| モデル名     | 21264    | Pentium4   | UltraSPARCIII | Power4    |

|----------|----------|------------|---------------|-----------|

| 発表年      | 1998     | 2000       | 2001          | 2001      |

| デザインルール  | 0. 35 μm | 0. 18 μm   | 0. 18 μm      | 0. 18 μm  |

| Tr数      | 1520万    | 4200万      | 2900万         | 17000万    |

| ピン数      | 587      | 478        | 1368          | 2200      |

| 配線層      | 6        | 6          | 6             | 7         |

| 周波数      | 600MHz   | 1. 4GHz    | 900MHz        | 1. 3 GH z |

| 電力       | 6 0 W    | 5 5 W      | 7 0 W         | 5 0 W     |

| プロセッサ数   | 1        | 1          | 1             | 2         |

| パイプライン   |          |            |               |           |

| 命令フェッチ   | 4多重      | 3多重        | 4多重           | 8多重       |

| 基本ステージ数  | 7        | 20         | 14            | 15        |

| 演算器個数    |          |            |               |           |

| 整数       | 4        | 4          | 2             | 2         |

| 浮動       | 2        | 1          | 2             | 2         |

| ロードストア   | 2        | 2          | 1             | 2         |

| 命令発行     | リネーミング   | リネーミング     | フューチャ         | リネーミンング   |

|          | レジスタ     | レジスタ       | ファイル          | レジスタ      |

|          | Sax Sax  |            | (スコアボード)      |           |

|          | 乱発行同時終了  | 乱発行同時終了    | 乱発行同時終了       | 乱発行同時終了   |

| リオーダバッファ | 8 0 命令   | 126命令      | ?             | 200命令     |

| 11ラーコンド  | 敷粉・80個   | 合計128個     | ?             | 80個       |

| リネーミング   | 正然.00回   | DILL TO OF |               | OUNE      |

| 分岐予測        |         |          |          |               |

|-------------|---------|----------|----------|---------------|

| 方式          | ハイブリッド  | ハイブリッド?  | 大域       | ハイブリッド        |

| 予測テーブル容量    | 29Kビット  | 32Kビット   | 32Kビット   | 48Kエントリ       |

|             | 局所2レベル通 | 適応       | 2レベル適応   | 局所: 16Kエントリ   |

|             | 大域2ビット  |          | (Gshare) | 大域:16Kエントリ    |

|             | カウンタ    |          | 16Kエントリ  | 上記選択:16Kエントリ  |

|             |         |          | 2ビットカウン  | <del>9</del>  |

| 1次キャッシュ     |         |          |          |               |

| 命令          | 6 4 KB  | トレースキャッ  | 3 2 KB   | 6 4 KB        |

|             |         | シュ12Kμ命令 |          |               |

|             | 2ウェイ    | 8ウェイ     | 4ウェイ     | ダイレクトマップ      |

| データ         | 6 4 KB  | 8 KB     | 6 4 KB   | 3 2 KB        |

|             | 2ウェイ    | 4ウェイ     | 4ウェイ     | 2ウェイ          |

|             | ストアイン   | ストアスルー   | ストアスルー   | ストアスルー        |

| 2次キャッシュ     | 1 6 MB  | 2 5 6 KB | 8MB      | 1.5MB         |

|             | オフチップ   | オンチップ    | オフチップ    | オンチップ         |

|             | 統合,     | 統合, 8ウェイ | 統合,      | 統合, 8ウェイ,     |

|             | ダイレクト   | ストアイン    | ダイレクト    | ストアイン,        |

|             | マップ     |          | マップ      | スヌープコントローラ    |

|             |         |          |          | (2台のプロセッサで共有) |

| 性能          |         |          |          |               |

| 測定時周波数      | 1 GHz   | 2GHz     | 900MHz   | 1. 3 GHz      |

| SPECint2000 | 6 2 1   | 6 4 0    | 4 3 8    | 7 9 0         |

| SPECfp2000  | 776     | 7 0 4    | 427      | 1098          |

#### CHART WATCH: WORKSTATION PROCESSORS

| Processor Alpha AMD<br>21264C Athlon X |                    | AMD<br>Athlon XP | HP<br>PA-8700      | IBM<br>Power4        | Intel<br>Itanium     | Intel<br>Itanium 2   | Intel<br>Xeon      | MIPS<br>R14000     | Sun<br>Ultra-III   |  |

|----------------------------------------|--------------------|------------------|--------------------|----------------------|----------------------|----------------------|--------------------|--------------------|--------------------|--|

| Clock Rate                             | 1,001MHz           | 1,800MHz         | 750MHz             | 1,300MHz             | 800MHz               | 1,000MHz             | 2,530MHz           | 600MHz             | 1,050MHz           |  |

| Cache<br>(I/D/L2/L3)                   | 64K/64K            | 64K/64K/<br>256K | 750K/<br>1.5M      | 64K/32K/<br>1.5MB    | 16K/16K/96K          | 16K/16K/256<br>K/ 3M | 12K/8K/<br>512K    | 32K/32K            | 32K/64K            |  |

| Issue Rate                             | 4 issue            | 3 x86 instr      | 4 issue            | 8 issue              | 6 issue 8 Issue      |                      | 3 ROPs             | 4 issue            | 4 issue            |  |

| Pipeline Stages                        | 7/9 stages         | 9/11 stages      | 7/9 stages         | 12/17 stages         | 10 stages            | 8 stages             | 22/24 stages       | 6 stages           | 14/15 stages       |  |

| Out of Order                           | 80 instr           | 72ROPs           | 56 instr           | 200 instr            | None                 | None                 | 126 ROPs           | 48 instr           | None               |  |

| Rename Regs                            | 48/41              | 36/36            | 56 total           | 48/40                | 328 total            | 328 total            | 128 total          | 32/32              | None               |  |

| BHT Entries                            | 4K x 9-bit         | 4K x 2-bit       | 2K x 2-bit         | 3 x 16K x 1-bit      | 512 x 2-bit          | 512 x 2-bit          | 4K x 2-bit         | 2K x 2-bit         | 16K x 2-bit        |  |

| TLB Entries                            | 128/128            | 280/288          | 240 unified        | 1,024 unified        | 64I/32L1D/<br>96L2D  |                      |                    | 64 unified         | 128I/512D          |  |

| Memory B/W                             | 8GB/s              | 2.1GB/s          | 1.54GB/s           | 12.8GB/s             | 2.1GB/s              | 6.4GB/s              | 3.2GB/s            | 539 MB/s           | 4.8GB/s            |  |

| Package                                | CPGA-588           | PGA-462          | LGA-544            | MCM                  | PAC-418              | mPGA-700             | PGA-423            | CPGA-527           | FC-LGA 1368        |  |

| IC Process                             | 0.18µ 6M           | 0.13µ 6M         | 0.18µ 7M           | 0.18µ 7m             | 0.18µ 6M             | 0.18µ 6M             | 0.13µ 6M           | 0.25µ 4M           | 0.15µ.7M           |  |

| Die Size                               | 115mm <sup>2</sup> | 80mm²            | 304mm <sup>2</sup> | 400mm <sup>2**</sup> | 300mm <sup>2</sup> * | 400mm <sup>2</sup> * | 131mm <sup>2</sup> | 204mm <sup>2</sup> | 210mm <sup>2</sup> |  |

| Transistors                            | 15.4 million       | 37.5 million     | 130 million        | 174 million**        | 25 million           | 221 million          | 55 million         | 7.2 million        | 29 million         |  |

| Est Die Cost                           | \$28*              | \$16*            | \$96*              | \$144**              | \$116*               | \$139*               | \$23*              | \$76*              | \$72*              |  |

| Power (Max)                            | 95W*               | 67W(MTP)         | 75W*               | 135W**               | 130W                 | 130W                 | 59W(TDP)           | 30W*               | 75W*               |  |

| Availability                           | 3Q01               | 2Q02             | 4Q01               | 4Q01                 | 2Q01                 | 3Q02                 | 2002               | 1002               | 1Q02               |  |

Source: vendors, except \*MDR estimates. Estimated manufacturing costs does not include external cache chips. \*\* Contains two processors on one die.

The table above gives the vital statistics for the key high-end processors available. The table below provides the best reported SPEC CPU2000 (base) results for each shipping processor.

| Processor                | Alpha<br>21264C       | AMD<br>Athlon XP | HP<br>PA-8700    | IBM<br>Power 4       | Intel<br>Itanium | Intel<br>Itanium 2 | Intel<br>Xeon     | MIPS<br>R14000 | Sun<br>UltraSPARC III |

|--------------------------|-----------------------|------------------|------------------|----------------------|------------------|--------------------|-------------------|----------------|-----------------------|

| System or<br>Motherboard | Alpha ES40<br>Model 6 | Epox<br>BKHA+    | HP9000<br>rp7400 | pSeries<br>690 Turbo | HP<br>12000      | HP<br>RX2600       | Dell<br>Prec. 340 | SGI 3200       | Sun<br>Blade 2050     |

| Clock Rate               | 1,001MHz              | 1.8GHz           | 750MHz           | 1,300MHz             | 800MHz           | 1,000MHz           | 2,530MHz          | 600MHz         | 1,050MHz              |

| External Cache           | 8MB                   | None             | None             | 128MB                | 4MB              | None               | None              | 8MB            | 8MB                   |

| 164.gzip                 | 463                   | 903              | 495              | 563                  | 332              | 583                | 911               | 322            | 433                   |

| 175.vpr                  | 534                   | 448              | 550              | 718                  | 376              | 704                | 511               | 572            | 460                   |

| 176.gcc                  | 693                   | 504              | 710              | 788                  | 407              | 1,014              | 1,058             | 445            | 577                   |

| 181.mcf                  | 550                   | 346              | 396              | 1,087                | 402              | 834                | 625               | 783            | 659                   |

| 186.crafty               | 816                   | 1,059            | 642              | 673                  | 356              | 781                | 860               | 502            | 558                   |

| 197.parser               | 418                   | 674              | 427              | 445                  | 296              | 660                | 883               | 409            | 488                   |

| 252.eon                  | 799                   | 1,452            | 508              | 985                  | 370              | 1,004              | 1,162             | 507            | 527                   |

| 253.peribmk              | 635                   | 1,094            | 510              | 694                  | 320              | 875                | 1,171             | 367            | 540                   |

| 254.gap                  | 454                   | 844              | 242              | 746                  | 256              | 680                | 1,130             | 30B            | 372                   |

| 255.vortex               | 844                   | 1,157            | 930              | 1,246                | 459              | 1,193              | 1,338             | 679            | 738                   |

| 256.bzip2                | 656                   | 593              | 411              | B68                  | 334              | 759                | 709               | 493            | 629                   |

| 300.twolf                | 795                   | 568              | 781              | 1,027                | 449              | 880                | 750               | 645            | 570                   |

| SPECint_base2000         | 621                   | 738              | 520              | 790                  | 358              | 810                | 893               | 483            | 537                   |

| 168.wupside              | 660                   | 928              | 333              | 1,570                | 591*             | 1,003              | 1,234             | 434            | 659                   |

| 171.swim                 | 1502                  | 840              | 790              | 1,493                | 1,369*           | 3,205              | 1,425             | 529            | 980                   |

| 172.mgrid                | 517                   | 551              | 469              | 726                  | 749*             | 1,720              | 845               | 379            | 487                   |

| 173.applu                | 741                   | 575              | 591              | 960                  | 1,022*           | 2,033              | 939               | 381            | 310                   |

| 177.mesa                 | 800                   | 968              | 570              | 665                  | 329*             | 642                | 1,043             | 425            | 543                   |

| 178.galgel               | 1638                  | 578              | 1,374            | 2,637                | 1,019*           | 2,505              | 1,133             | 1,398          | 1,713                 |

| 179.art                  | 1782                  | 431              | 500              | 1,703                | 2,369*           | 4,226              | 586               | 1,436          | 9,389                 |

| 183.equake               | 332                   | 574              | 239              | 1,696                | 834*             | 1,871              | 903               | 347            | 645                   |

| 187.facerec              | 1024                  | 757              | 334              | 1,310                | 637*             | 1,152              | 1,134             | 647            | 958                   |

| 188.ammp                 | 592                   | 477              | 472              | 751                  | 511*             | 788                | 563               | 573            | 509                   |

| 189.lucas                | 891                   | 666              | 300              | 1,124                | 837*             | 1,206              | 1,155             | 442            | 371                   |

| 191.fma3d                | 703                   | 711              | 273              | 855                  | 323*             | 747                | 806               | 306            | 400                   |

| 200.sixtrack             | 401                   | 456              | 407              | 505                  | 575*             | 894                | 459               | 298            | 366                   |

| 301.aspi                 | 641                   | 504              | 591              | 940                  | 350*             | 678                | 684               | 406            | 471                   |

| SPECfp_base2000          | 776                   | 624              | 464              | 1,098                | 703*             | 1,356              | 878               | 499            | 701                   |

\*Dell PowerEdge 7150 with 4MB L3 cache

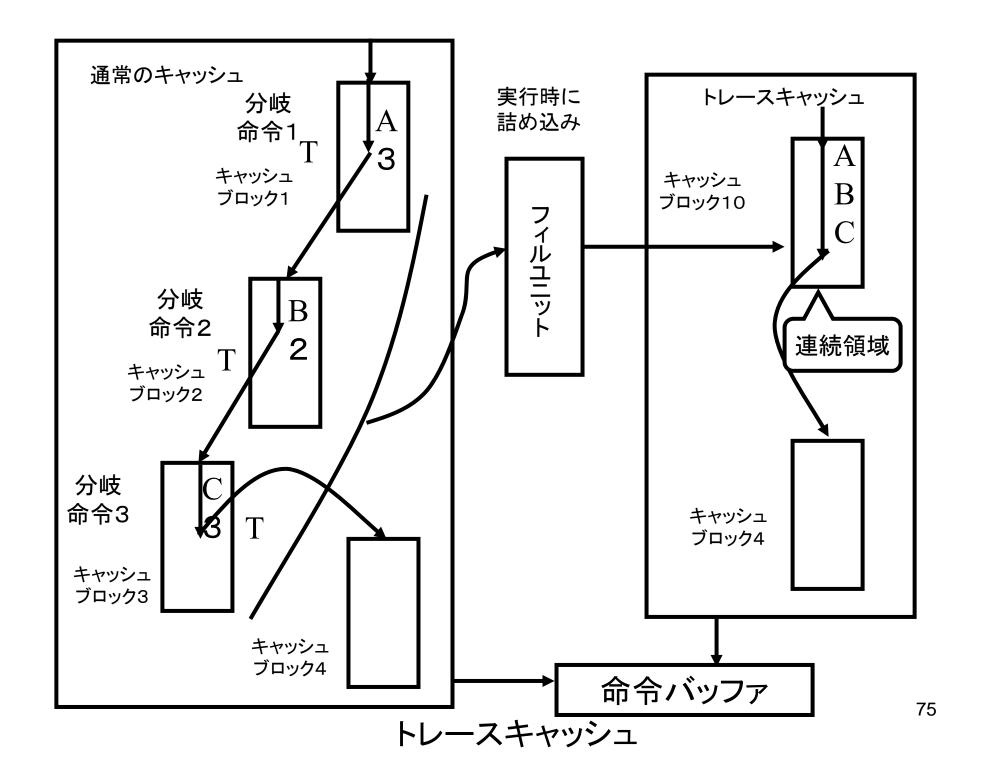

## トレースキャッシュ

Pentium4で採用 通常の キャツ シュブ トレースキャッシュ BRブロック ロック 予測側 Taken NotTaken

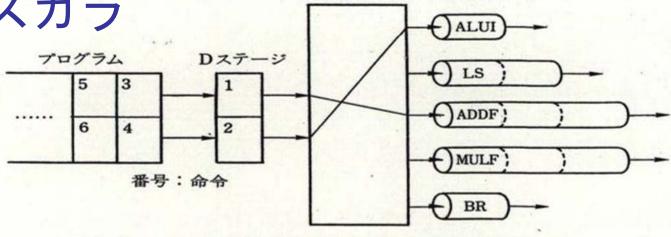

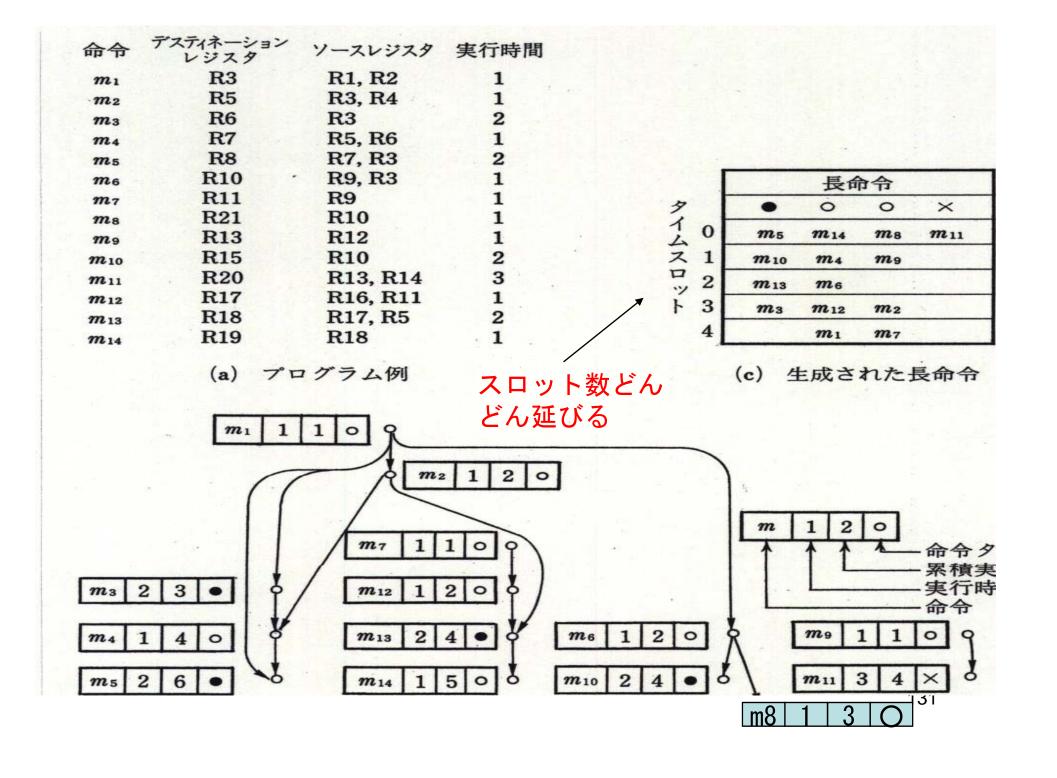

## 6.5V L I Wプロセッサ

- (1) VLIW方式の特徴

- ①コンパイル時の並列性検出

- ②シンプルなハードウェア構成

- ③機械命令のビット使用率の低下

- 4目的コードレベルでの非互換性

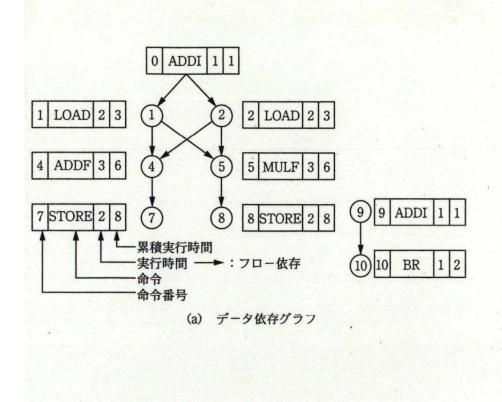

- (2) プログラムの実行例

プログラムの実行例

ロードストア装置2、整数演算装置2、浮動 小数点加算装置1、

浮動小数点乗算装置1、分岐装置1とし、遅延分岐を採用

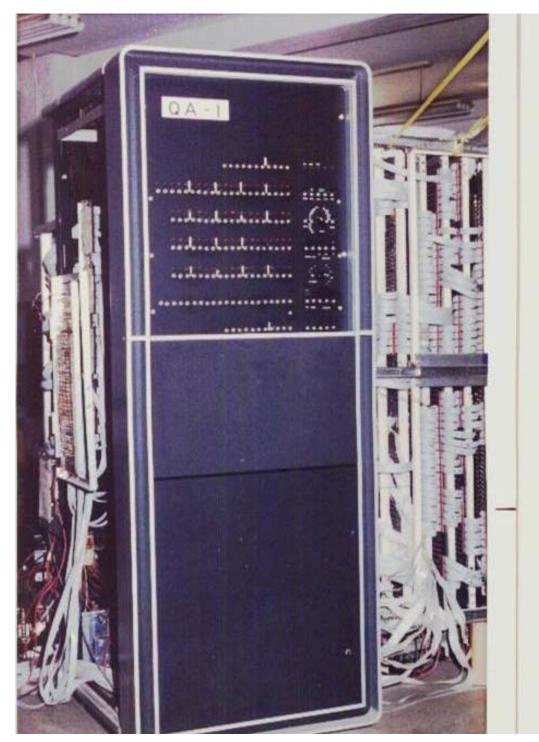

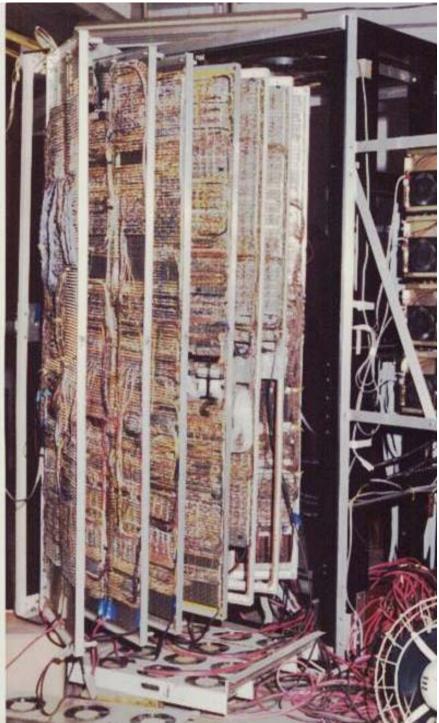

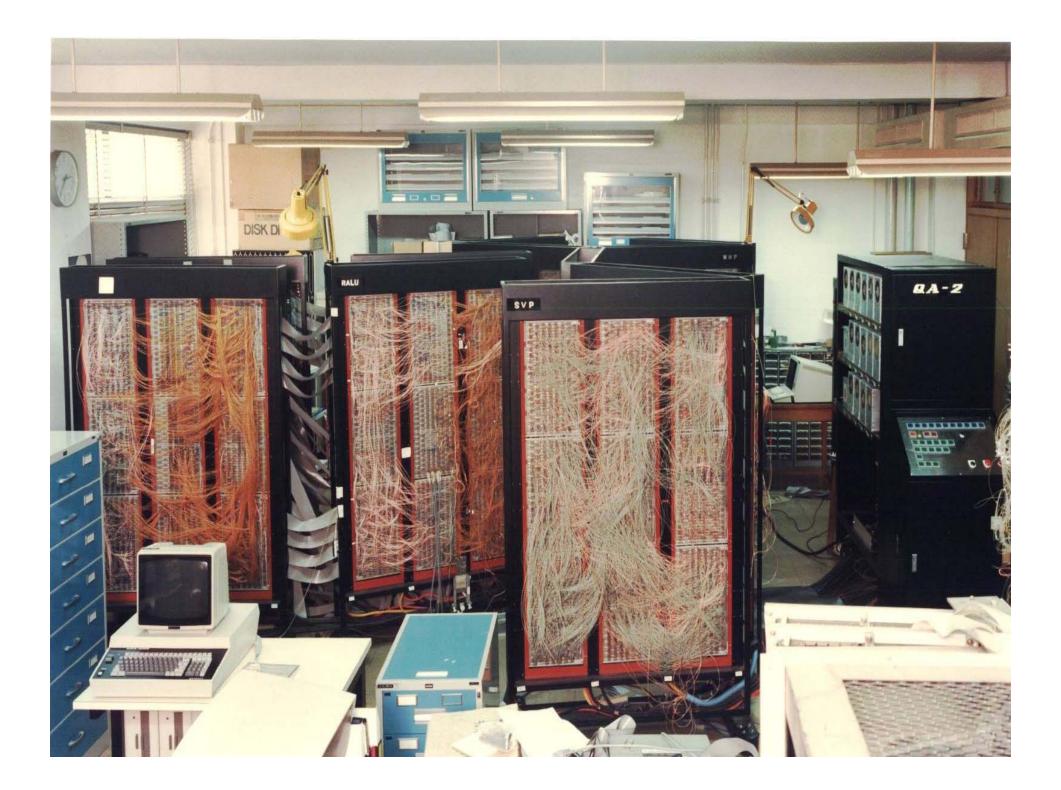

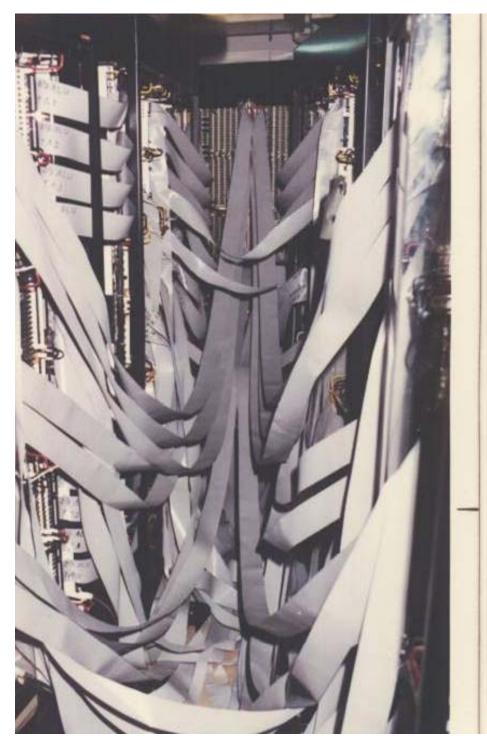

# 1970/1980年代のVLIW方式 VLIWの命名者 J. Fisher、1983年

1976年:AP-120B、QA-1/2

1987年: ELI-512、Trace、Cydra

番号:長命令

(b) VLIW 方式での命令と演算装置の対応

ALUI:整数, LS:ロードストア, ADDF:浮動小数点加算,

MULF:浮動小数点乗算, BR:分岐

スーパスカラ/VLIW での命令と演算装置の対応

LS:2サイクル

ADDF:3サイクル

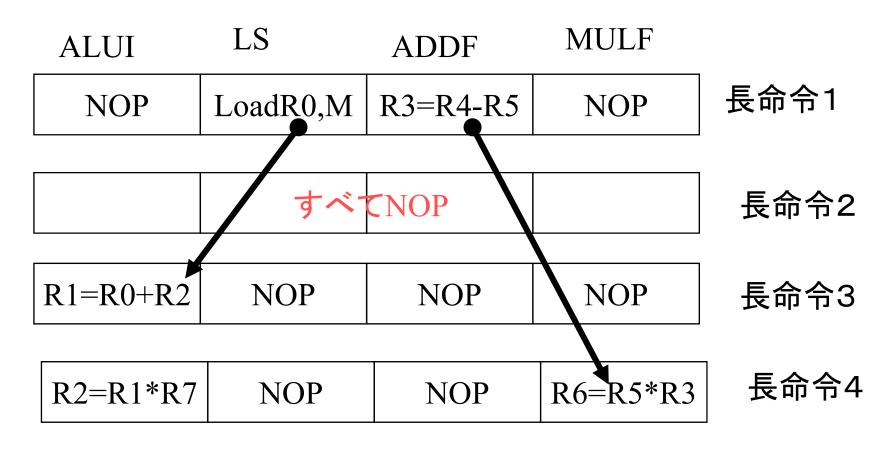

## 長命令間および内でのNOP

#### ソースプログラム

```

目的コード

LOAD R1 M(R10+D1)

LOAD R2 M(R10+D2)

ADDF R3 R1 R2

MULF R4 R1 R2

ADDI R10 #11

(20)

ADDI R11 #11

STORE M(R10+D3) R3

STORE M(R10+D4) R4

BRCN M(PC-18) Lに分岐

```

## VLIW命令での実行

```

1 LOAD IF D EX EX S

LOAD IF D EX EX S

```

② すべてNOP

```

3 ADDF IF D EX EX EX S

MULF IF D EX EX EX S

ADDI IF D EX S (21)

ADDI IF D EX S

```

- ④ すべてNOP

- ⑤ すべてNOP

- 6 STORE IF D EX EX S STORE IF D EX EX S BRCN IF D EX S

- ⑦ LOADIF D EX EX S 遅延スロットの実行LOADIF D EX EX S (2回目の反復)

- ⑧ すべてNOP 遅延スロットの実行

#### これを先の乱発行乱終了スカラで行うと、

```

LOAD IF D EX EX S

LOAD

IF D EX EX S

ADDF

IF D - EX EX EX S

MULF

IF D - EX EX EX S

ADD I

IF D EX S

ADD I

IF D EX S

STORE

IF D EX EX S (22)

STORE

IF D EX EX S

BRCN

IF D EX S

2回目の反復

LOAD

IF D EX EX S

LOAD

IF D EX EX S

```

#### スーパスカラでは

```

LOAD IF D EX EX S

LOAD IF D EX EX S

IF D - EX EX EX S

ADDF

IF D - EX EX EX S

MULF

ADD I

IF D EX S

IF D EX S

ADDI

(23)

STORE

IF D - - EX EX S

STORE

IFD - - EXEXS

BRCN

IF D EX S

2回目の反復

IF D EX EX S

LOAD

LOAD

IF D EX EX S

```

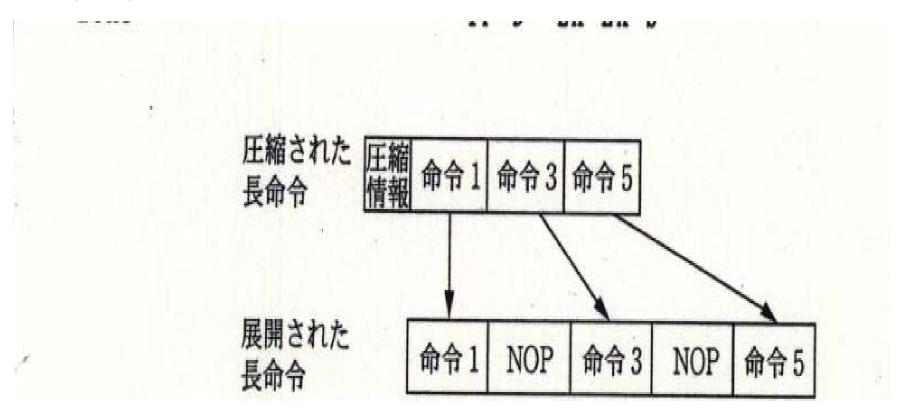

# 6.5.2 VLIW方式の改良(1)全NOP命令の削除

## (2)長命令の圧縮

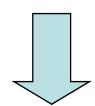

#### (3) 分岐命令の高速処理

分岐成立/不成立側の同時実行 ブースティングと遅延例外処理 プレディケート付き演算 ソフトウェアパイプライン支援

Itaniumのアーキテクチャ

T:チェック先の論理値1

ならチェック結果1

F:チェック先の論理値O

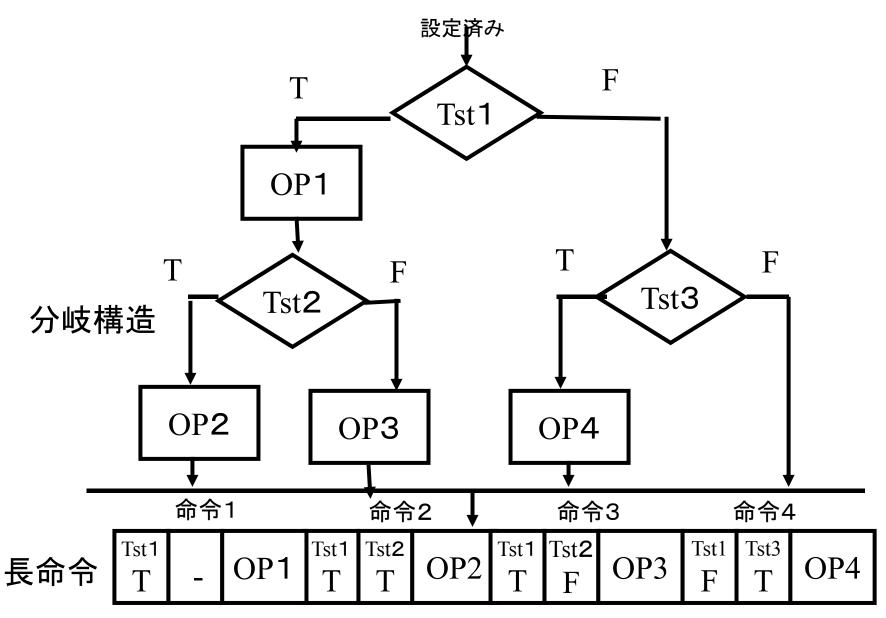

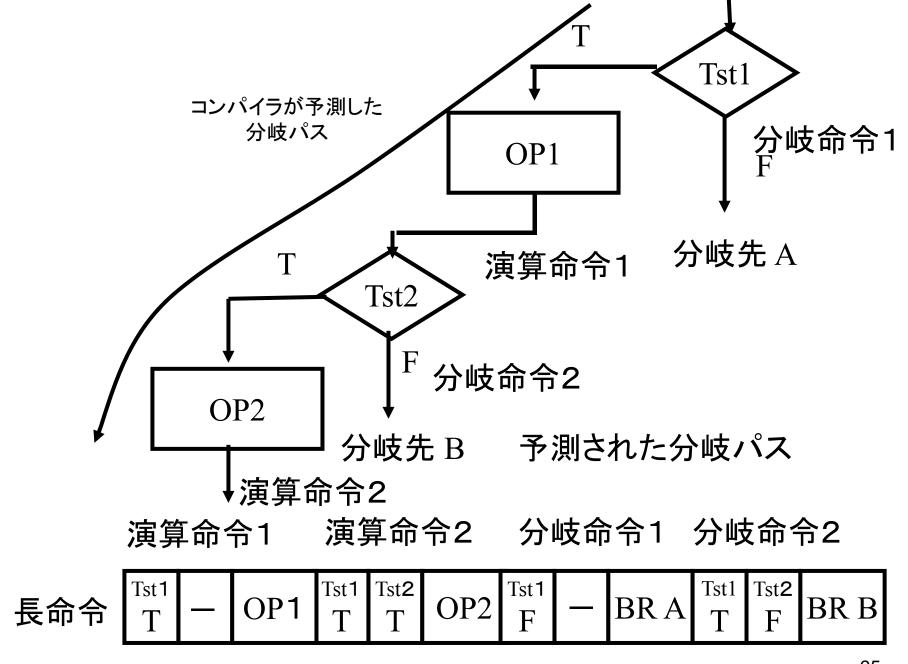

ならチェック結果1

3 6.13 VLIW 方式の分岐高速化機構

Tst1, Tst2, Tst3

複雑な分岐構造を1つの長命令に埋め込める

多数の長命令のフェッチがなくなる 長命令のビット使用効率が向上する

共有命令パイプライン方式

```

(1)マルチスレッドVLIW方式

スレッド1

LOAD IF D EX EX S

DCN=1

LOAD IF D EX EX S

スレッド2

(2)

LOAD IF D EX EX S

DCN=1

LOAD IF D EX EX S

スレッド1

IF D EX EX EX S

3

ADDF

DCN=0

MULF

IF D EX EX EX S

ADDI

IF D EX S

DCN=2

IF D EX S

ADD I

98

スレッド2

(24)

```

| 4          | ADDF  | ΙF | D  | EX | EX | EX | S  |   | DCN=0 |

|------------|-------|----|----|----|----|----|----|---|-------|

|            | MULF  | IF | D  | EX | EX | EX | S  |   |       |

|            | ADD I | IF | D  | EX | S  |    |    |   | DCN=2 |

|            | ADDI  | IF | D  | EX | S  |    |    |   |       |

|            | スレッド3 |    |    |    |    |    |    |   |       |

| <b>(5)</b> | LOAD  |    | ΙF | D  | EX | EX | S  |   | DCN=1 |

|            | LOAD  |    | IF | D  | EX | EX | S  |   |       |

|            | スレッド1 |    |    |    |    |    |    |   |       |

| <b>6</b>   | STORE |    |    | IF | D  | EX | EX | S | DCN=2 |

|            | STORE |    |    | IF | D  | EX | EX | S |       |

|            | BRCN  |    |    | IF | D  | EX | S  |   |       |

スレッド2

(7) STORE

IF D EX EX S

DCN=2

**STORE**

**BRCN**

スレッド1

IF D EX EX S

IF D EX S

8 LOAD

LOAD

2回目の反復

IF D EX EX S

DCN=1

IF D EX EX S

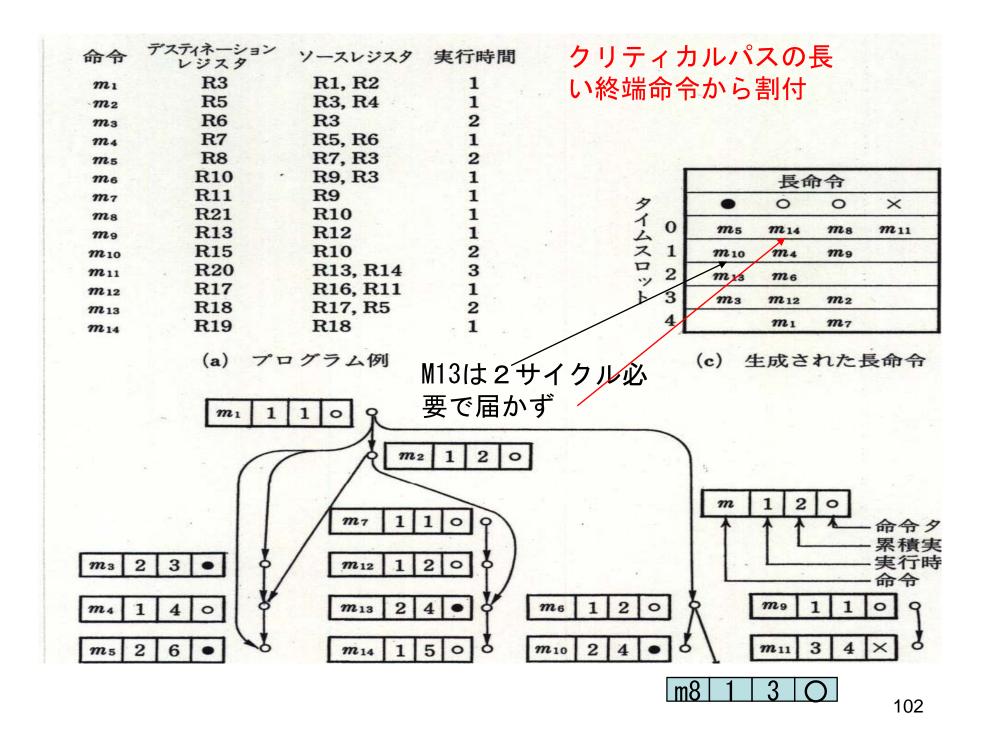

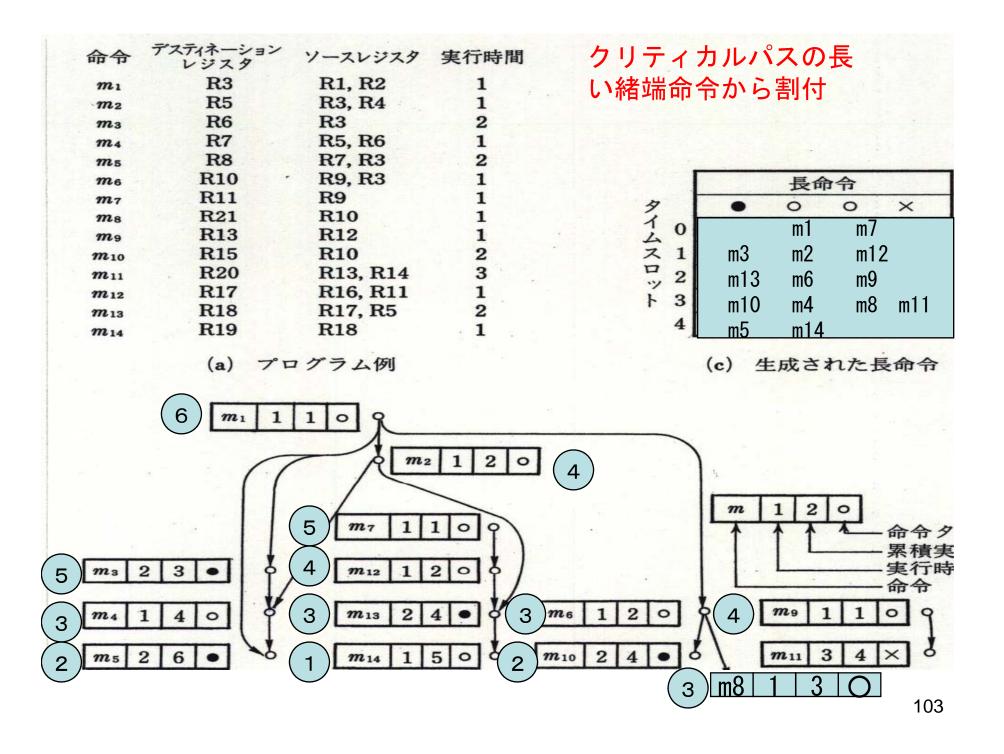

リストスケジューリング

- ①基本ブロック内のデータ依存グラフの作成

- ②クリティカルパスの決定

- ③リストスケージューリング

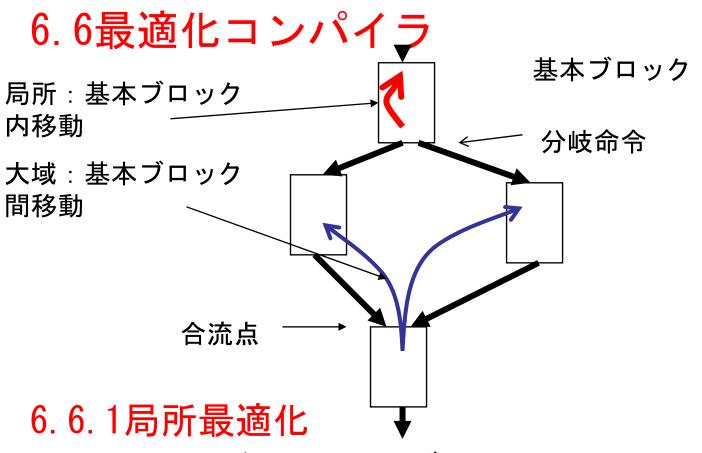

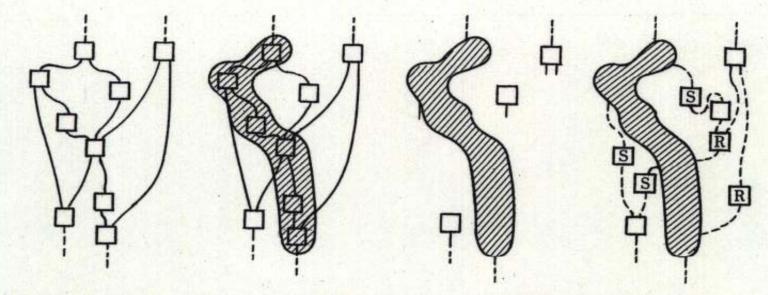

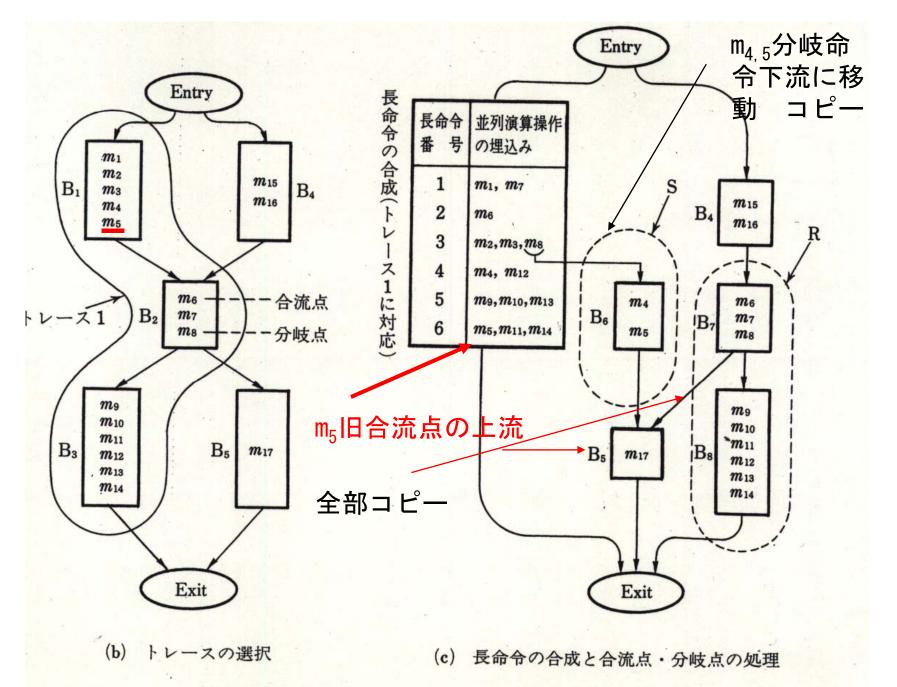

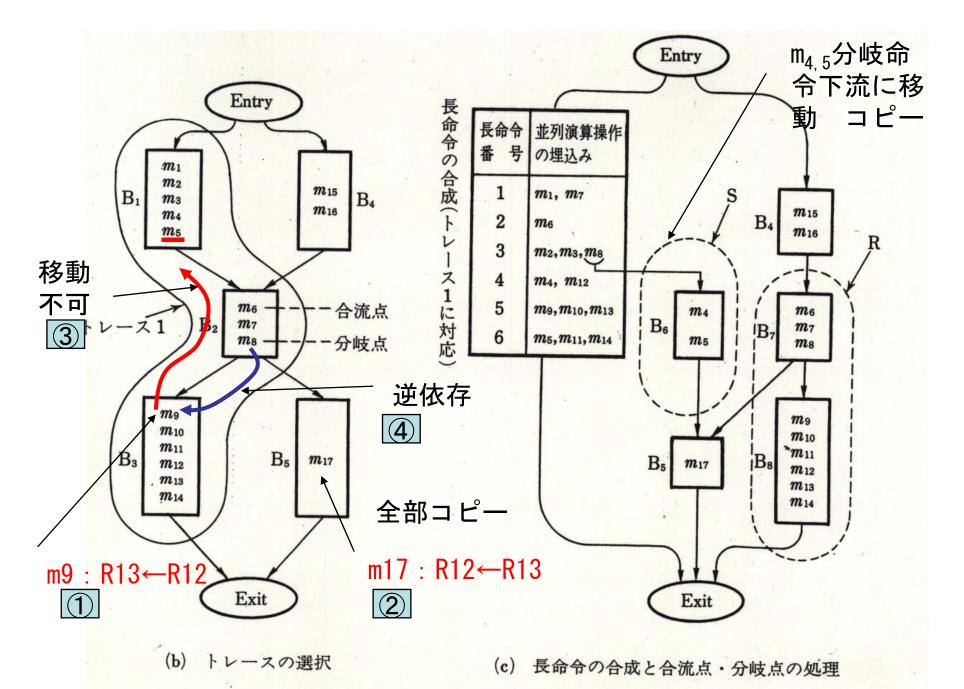

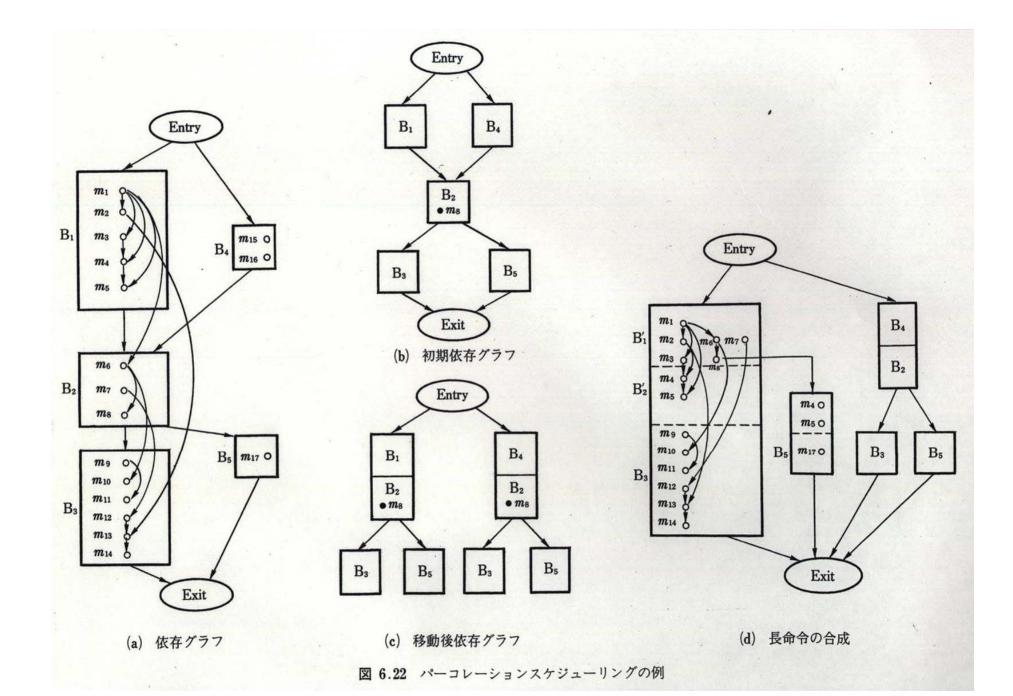

#### 6.5.2広域最適化

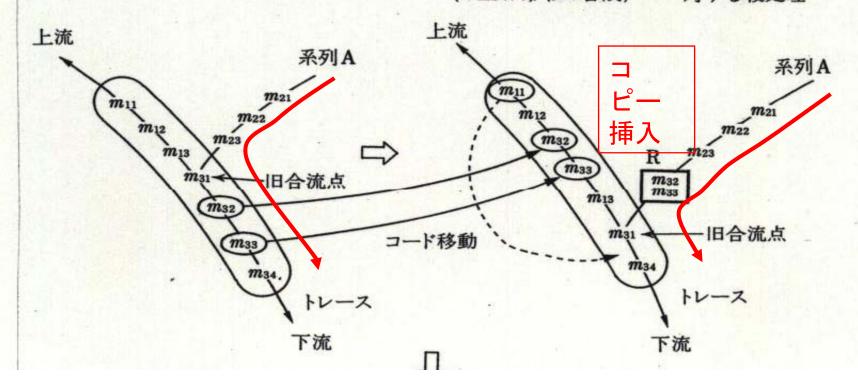

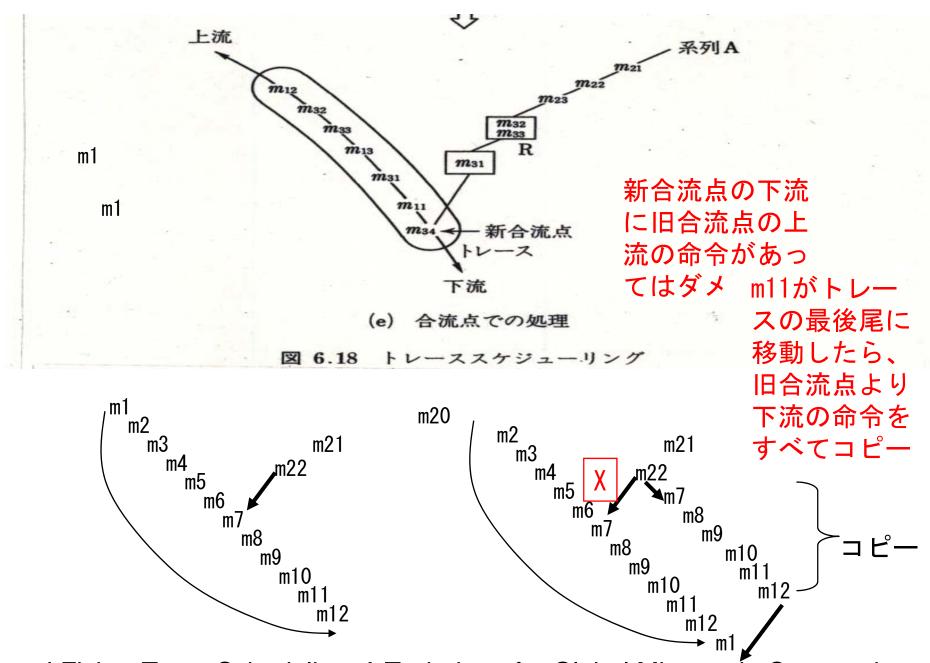

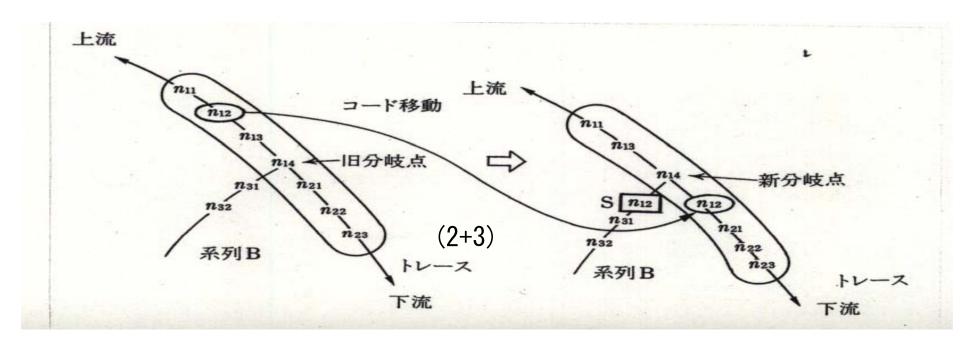

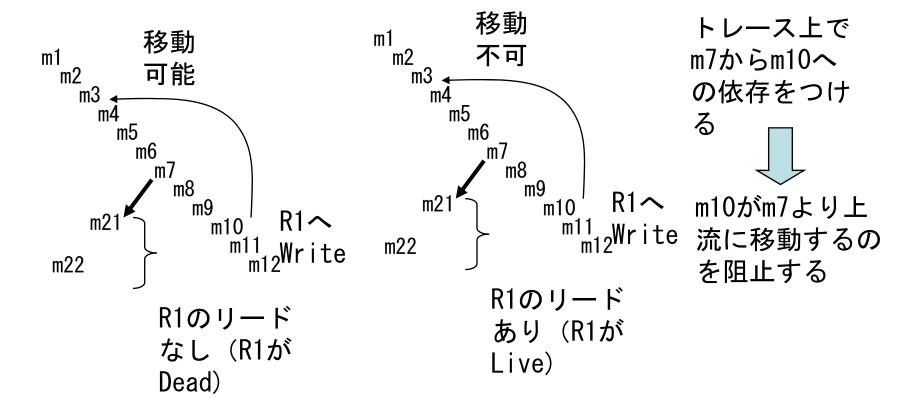

(1) トレーススケジューリング

1981年: J, Fisher

分岐に偏りのあるプログラムに適用

- 1)トレースの選択

- ②リストスケジューリングでコード移動

- ③命令挿入

- ④次のトレース処理

(a) フローグラフ (b) トレースの決定 (c) トレース内最適化 (d) トレース外に (VLIW命令の合成) 対する後処理

-J.Fisher:Trace Scheduling: A Technique for Global Microcode Compaction, IEEE Trans. Computers, C-30,7, pp.478-490(1981)

トレースの上流から分岐点 を越えて移動の場合

-J.Fisher:Trace Scheduling: A Technique for Global Microcode Compaction, IEEE Trans. Computers, C-30,7, pp.478-490(1981)

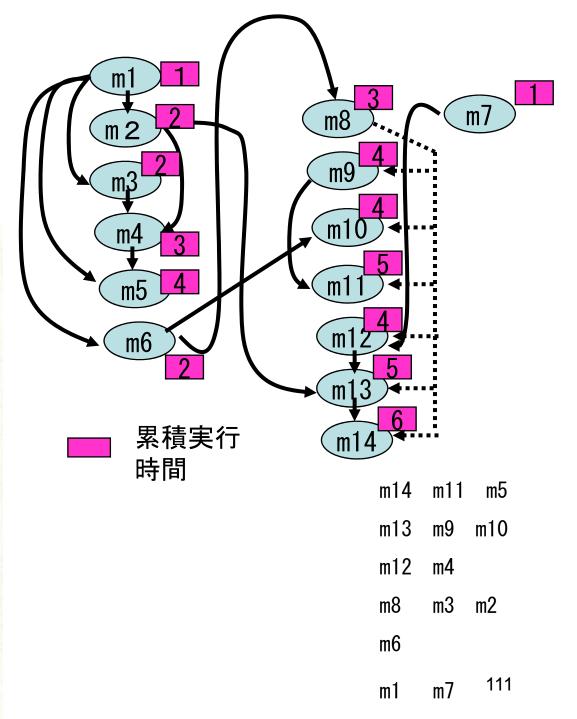

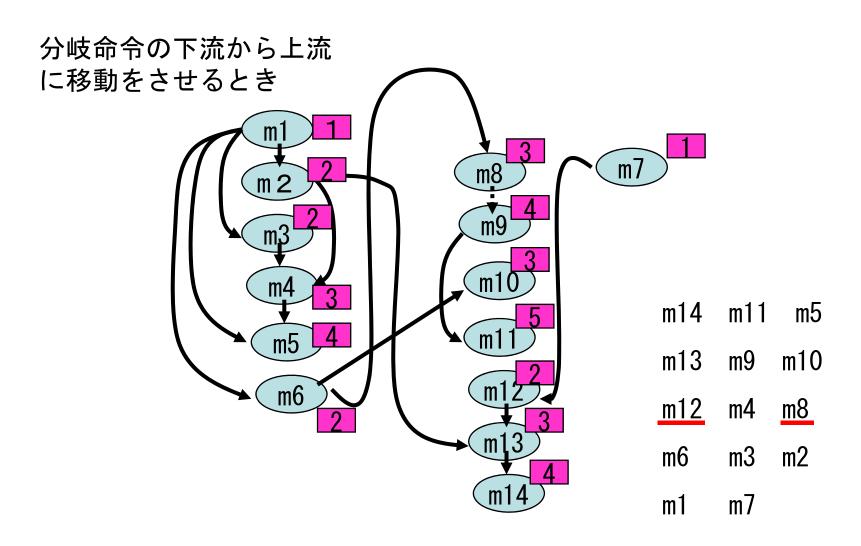

#### 分岐命令の下流から 上流への移動

|        | 基本演算<br>操作番号                                                                                   | ブロック番号                      | デスティ<br>ネーション<br>レジスタ                  | ソースレジスタ                                              | 分岐先           |

|--------|------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------|------------------------------------------------------|---------------|

| エントリ点- | $m_1$ $m_2$ $m_3$ $m_4$ $m_5$                                                                  | B <sub>1</sub> :            | R3<br>R5<br>R6<br>R7<br>R8             | R1, R2<br>R3, R4<br>R3<br>R5, R6<br>R7, R3           | $m_6$         |

|        | $m_6$ $m_7$ $m_8$                                                                              | B <sub>2</sub> :            | R10<br>R11                             | R9, R3<br>R9<br>R10                                  | $m_9, m_{17}$ |

|        | m <sub>9</sub> m <sub>10</sub> m <sub>11</sub> m <sub>12</sub> m <sub>13</sub> m <sub>14</sub> | B <sub>3</sub> : R20の<br>誤り | R13<br>R15<br>R16<br>R17<br>R18<br>R19 | R12<br>R10<br>R13, R14<br>R16, R11<br>R17, R5<br>R18 | Exit          |

| エントリ点- | $m_{15}$ $m_{16}$                                                                              | B <sub>4</sub> :            | R5<br>R8                               | R3, R4<br>R7, R3                                     | $m_6$         |

|        | m <sub>17</sub>                                                                                | B <sub>5</sub> :            | R12                                    | R13                                                  |               |

図 6.19 トレーススケジューリングの適用例30)

#### 分岐命令の下流から上流 に移動をさせないとき

| 基本演算<br>操作番号                                                    | ブロック<br>番号       | デスティ<br>ネーション<br>レジスタ      | ソース<br>レジスタ                                |

|-----------------------------------------------------------------|------------------|----------------------------|--------------------------------------------|

| $m_1$ $m_2$ $m_3$ $m_4$ $m_5$                                   | B <sub>1</sub> : | R3<br>R5<br>R6<br>R7<br>R8 | R1, R2<br>R3, R4<br>R3<br>R5, R6<br>R7, R3 |

| $m_6$ $m_7$ $m_8$                                               | B <sub>2</sub> : | R10<br>R11                 | R9, R3<br>R9<br>R10                        |

| $m_9$ $m_{10}$                                                  | B <sub>3</sub> : | R13<br>R15                 | R12<br>R10                                 |

| m <sub>11</sub> m <sub>12</sub> m <sub>13</sub> m <sub>14</sub> | R20 -            | R16<br>R17<br>R18<br>R19   | R13, R14<br>R16, R11<br>R17, R5<br>R18     |

| $m_{15}$ $m_{16}$                                               | B <sub>4</sub> : | R5<br>R8                   | R3, R4<br>R7, R3                           |

| m <sub>17</sub>                                                 | $B_5$ :          | R12                        | R13                                        |

m12とm8が同時実行

図 6.19 トレーススケジューリングの適用例30)

|        | 基本演算<br>操作番号                                                                                    | ブロック<br>番号                  | デスティ<br>ネーション<br>レジスタ                  | ソース<br>レジスタ                                          | 分岐先           |

|--------|-------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------|------------------------------------------------------|---------------|

| エントリ点- |                                                                                                 | B <sub>1</sub> :            | R3<br>R5<br>R6<br>R7<br>R8             | R1, R2<br>R3, R4<br>R3<br>R5, R6<br>R7, R3           | $m_6$         |

|        | $m_6$ $m_7$ $m_8$                                                                               | B <sub>2</sub> :            | R10<br>R11                             | R9, R3<br>R9<br>R10                                  | $m_9, m_{17}$ |

|        | m <sub>10</sub> m <sub>10</sub> m <sub>11</sub> m <sub>12</sub> m <sub>13</sub> m <sub>14</sub> | B <sub>3</sub> : R20の<br>誤り | R13<br>R15<br>R16<br>R17<br>R18<br>R19 | R12<br>R10<br>R13, R14<br>R16, R11<br>R17, R5<br>R18 | Exit          |

| エントリ点- |                                                                                                 | B <sub>4</sub> :            | R5<br>R8                               | R3, R4<br>R7, R3                                     | $m_6$         |

|        | m <sub>17</sub>                                                                                 | B <sub>5</sub> :            | R12                                    | R13                                                  |               |

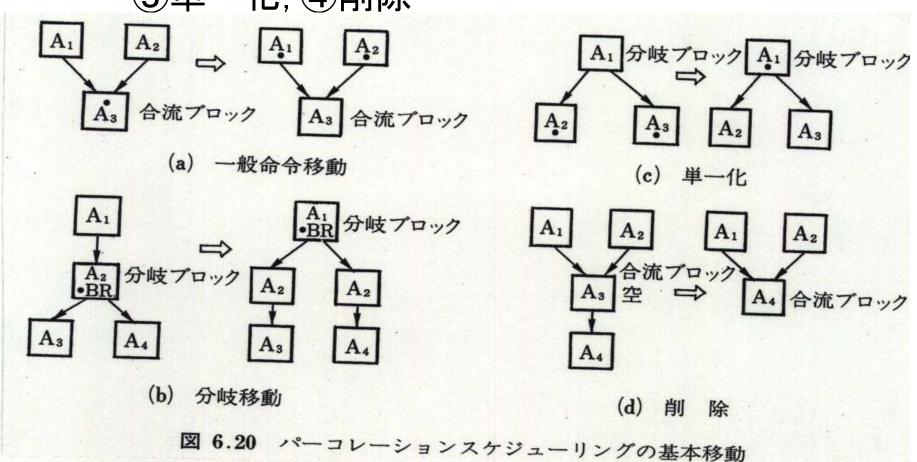

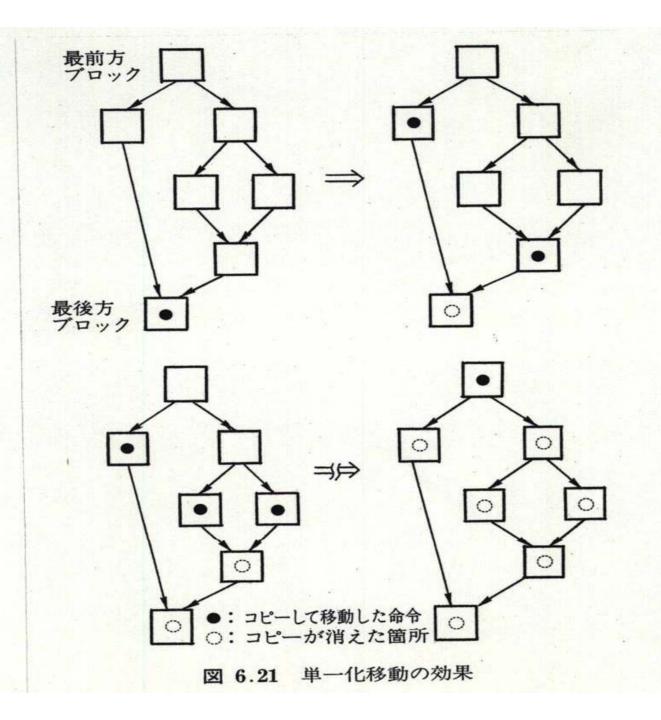

# (2) パーコレーションスケジューリング 命令をどんどん前方のブロックへ:漏斗

- ①一般命令移動, ②分岐命令移動

- ③单一化, ④削除

## (3) ループアンローリング

### ソースプログラム

D0 10 I=1, N Z(I)=X(I)+Y(I) (19) W(I)=X(I)\*Y(I)

10 CONTINUE

```

目的コード

LOAD R1 M(R10+D1)

LOAD R2 M(R10+D2)

ADDF R3 R1 R2

MULF R4 R1 R2

ADDI R10 #11

(20)

ADDI R11 #11

STORE M(R10+D3) R3

STORE M(R10+D4) R4

BRCN M(PC-18) Lに分岐

```

## VLIW命令での単純実行:NOP多し

```

LOAD IF D EX EX S

(1)

LOAD IF D

EX EX S

すべてNOP

3

ADDF

IF D

EX EX EX S

MULF

IF D EX EX EX S

ADD I

IF D/

EX S

(21)

ADD I

EX S

すべてNOP、

4

(5)

すべてNOP

6

STORE

EX EX S

IF D

STORE

IF D

EX EX S

IF D EX S

BRCN

LOAD

IF D

EX EX S 遅延スロットの実行

(7)

LOAD

EX EX S (2回目の反復)

IF D

8

すべてNOP

遅延スロットの実行

```

## ループアンローリング:1つの反復内に旧反復 を2つ入れ、反復回数を半分にする

```

LOAD IF D EX EX S

LOAD IF D EX EX S

2

EX EX S

LOAD

IF D

IF D EX EX S

LOAD

3

ADDF

IF D

EX EX EX S

MULF

IF D

EX EX EX S

ADDF

IF D

EX EX EX S

(4)

MULF

EX EX EX S (26)

IF D

ADD I

IF D

EX S

ADD I

IF D

EX S

すべてNOP

(5)

STORE

EX EX S

IF D

STORE

122

```

EX EX S

IF D

7 STORE STORE BRCN IF D EX EX S

IF D EX EX S

IF D EX S

遅延スロットの実行

(2回目の反復)

8 LOAD LOAD

IF D EX EX S

IF D EX EX S

LOAD IF D EX EX S LOAD IF D EX EX S **2** EX EX S LOAD IF D IF D EX EX S LOAD 3 LOAD IF D EX EX S LOAD IF D EX EX S **(4**) **ADDF** IF D EX EX EX S MULF IF D EX EX EX S **(5) ADDF** IF D EX EX EX S MULF IF D EX EX EX S **6**) **ADDF** EX EX EX S IF D MULF EX EX EX S IF D

**ADD I**

EX S

IF D

- **ADD I STORE STORE STORE** 8 **STORE STORE** 9

- 9 STORE STORE BRCN

- 10 LOAD LOAD

IF D EX S (28)

IF D EX EX S

IF D EX S

遅延スロットの実行

(2回目の反復)

IF D EX EX S

IF D EX EX S

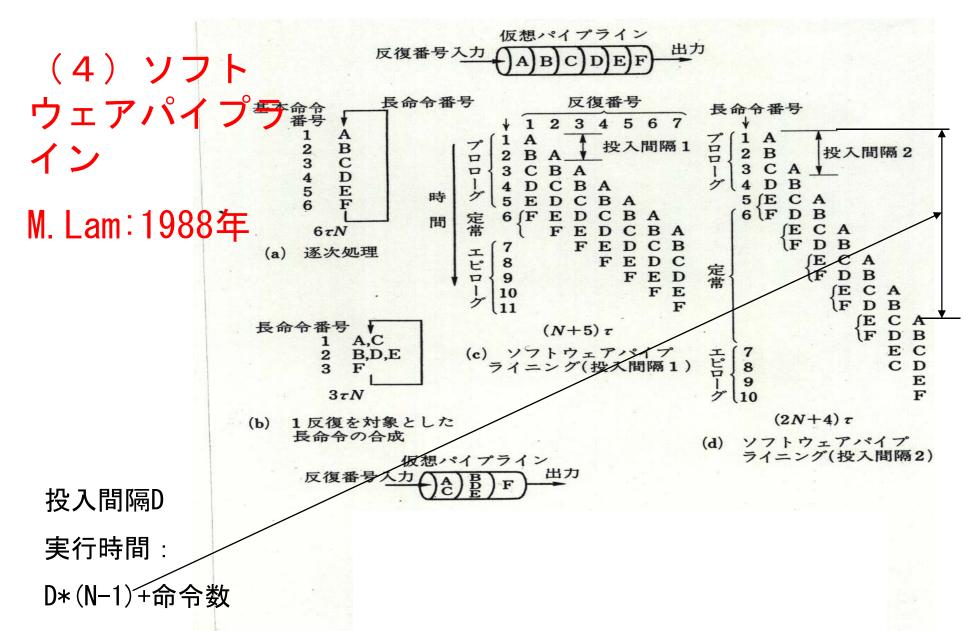

•M.Lam:Software Pipelining: An Effective Scheduling Technique for VLIW Machines, Proc of Conf on Programming Language Design and Implementation, pp.318-328(1988)

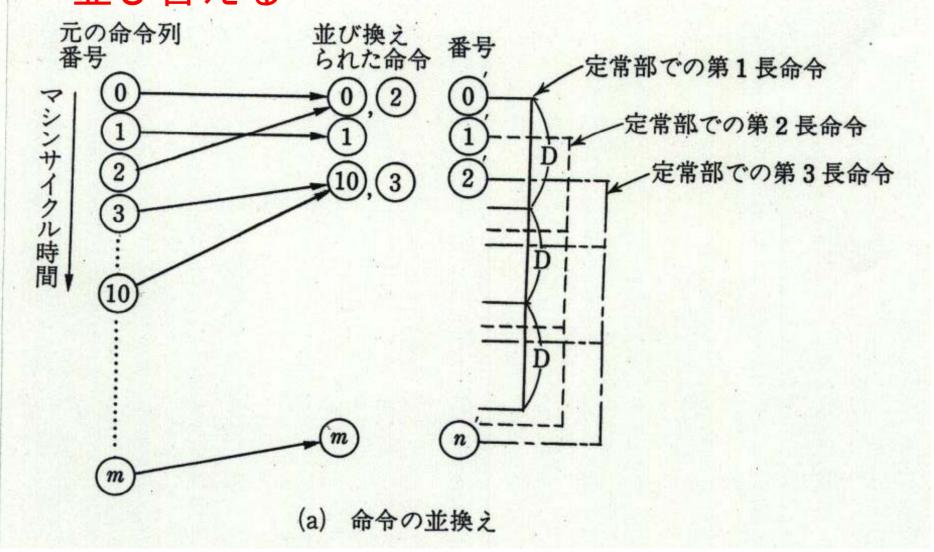

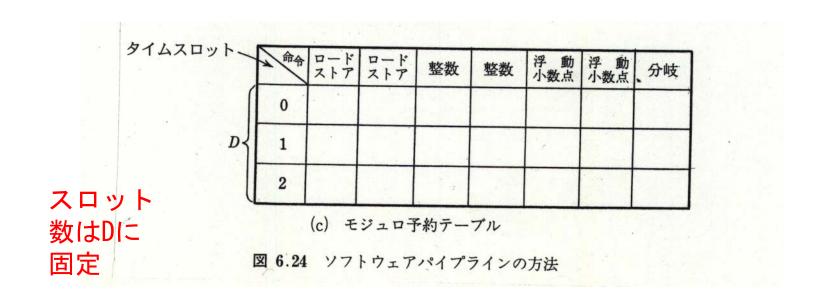

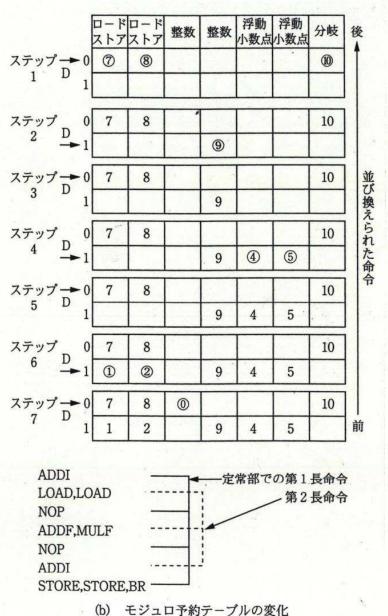

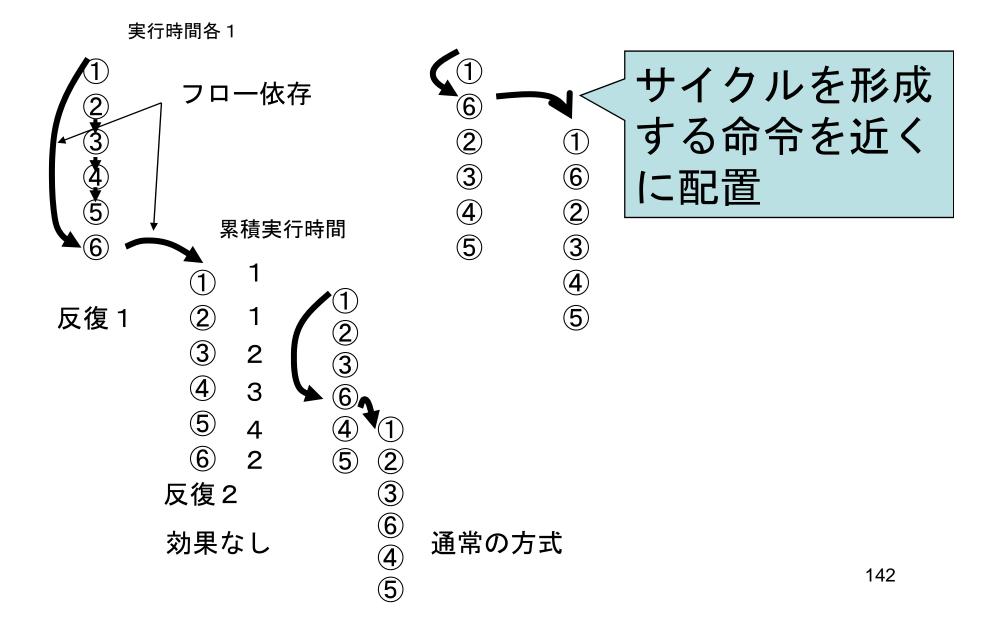

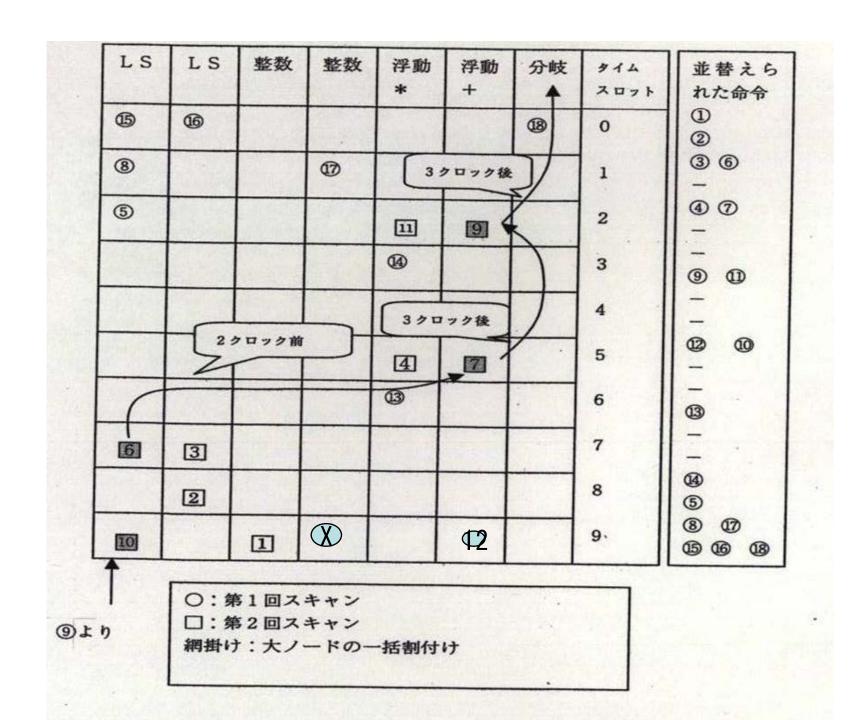

## 基本:Dが最小となるように命令を 並び替える

リストスケージューリングを適用 投入間隔をDに設定 モジュロ予約テーブル Dごとに循環 資源の競合発生: D+1

Dの最小値は?

リストスケジューリングでD ごとに折り畳む

### Dの最小値の決定法

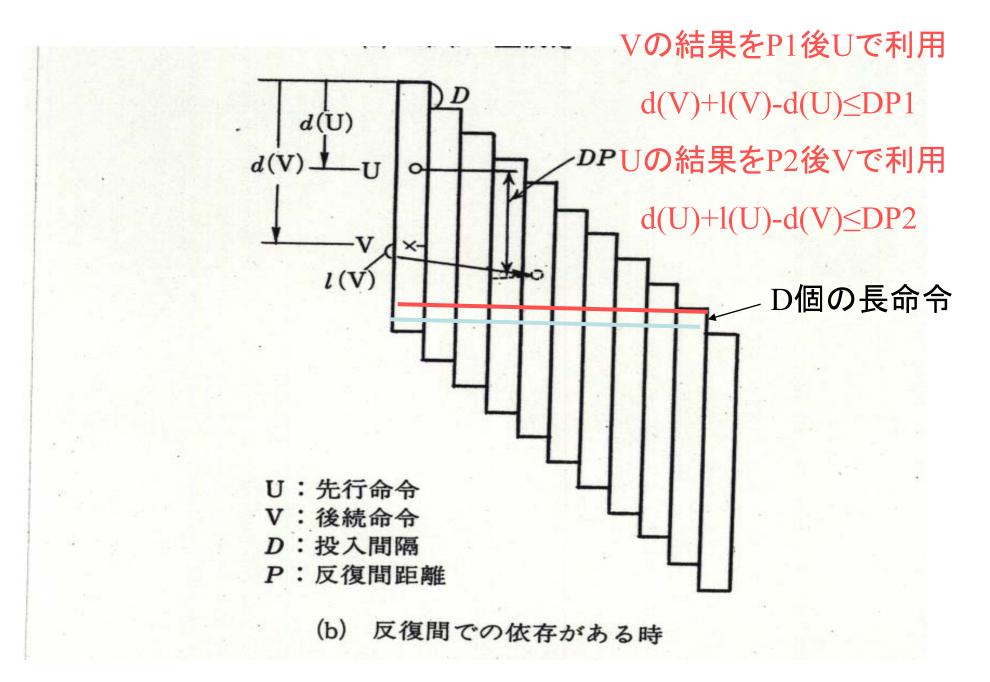

#### ① 反復間の依存性

$$D \ge (d(V) - d(U) + I(V)) / P1$$

(29)

$$D \ge (d(U) - d(V) + I(U)) / P2$$

(30)

$$D \ge (I(V) + I(U)) / (P1 + P2) \tag{31}$$

反復内での依存性

$$d(V) - d(U) \ge I(U) \tag{32}$$

#### ②資源競合

反復内で同一の演算装置を使用する命令数NI、 長命令で指定できる同一の演算器の数をNVとすると、 D≥NI/NV (33)

D個の長命令

演算指定個数:D\*W≥命令数NI

- ソフトウェアパイプラインの手順

- ①投入間隔Dの最小値、最大値の決定

- ②投入間隔Dを最小値に設定, だめならD+1

### 命令の並び換えの手順

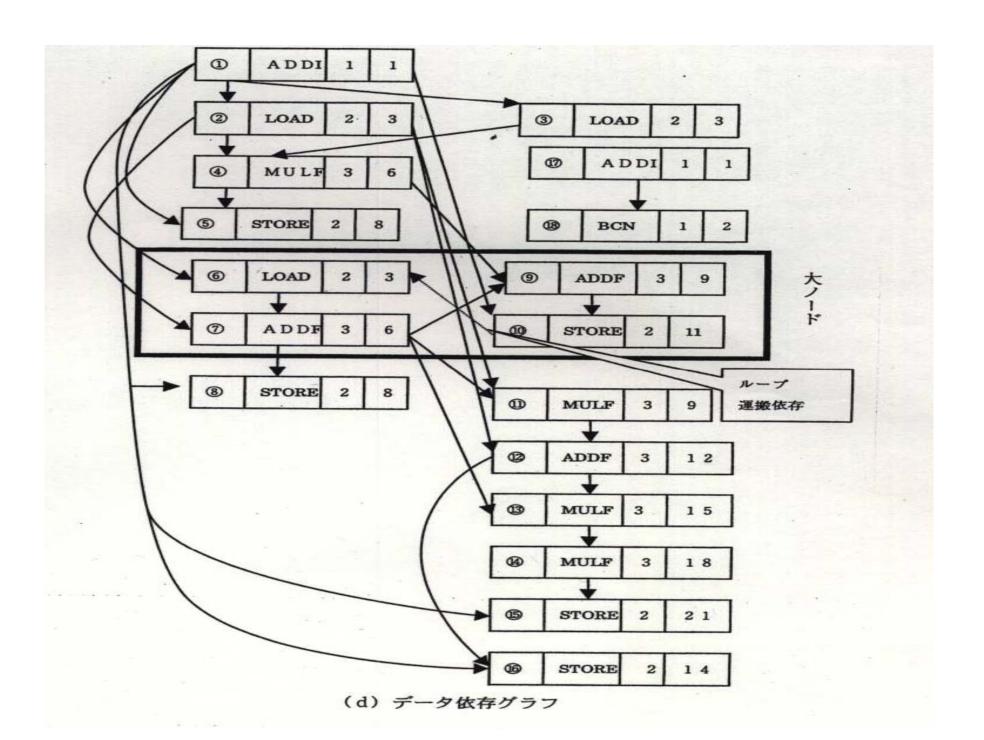

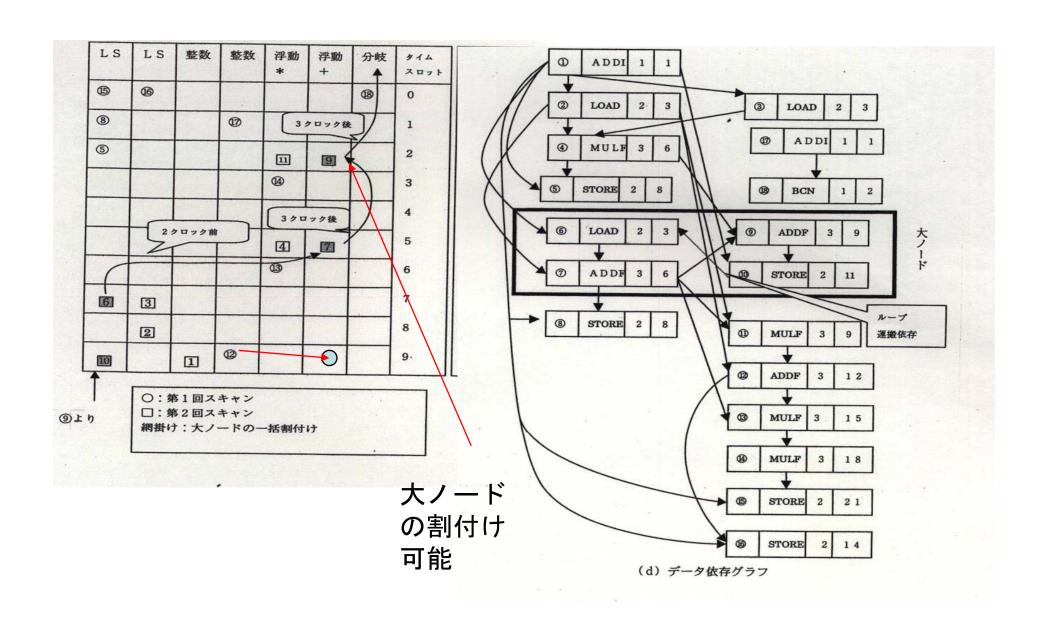

- ①データ依存グラフの作成

- ②ループ運搬依存(サイクル)のないとき 資源競合チェック:モジュロ予約テーブル

- ③ループ運搬依存(サイクル)のあるとき ループ運搬依存にある2つの命令の優先的並換え 大ノードからなるデータ依存グラフに対して、② を実行する。

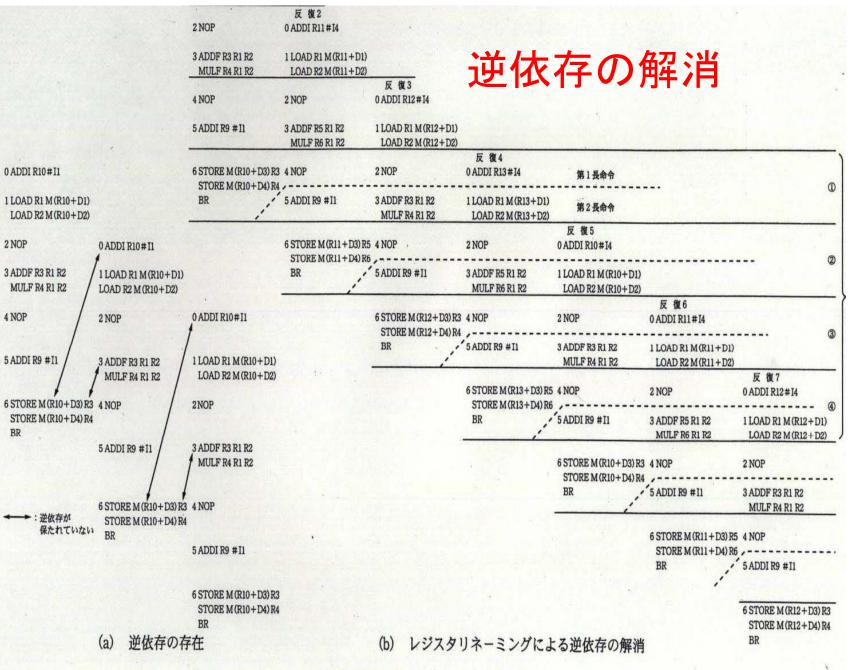

- 42、③で得られた結果に対して、逆依存、出力依存 を解消するレジスタリネーミングを施す。

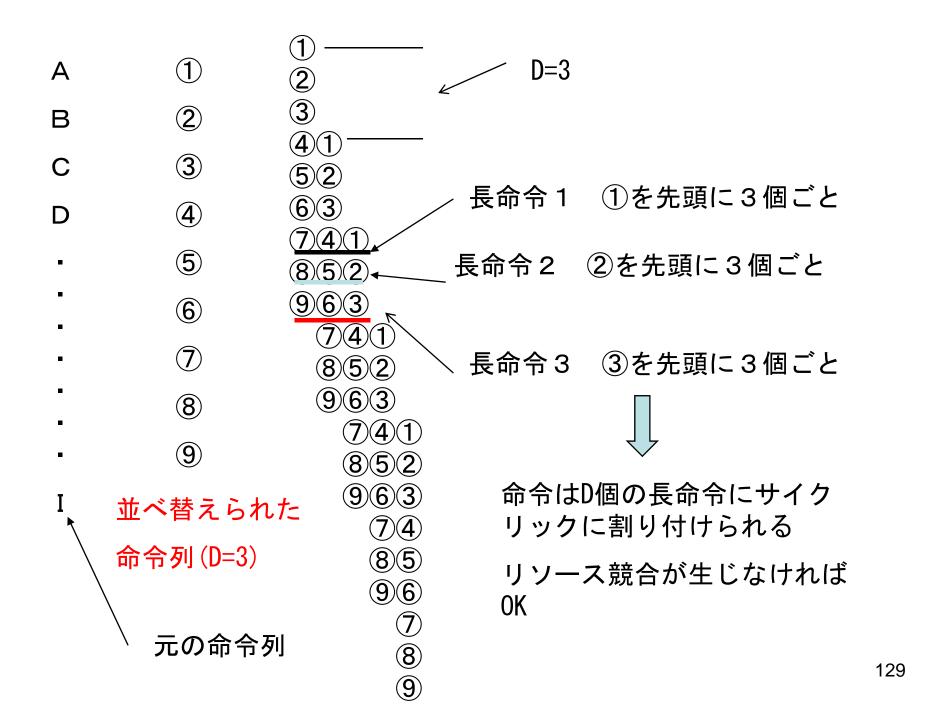

## サイクルのない場合の例 ソースプログラム

### ソフトウェアパイプラインの例:

### 反復間にサイクルなしの例

- O ADDI R10 #11

- 1 LOAD R1 M(R10+D1) <sub>資源の制約から</sub>

- 2 LOAD R2 M(R10+D2) Dの最小値: 2

- 3 NOP

- 4 ADDF R3 R1 R2

- 5 MULF R4 R1 R2

- $6 NOP \qquad (34)$

- 7 STORE M(R10+D3) R3

- 8 STORE M(R10+D4) R4

- 9 ADDI R9 #11

- 10 BRCN M (PC-18)

図 6.25 ソフトウェアパイプラインの一例 (データ依存グラフにサイクルのない場合)

### 並び換えられた命令列

- O ADDI R10 #11

- 1 LOAD R1 M(R10+D1), LOAD R2 M(R10+D2)

- 2 NOP

- 3 ADDF R3 R1 R2 , MULF R4 R1 R2

- 4 NOP

- 5 ADDI R9 #I1 (35)

- 6 STORE M(R10+D3) R3, STORE M(R10+D4), BR

図 6.26 レジスタリネーミングの適用

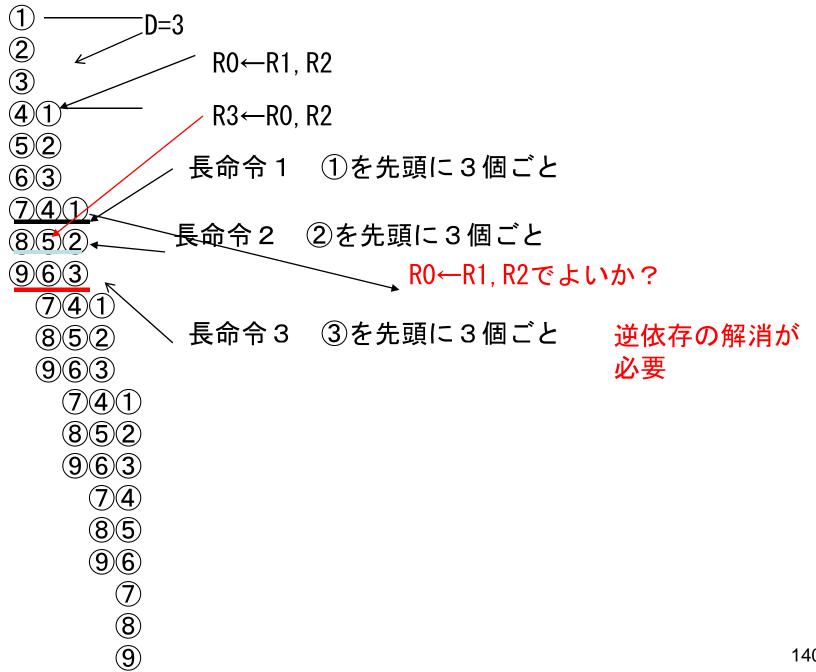

## 反復間にサイクルがある場合

サイクルがある場合 DO 10 I=1, N ① ADDI R10 R10 #I1 A(I) = B(I-1) + C(I)② LOAD \_R3 M(R10+D3) D(I) = A(I) \*C(I)R2 M (R10+D2)  $\rightarrow$  (B) 3 LOAD E(I) = C(I) \* B(I)(B) R5 R2 R3 4 MULF D(I) = D(I) + C(I)(5) STORE M(R10+D5) R5 C(I) = A(I) \* D(I)R6 M(R10+D2-1) 6 LOAD C(I) = C(I) \* 10.0(A)R1 R6 R3 7 ADDF B(I) = A(I) + E(I)® STORE M(R10+D1) R1 1 0 CONTINUE R2 R1 R5 ADDF (a) 元プログラム OF STORE M(R10+D2) R2 1 MULF R4 R1 R3 DO 10 I=1, N 12 ADDF R4 R4 R3 E(I) = C(I) \* B(B) (13) MULF R3 R4 R1 (A) A(I) = B(I - 1)(D) (4) MULF R3 R3 #F10.0 B(I) = A(I) + E(I)(C) (5) STORE M(R10+D3) R3 D(I) = A(I) \*C(I)(6) STORE M(R10+D4) R4 D(I) = D(I) + C(I)(D)77 ADDI R9 #I1 C(I) = A(I) \* D(I)(8) BRCN M(L) C(I) = C(I) \* 10.01 0 CONTINUE (c)(b)に対応する機械命令列 (b) 投入間隔最小化のための移動

図 6.27 ソフトウェアバイプランニングの例(デー

### コンパイラ最適化の効果

### ソースプログラム

D0 10 I=1, N

Z(I)=X(I)+Y(I) (19)

W(I)=X(I)\*Y(I)

10 CONTINUE

|            | 方式           | 例番号  | サイクル数 |

|------------|--------------|------|-------|

| 1          | 乱発行乱終了スカラ    | (22) | 1 0   |

| 2          | 乱発行乱終了スーパスカラ | (23) | 6     |

| 3          | 単純VLIW       | (22) | 6     |

| 4          | マルチスレッドVLIW  | (24) | 3. 5  |

| <b>(5)</b> | アンローリング2回    | (26) | 3. 5  |

| <b>6</b>   | アンローリング3回    | (28) | 3     |

| 7          | ソフトウェアパイプライン | (35) | 2     |

### Intel@Itanium

発表: 2000年

EPIC

(ExplicitlyParallel

InstructionComputing)

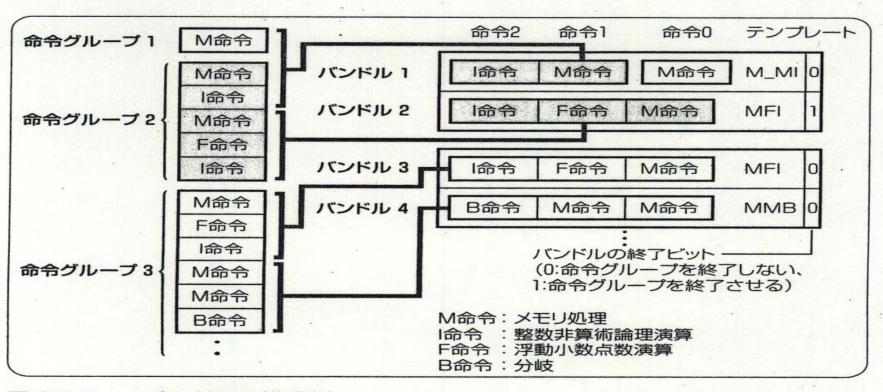

# バンドルの導入

### 純粋VLIWの欠点を解消

コンパイラ支援を得つつ,

命令長の圧縮、NOP削除

互換性の確保. 拡張性の確保

128ビット命令: バンドル

4 1ビットx3操作+5ビットテンプレート

# バンドル

|     | 作 1<br>ビット |       | :作2<br>Lt゙ット | 操作3<br>41ビット | テンフ°レート<br><b>5</b> ビット |

|-----|------------|-------|--------------|--------------|-------------------------|

|     |            |       |              |              |                         |

| P 6 | OP<br>14   | R d 7 | Rs1 7        | Rs2<br>7     |                         |

### テンプレート:5ビット

ストップビット(1ビット)

0:前バンドルと並列化可

互換性、拡張性の確保

1:前バンドルと並列化不可

長命令NOPなし

操作パターンの指定(4ビット)

3つの操作の組み合わせに制約

第2,3操作と並列化不可パターン 長命令内NOP削減

表 2.2 バンドルの種類

| テンプレート | 00  | 01   | 02  | 03    | 04  | 05   | 06  | 07  |

|--------|-----|------|-----|-------|-----|------|-----|-----|

| 命令スロット | MII | MI_I | MLX | (未定義) | MMI | M_MI | MFI | MMF |

| テンプレート | 08  | 09  | OA    | 0B  | OC  | OD    | 0E  | OF    |

|--------|-----|-----|-------|-----|-----|-------|-----|-------|

| 命令スロット | MIB | MBB | (未定義) | BBB | MMB | (未定義) | MFB | (未定義) |

図 2.15 バンドルの構成例

### プレディケート:6ビット

プレディケートレジスタを指示 その内容が 1 であれば操作実行完了 True, False側同時実行と選択 レジスタ 6 4 個、 6 ビットで指定

投機ロードと遅延例外

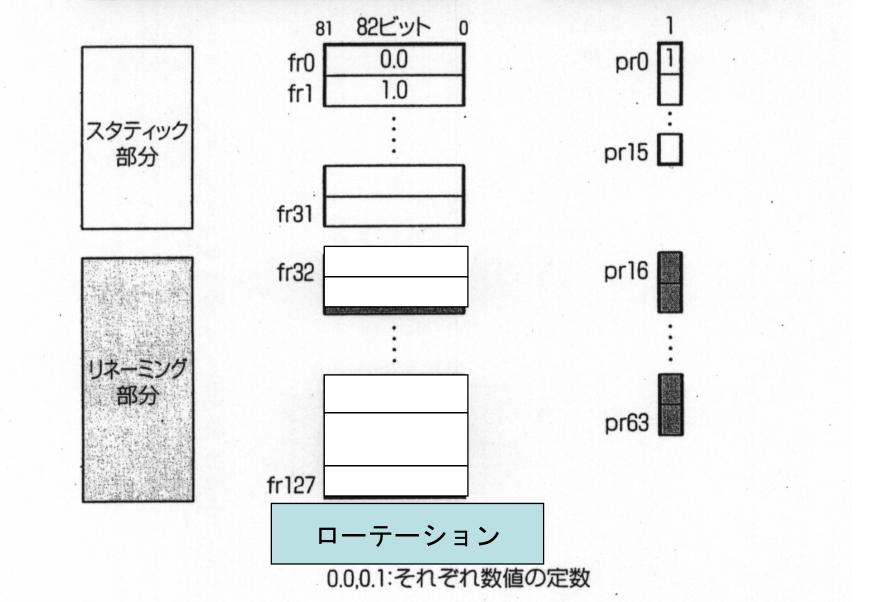

## NaT 汎用レジスタ 63 64ビット gr0 gp grl スタティック sp gr12 部分 gr31 gr32 リネーミング 部分 gr127 レジスタ・スタック gp:グローバル・ポインタ NaT:Not a Thing sp:スタック・ポインタ

# 浮動小数点、プレディケートレジスタ

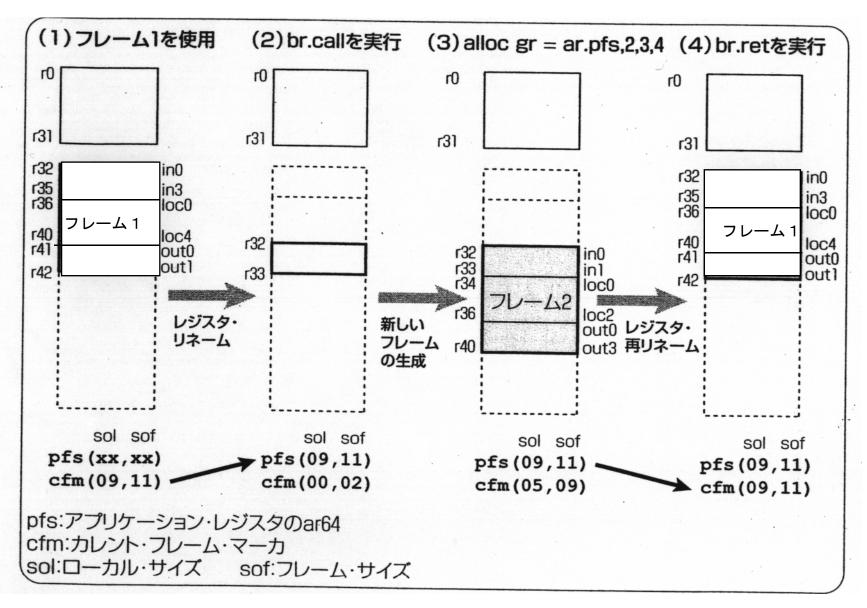

## レジスタスタック

### レジスタローテーション

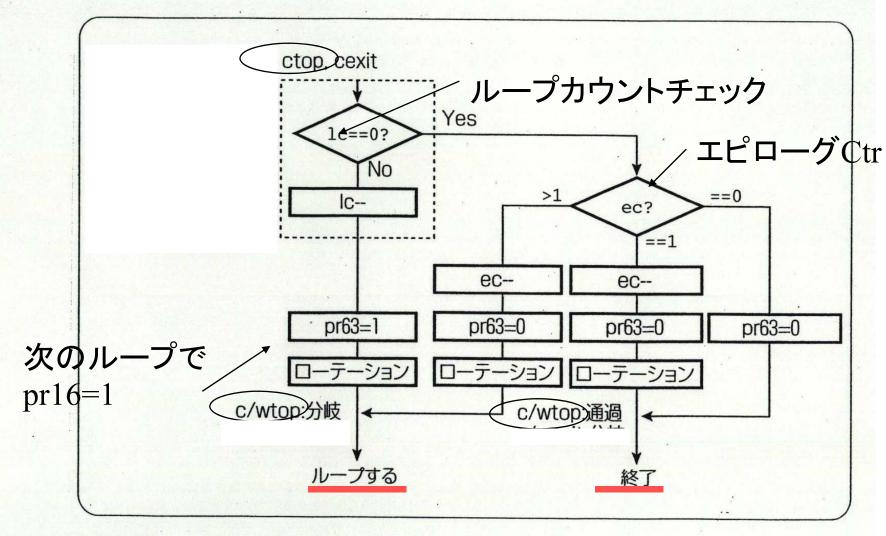

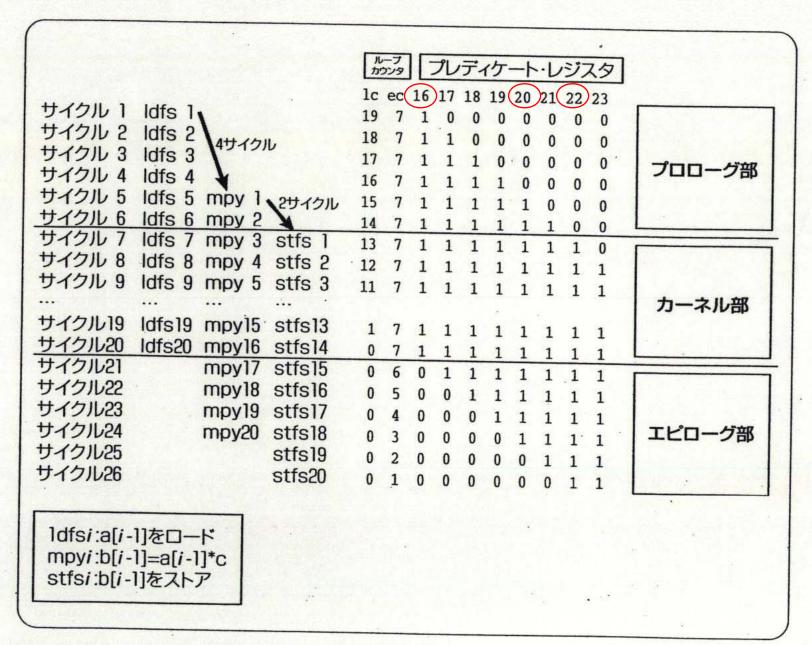

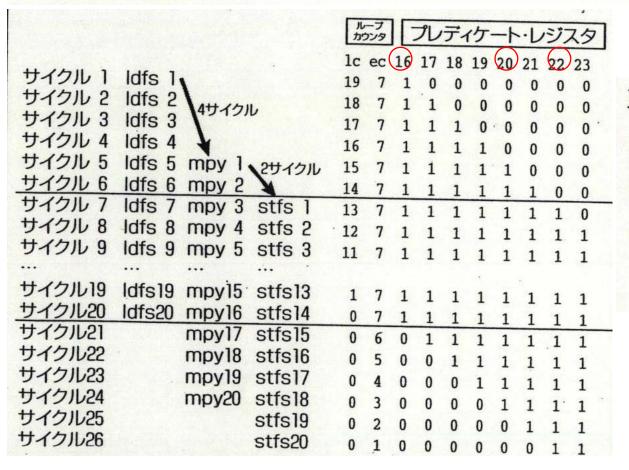

$Fr32 \rightarrow Fr33 \rightarrow \cdot \cdot \cdot Fr127$   $Pr16 \rightarrow Pr17 \rightarrow \cdot \cdot \cdot Pr63$

モジュロスケジュール命令を実行時 レジスタ内容が回転する

図 4.30 モジュロ・スケジュール・ループ命令

池井 満 IA-64プロセッサ、オーム社

### (1)配列を定数倍する C 言語プログラム

```

float a[20],b[20],c;

for(i=0;i<20;i++){

b[i]=a[i]*c

通常の目的プログラム

}

```

### (2)IA-64アセンブラプログラム

```

mov ar.lc=19;; //ループカウンタに回数 - 1をセット loop:ldfs f32=[r15],4;; //命令グループ 0 (4 サイクル) fmpy.s f33=f32,f17;; //命令グループ 1 (2 サイクル) stfs [r16]=f33,4 //命令グループ 2 (1 サイクル) br.cloop.sptk loop //命令グループ 2 (1 サイクル)

```

```

//プレディケート・レジスタをクリア

mov pr.rot=0

cmp.eq p16=r0,r0 //pr16に1をセット

//ループ・カウンタに回数-1をセット

mov ar.lc=19

//エピローグ・カウンタにステージ数

mov ar.ec=7

loop:

ロード: 4サイクル

(p16) ldfs f32=[r15],4

(p20) fmpy.s f37=f36, f17

MUL: 2サイクル

(p22) stfs [r16] = f39,4

br.ctop.sptk loop

br,ctop

ソフトウェア・パイプライニング

図4.31

```

プレディケート

モジュロスケジュール命令

図 4.32 プレディケート・レジスタと実行サイクル

```

mov pr.rot=0 //プレディケート・レジスタをクリア cmp.eq p16=r0,r0 //pr16に1をセット mov ar.lc=19 //ループ・カウンタに回数 - 1をセット mov ar.ec=7 //エピローグ・カウンタにステージ数

```

loop:

(p16) ldfs f32=[r15],4

(p20) fmpy.s f37=f36,f17

(p22) stfs [r16]=f39,4

br.ctop.sptk loop

### 投機ロード

| STORE   | M (R4)   | R12    |    |                                           |

|---------|----------|--------|----|-------------------------------------------|

| LOAD    | R6       | M(R8)  |    |                                           |

| ADD     | R5       | R6     | R7 |                                           |

| STORE   | M(R18)   | R5     |    | R8=R4の時、投機失敗                              |

|         | <b>\</b> | 4      |    | 「ALAT (Advanced Load<br>Address Table)で管理 |

| LOADAdv | R6       | M (R8) |    | ALATのR6のエントリを                             |

|         | 他の命令     | を埋め    | 込み | LOADAdvでセット                               |

| STORE   | M (R4)   | R12    |    | R8=R4ならSTOREでエント                          |

| LOADChk | R6       | M(R8)  |    | リ無効化                                      |

| ADD     | R5       | R6     | R7 | LOADChkでチェックOKな                           |

| STORE   | M(R18)   | R5     |    | ら投機成功、XならLOAD<br>の再実行                     |

|         |          |        |    |                                           |

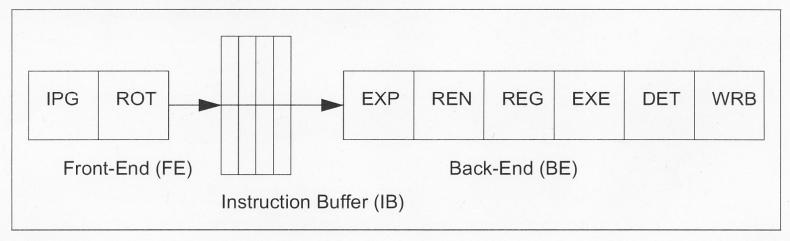

# Itanium2の命令パイプライン

2002年7月発表 8ステージ 2バンドル発行 順発行順終了 分岐予測ミス:6サイクル

### A.1 Core Pipeline

The core pipeline is separated into a front end (FE) and a back end (BE). The FE and BE are separated by an Instruction Buffer (IB).

Figure A-1. Core Pipeline of the Itanium® 2 Processor

The core pipeline consists of 8 stages:

*IPG*: Instruction pointer generation

*ROT*: instruction rotation

EXP: Instruction template decode, expand, and disperse

REN: Rename (for register stack and rotating registers) and decode

REG: Register file read

EXE: ALU execution

DET: Last stage for exception detection

WRB: Write back

#### A.4.1 FPU Micro-Pipeline

The FPU pipeline is four stages deep (FP1 to FP4), with write back performed in the fifth stage (FWB). The FPU is fully pipelined. In the FP1 stage, an early examination of the numeric operands is performed to determine if the instruction can be numeric exception free.

#### Table A-1. FPU Pipeline

| Core Pipeline | REG | EXE | DET | WRB |     |     |

|---------------|-----|-----|-----|-----|-----|-----|

| FPU Pipeline  |     | FP1 | FP2 | FP3 | FP4 | FWB |

#### A.4.2 L1D Micro-Pipeline

In the L1M stage, the L1 data, tag and the L1 DTLB are accessed in parallel and deliver data to the execution units.

#### Table A-2. L1D Micro-Pipeline

| Core Pipeline | REN | REG | EXE | DET | WRB |

|---------------|-----|-----|-----|-----|-----|

| L1D Pipeline  |     | L1I | L1M | L1D | WRB |

### A.4.3 L2 Micro-Pipeline

The first stage is used for L2 TLB accesses. The L2A stage arbitrates for the data array accesses. Demand fetches for instructions have the highest priority, followed by loads and prefetches. Data array access occurs in the L2M stage. The L2D stage is for way selection, and data delivery. The L2C stage is used for correction of ECC errors and for error detection.

#### Table A-3. L2 Micro-Pipeline

| Core Pipeline | REG | EXE | DET | WRB |     |     |     |

|---------------|-----|-----|-----|-----|-----|-----|-----|

| L2 Pipeline   |     | L2L | L2A | L2M | L2D | L2C | L2W |

### キャッシュメモリ: 3階層、すべて実アドレスキャッシュ

Table 6-4. Cache Summary

|                        | L1I                                              | L1D                                              | L2                                                                               | L3                                   |

|------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|

| Size                   | 16 KB                                            | 16 KB                                            | 256 KB                                                                           | 3 MB or 1.5 MB                       |

| Associativity          | 4-way                                            | 4-way                                            | 8-way                                                                            | 12-way                               |

| Line size              | 64 Bytes                                         | 64 Bytes                                         | 128 Bytes                                                                        | 128 Bytes                            |

| Latency                | 1 cycle                                          | 1 cycle                                          | Minimum 5 cycles integer load use                                                | Minimum 12 cycles load use           |

|                        |                                                  |                                                  | Minimum 6 cycles floating-point load use                                         |                                      |

|                        |                                                  |                                                  | 7 cycles with 6 cycle stall penalty in <i>ROT</i> stage for instruction load use |                                      |

| Tag Read<br>bandwidth  | 2 / cycle                                        | 4 / cycle                                        | 4 / cycle                                                                        | 1 / cycle                            |

| Data Read<br>bandwidth | 1 X 32B / cycle                                  | 2 X 8B / cycle                                   | 4 x 8B / cycle                                                                   | 1 x 32B / cycle                      |

| Data banks             | NA                                               | 8 bytes/bank<br>(store only)                     | 16 bytes/bank                                                                    | NA                                   |

| Write bandwidth        | NA                                               | 2 x 8B / cycle                                   | 4 x 16B / cycle                                                                  | 1 x 32B / cycle                      |

| Fill bandwidth         | 64 bytes<br>assembly 2 cycles<br>write - 1 cycle | 64 bytes<br>assembly 2 cycles<br>write - 1 cycle | 128 bytes<br>assembly 4 cycles<br>write - 1 cycle                                | 128 bytes in 4 cycles                |

| Outstanding misses     | 7 prefetches                                     | 8 unique lines                                   | 16 unique lines                                                                  | 22 (16 read shared with L2, 6 write) |

| Line size              | 64 Bytes                                         | 64 Bytes                                         | 128 Bytes                                                                        | 128 Bytes                            |

# 分岐予測

Table 2-8. Branch Prediction Latencies (in cycles)

|                                              | Itanium <sup>®</sup> 2 Processor | Itanium <sup>®</sup> Processor |

|----------------------------------------------|----------------------------------|--------------------------------|

| Correctly predicted taken IP-relative branch | 0                                | 1                              |

| Correctly predicted taken indirect branch    | 2                                | 0                              |

| Correctly predicted taken return branch      | 1                                | 1                              |

| Last branch in perfect loop prediction       | 0                                | 2                              |

| Misprediction latency                        | 6+                               | 9                              |

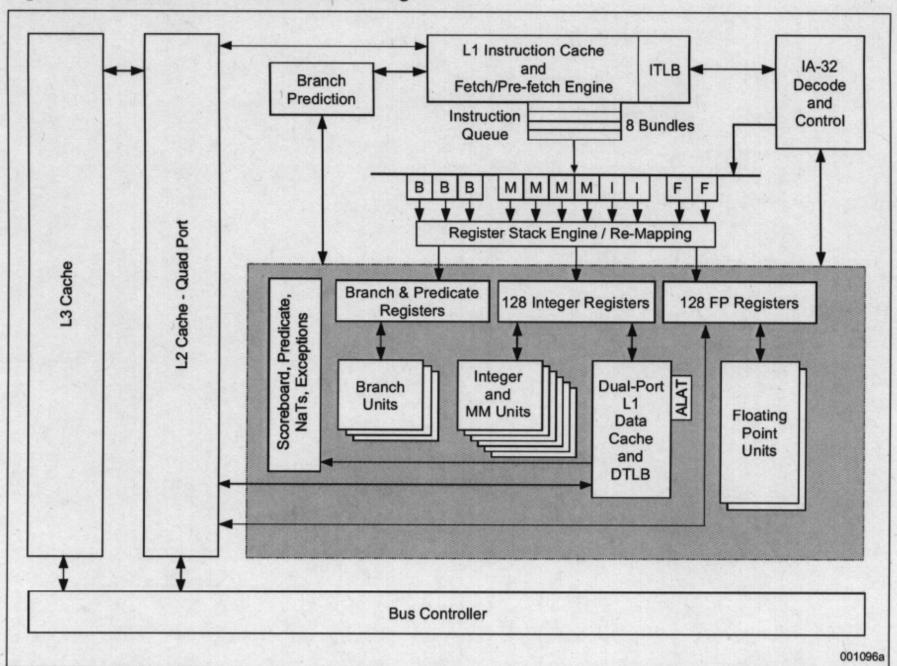

Figure 2-3. Itanium® 2 Processor Block Diagram

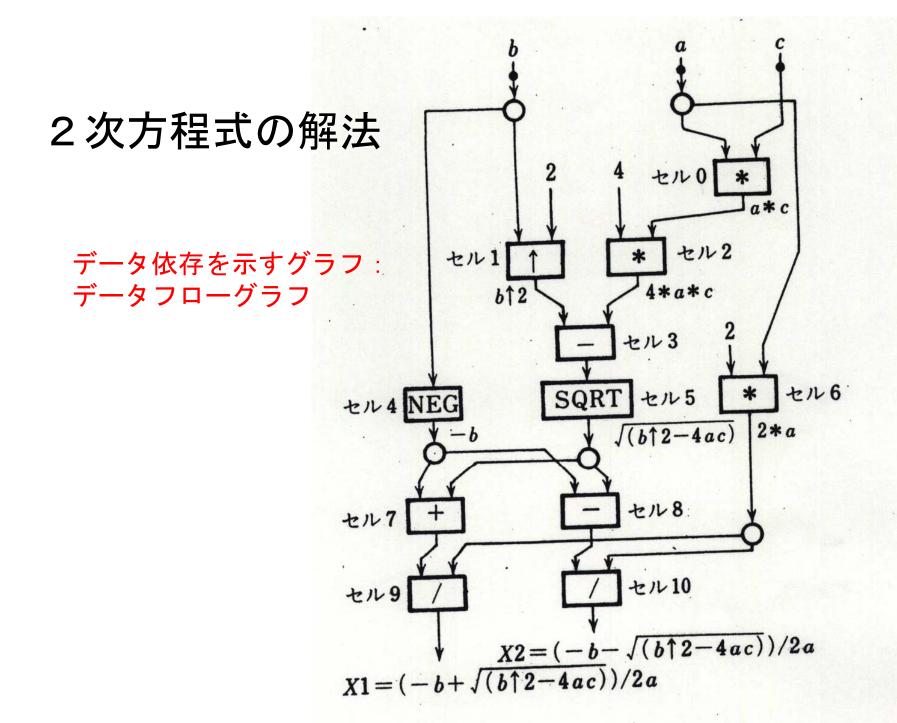

# かってデータフローコンピュータという魅惑的な研究があった

1974年: J. Dennis (MIT)、静的データフロー

1978年: J. Gurd (Manchester大)、動的データフロー

1970年代後半から80年代前半

スーパスカラ方式のルーツ

### 特徴

- プログラムカウンタがない

- プログラムに内在するすべての並列性を実行時に取り 出せる

VLIW方式のルーツ:水平型マイクロプログラム

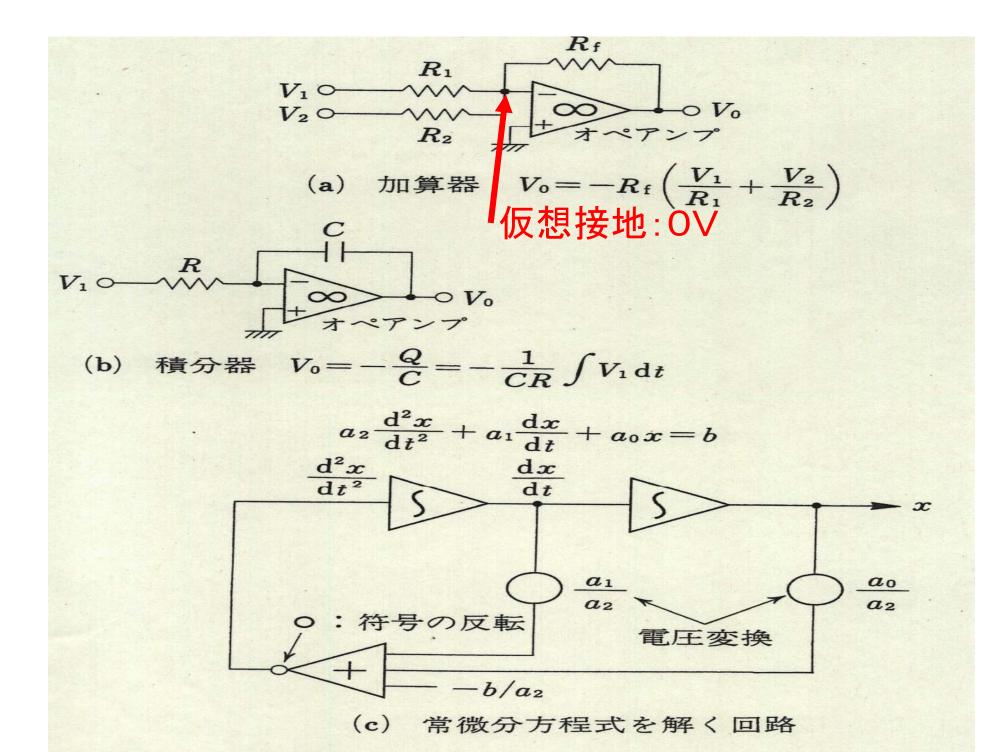

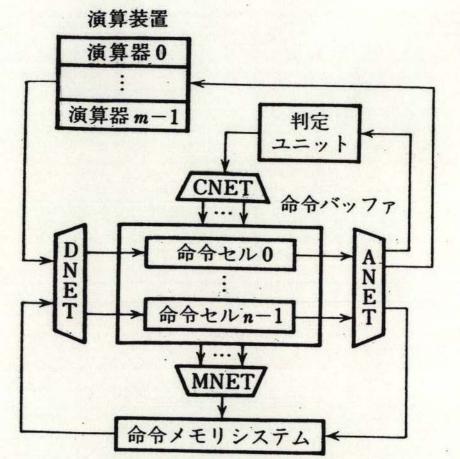

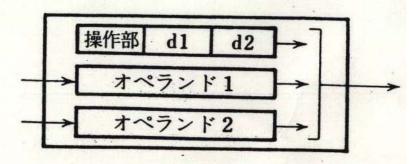

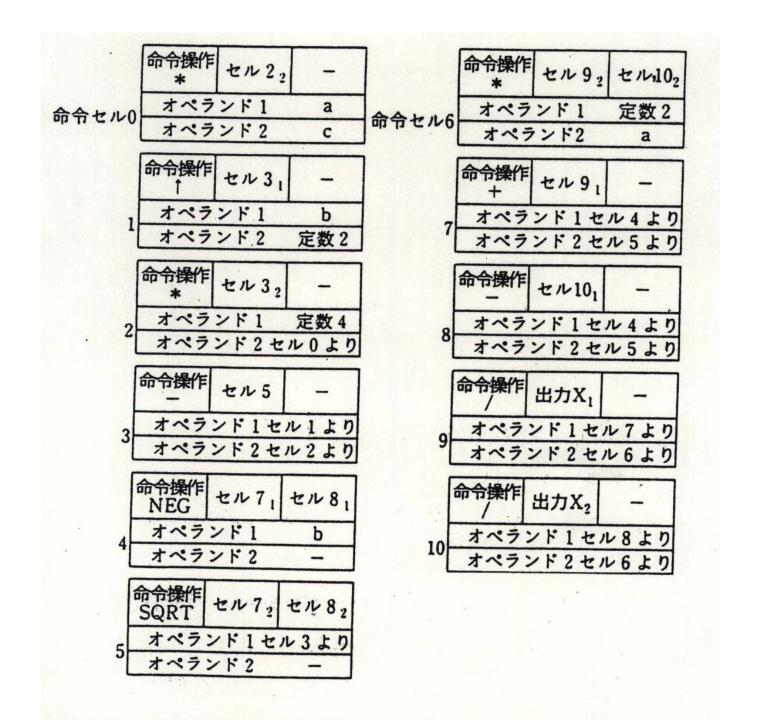

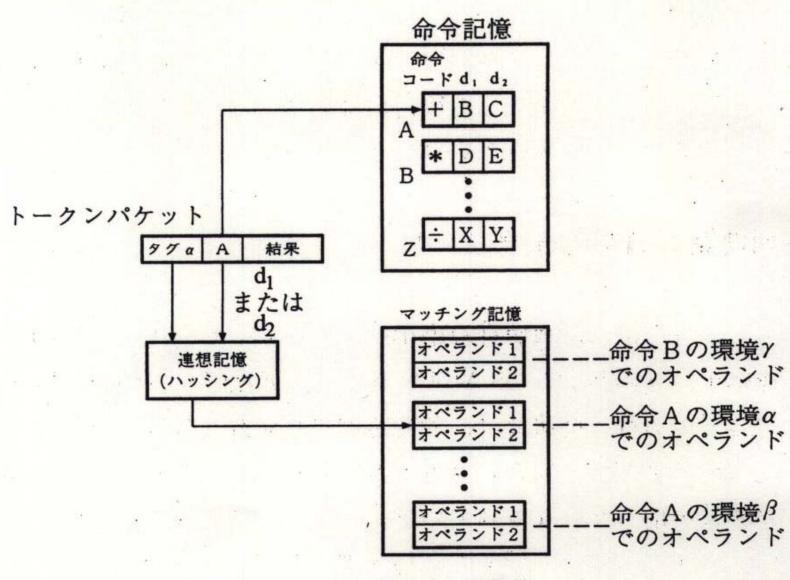

(b) 各命令セルの構造. d1,d2:デス ティネーションセルを指定.

- (a) ハードウェア構造. ANET:アービトレーション ネットワーク, DNET:ディストリビューション ネットワーク, CNET:制御ネットワーク, MNET :メモリコマンドネットワーク

- 図 5. 23 データ駆動型計算機の構成 (J. B. Dennis, et al.: 'A Preliminary Architecture for a Basic Data-Flow Processor', Proc. of 2nd Annual Int. Symp. on Computer Architecture, pp, 126-132 (1975) による)

175

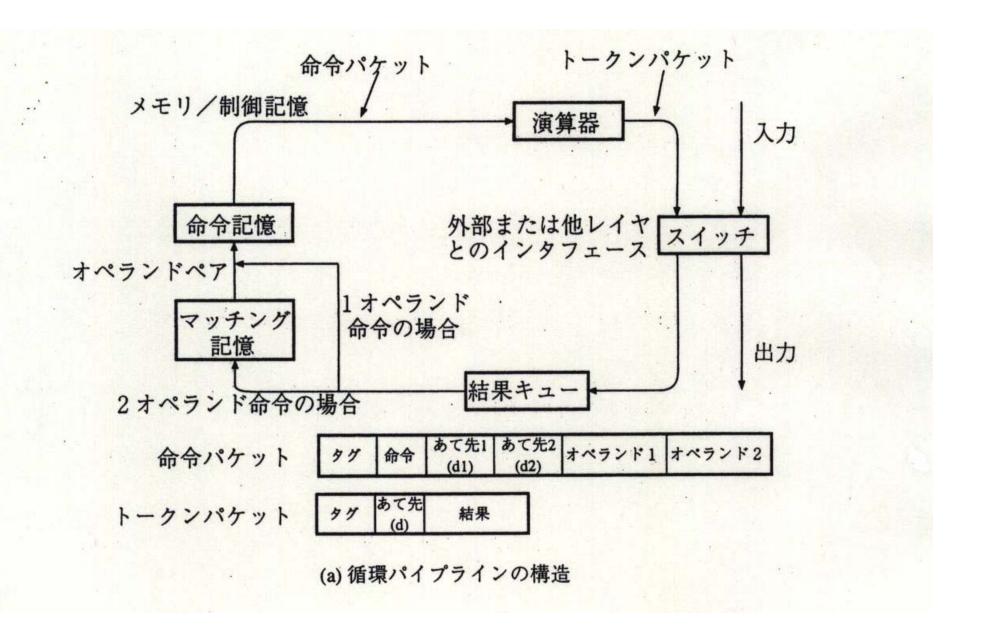

(b) マッチング記憶

図 5.25 循環パイプライン型データ駆動コンピュータ

# 第13章 将来展望

- 13.1 汎用プロセッサの高速化・省電力化

- 13.2 メディアプロセッサ

- 13.3 省電力化への並列処理の利用

- 13.4 超高信頼、セキュアなプロセッサ

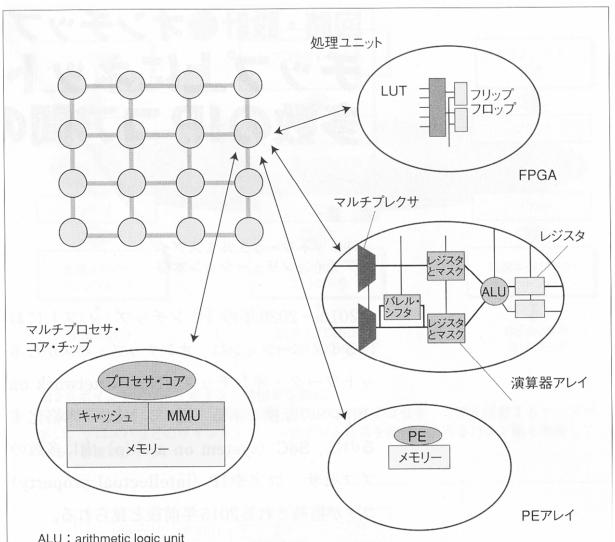

- 13.5 再構成可能素子による 可変構造コンピュータ

### ①大域並列の利用

- パイプライン:時間並列

- ・乱実行、投機実行による時間並列の高速化

- 局所並列:スーパスカラ、VLIW

- 非常に複雑な構造IPCの頭打ち

大域並列:マルチコア型プロセッサ

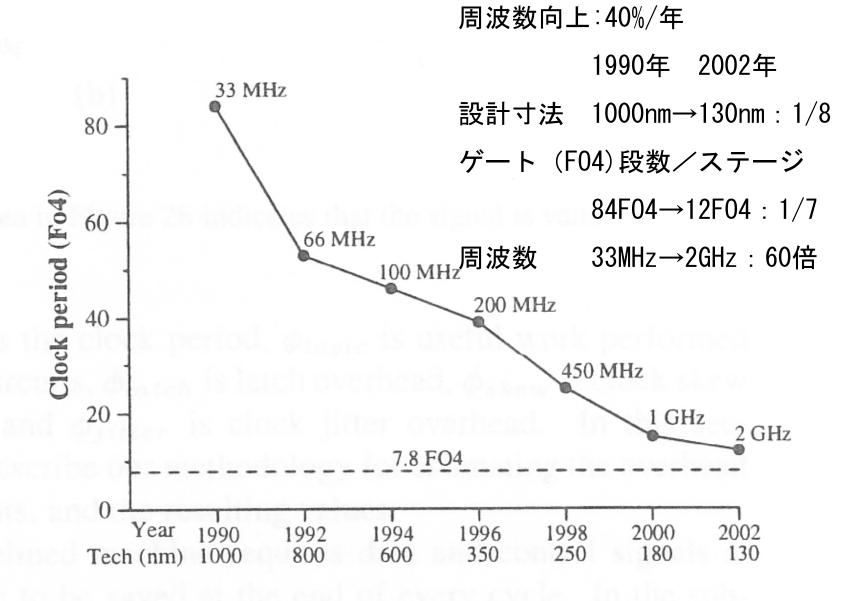

- ・周波数向上が困難 □ 深いパイプラインで性能向上:小さくなった

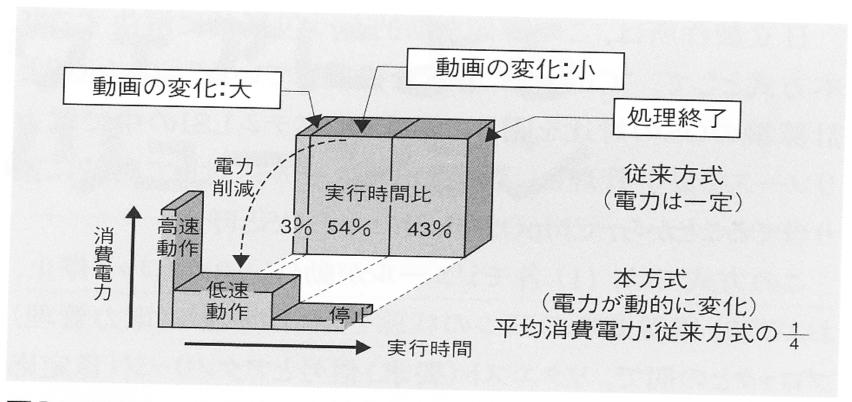

- ②省電力化 動的消費電力∝ f<sup>3</sup> リーク電流の増大

- ③高信頼化・セキュア化

プログラムカウンタの - 近傍にある命令の 並列実行

「キャッシュ、分岐予測ミス ステージ内ゲート段数<sub>179</sub>

# Intelのマイクロプロセッサの 発展過程

| Intel Processor                                | Date<br>Intro-<br>duced | Max. Clock<br>Frequency<br>at Intro-<br>duction | Tran-<br>sistors | Register<br>Sizes <sup>1</sup>       | Ext.<br>Data<br>Bus<br>Size <sup>2</sup> | Max.<br>Extern.<br>Addr.<br>Space | Caches                               |

|------------------------------------------------|-------------------------|-------------------------------------------------|------------------|--------------------------------------|------------------------------------------|-----------------------------------|--------------------------------------|

| 8086                                           | 1978                    | 8 MHz                                           | 29 K             | 16 GP                                | 16                                       | 1 MB                              | None                                 |

| Intel 286                                      | 1982                    | 12.5 MHz                                        | 134 K            | 16 GP                                | 16                                       | 16 MB                             | Note 3                               |

| Intel386 DX Processor                          | 1985                    | 20 MHz                                          | 275 K            | 32 GP                                | 32                                       | 4 GB                              | Note 3                               |

| Intel486 DX Processor                          | 1989                    | 25 MHz                                          | 1.2 M            | 32 GP<br>80 FPU                      | 32                                       | 4 GB                              | L1: 8 KB                             |

| Pentium Processor                              | 1993                    | 60 MHz                                          | 3.1 M            | 32 GP<br>80 FPU                      | 64                                       | 4 GB                              | L1:16 KB                             |

| Pentium Pro Processor                          | 1995                    | 200 MHz                                         | 5.5 M            | 32 GP<br>80 FPU                      | 64                                       | 64 GB                             | L1: 16 KB<br>L2: 256 KB or<br>512 KB |

| Pentium II Processor                           | 1997                    | 266 MHz                                         | 7 M              | 32 GP<br>80 FPU<br>64 MMX            | 64                                       | 64 GB                             | L1: 32 KB<br>L2: 256 KB or<br>512 KB |

| Pentium III Processor                          | 1999                    | 500 MHz                                         | 8.2 M            | 32 GP<br>80 FPU<br>64 MMX<br>128 XMM | 64                                       | 64 GB                             | L1: 32 KB<br>L2: 512 KB              |

| Pentium III and Pentium III<br>Xeon Processors | 1999                    | 700 MHz                                         | 28 M             | 32 GP<br>80 FPU<br>64 MMX<br>128 XMM | 64                                       | 64 GB                             | L1: 32 KB<br>L2: 256 KB              |

| Intel<br>Processor      | Date<br>Intro-<br>duced | Microarchi-<br>tecture                   | Clock<br>Frequency<br>at Intro-<br>duction | Tran-<br>sistors | Register<br>Sizes <sup>1</sup>           | System<br>Bus<br>Band-<br>width | Max.<br>Extern.<br>Addr.<br>Space | On-Die<br>Caches <sup>2</sup>                                   |

|-------------------------|-------------------------|------------------------------------------|--------------------------------------------|------------------|------------------------------------------|---------------------------------|-----------------------------------|-----------------------------------------------------------------|

| Pentium 4<br>Processor  | 2000                    | Intel NetBurst<br>Microarchi-<br>tecture | 1.50 GHz                                   | 42 M             | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 3.2 GB/s                        | 64 GB                             | 12K µop<br>Execution<br>Trace<br>Cache;<br>8KB L1;<br>256-KB L2 |

| Intel Xeon<br>Processor | 2001                    | Intel NetBurst<br>Microarchi-<br>tecture | 1.70 GHz                                   | 42 M             | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 3.2 GB/s                        | 64 GB                             | 12K µop<br>Trace<br>Cache;<br>8-KB L1;<br>256-KB L2             |

| Intel<br>Processor                                                                | Date<br>Intro-<br>duced | Microarchi-<br>tecture                                                                               | Clock<br>Frequency<br>at Intro-<br>duction | Tran-<br>sistors | Register<br>Sizes <sup>1</sup>               | System<br>Bus<br>Band-<br>width | Max.<br>Extern.<br>Addr.<br>Space | On-Die<br>Caches <sup>2</sup>                                    |

|-----------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|----------------------------------------------|---------------------------------|-----------------------------------|------------------------------------------------------------------|

| Intel Xeon<br>Processor                                                           | 2002                    | Intel NetBurst Microarchi- tecture; Hyper- Threading Technology                                      | 2.20 GHz                                   | 55 M             | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 3.2 GB/s                        | 64 GB                             | 12K µop<br>Trace<br>Cache;<br>8-KB L1;<br>512-KB L2              |

| Intel Xeon<br>Processor<br>MP                                                     | 2002                    | Intel NetBurst Microarchi- tecture; Hyper- Threading Technology                                      | 1.60 GHz                                   | 108 M            | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 3.2 GB/s                        | 64 GB                             | 12K µop<br>Trace<br>Cache;<br>8-KB L1;<br>256-KB L2;<br>1-MB L3  |

| Intel Pentium 4 Processor Supporting Hyper- Threading Technology                  | 2002                    | Intel NetBurst Microarchi- tecture; Hyper- Threading Technology                                      | 3.06 GHz                                   | 55 M             | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 4.2 GB/s                        | 64 GB                             | 12K µop<br>Execution<br>Trace<br>Cache;<br>8-KB L1;<br>512-KB L2 |

| Intel<br>Pentium M<br>Processor                                                   | 2003                    | Intel Pentium<br>M Processor                                                                         | 1.60 GHz                                   | 77 M             | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 3.2 GB/s                        | 4 GB                              | L1: 64 KB<br>L2: 1 MB                                            |

| Intel Pentium 4 Processor Supporting Hyper- Threading Technology at 90 nm process | 2004                    | Intel NetBurst<br>Microarchi-<br>tecture;<br>Hyper-<br>Threading<br>Technology                       | 3.40 GHz                                   | 125 M            | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 6.4 GB/s                        | 64 GB                             | 12K µop<br>Execution<br>Trace<br>Cache;<br>16 KB L1;<br>1 MB L2  |

| Intel<br>Pentium M<br>Processor<br>755 <sup>3</sup>                               | 2004                    | Intel Pentium<br>M Processor                                                                         | 2.00 GHz                                   | 140 M            | GP: 32<br>FPU: 80<br>MMX: 64<br>XMM: 128     | 3.2 GB/s                        | 4 GB                              | L1: 64 KB<br>L2: 2 MB                                            |

| 64-bit Intel<br>Xeon<br>Processor<br>with 800<br>MHz System<br>Bus                | 2004                    | Intel NetBurst Microarchi- tecture; Hyper- Threading Technology; Intel Extended Memory 64 Technology | 3.60 GHz                                   | 125 M            | GP: 32, 64<br>FPU: 80<br>MMX: 64<br>XMM: 128 | 6.4 GB/s                        | 64 GB                             | 12K µop<br>Execution<br>Trace<br>Cache;<br>16 KB L1;<br>1 MB L2  |

Clock Intel Date Microarchi-Tran-Register System Max. On-Die Caches<sup>2</sup> Intro-Frequency sistors Sizes<sup>1</sup> Bus Extern. **Processor** tecture at Intro-Band-Addr. duced duction width **Space** 64-bit Intel 2005 Intel NetBurst 3.33 GHz 675M GP: 32, 64 5.3 GB/s <sup>4</sup> 1024 GB 12K µop FPU: 80 Xeon Microarchi-(1 TB) Execution MMX: 64 Trace Processor tecture: XMM: 128 Hyper-MP with Cache: 8MB L3 Threading 16 KB L1: Technology: 1 MB L2, Intel Extended 8 MB L3 Memory 64 Technology 2005 Intel NetBurst 3.73 GHz 164 M GP: 32, 64 8.5 GB/s 64 GB Intel 12K µop FPU: 80 Pentium 4 Microarchi-Execution MMX: 64 tecture: Trace Processor XMM: 128 Extreme Hyper-Cache: 16 KB L1; Edition Threading 2 MB L2 Supporting Technology: Hyper-Intel Extended Memory 64 Threading Technology Technology 3.20 GHz 230 M GP: 32, 64 6.4 GB/s 64 GB Intel 2005 Intel NetBurst 12K µop FPU: 80 Execution Pentium Microarchitecture: MMX: 64 Trace Processor Extreme Hyper-XMM: 128 Cache: Edition 840 Threading 16 KB L1: 1MB L2 Technology: Intel Extended (2MB Total) Memory 64 Technology: Dual-core <sup>5</sup>

N. Joppi et. al., ISCA, 2002

# 13.1汎用プロセッサの高速化・省電力化(1)大域並列の利用:

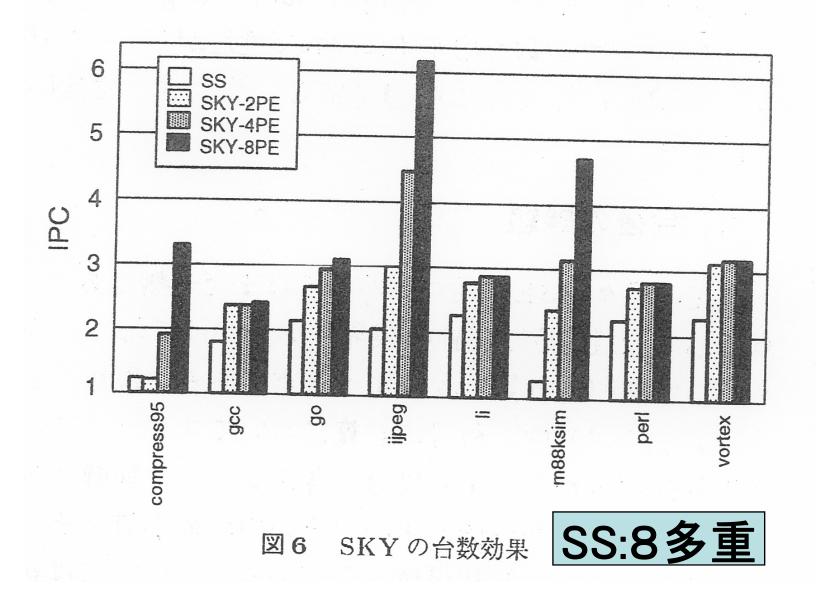

マルチスレッド/マルチプロセッサ スーパスカラ、VLIW:単一プロセス/ スレッドの高速化

複数プロセスシスレッドの高速化パソコン内:数10個のプロセス

Intel Hyperthreading,

NEC MUSCAT, 名大 SKY,

Wisconsin Multiscalar

**IBM POWER4**

オンチップマルチプロセッサ (CMP)

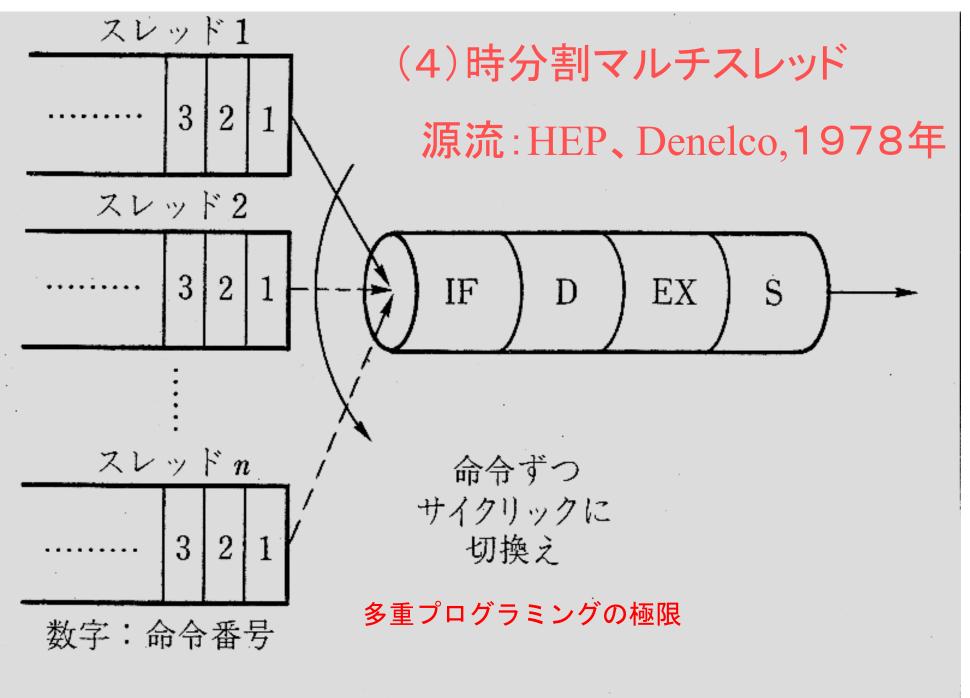

# マルチスレッド型プロセッサ

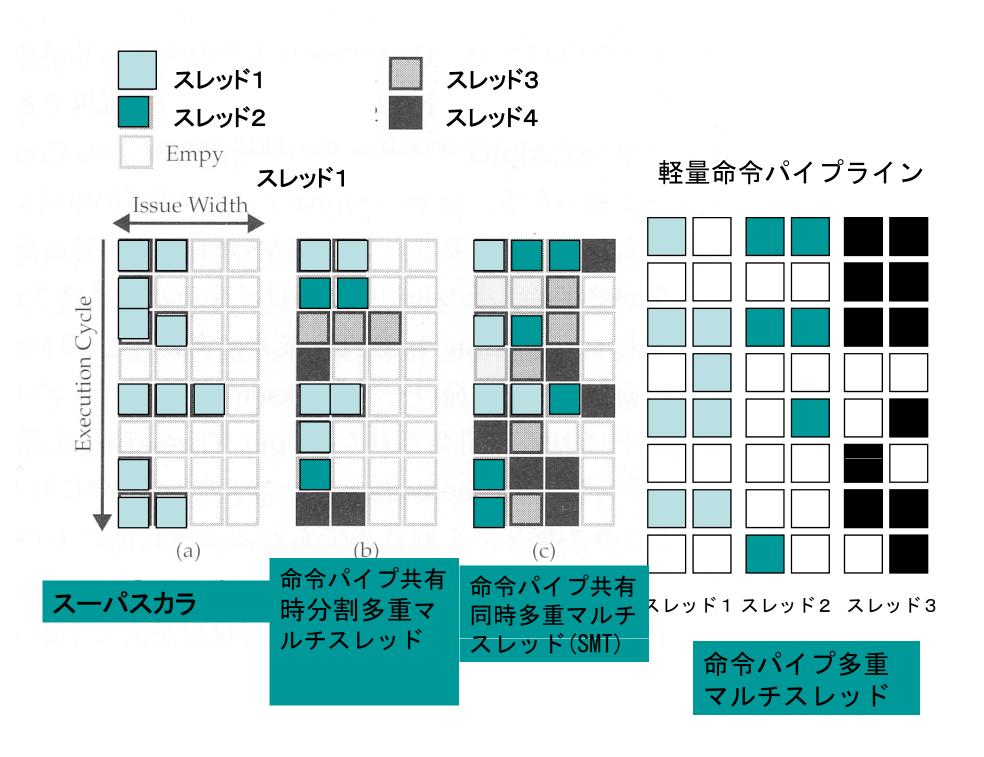

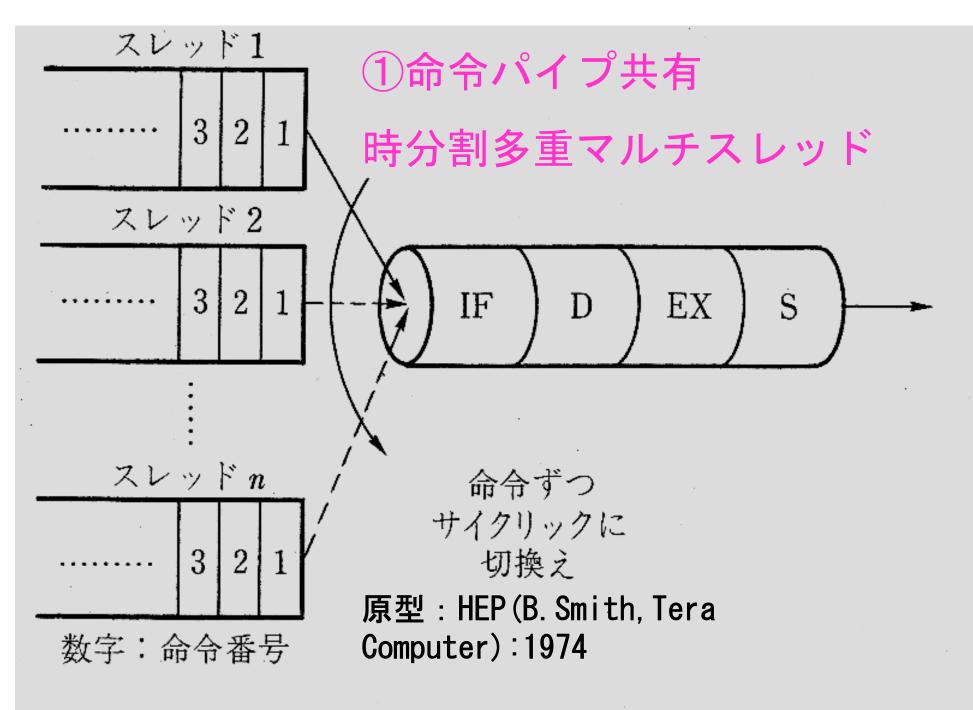

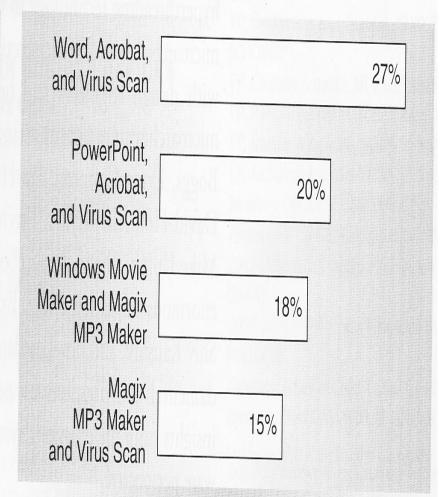

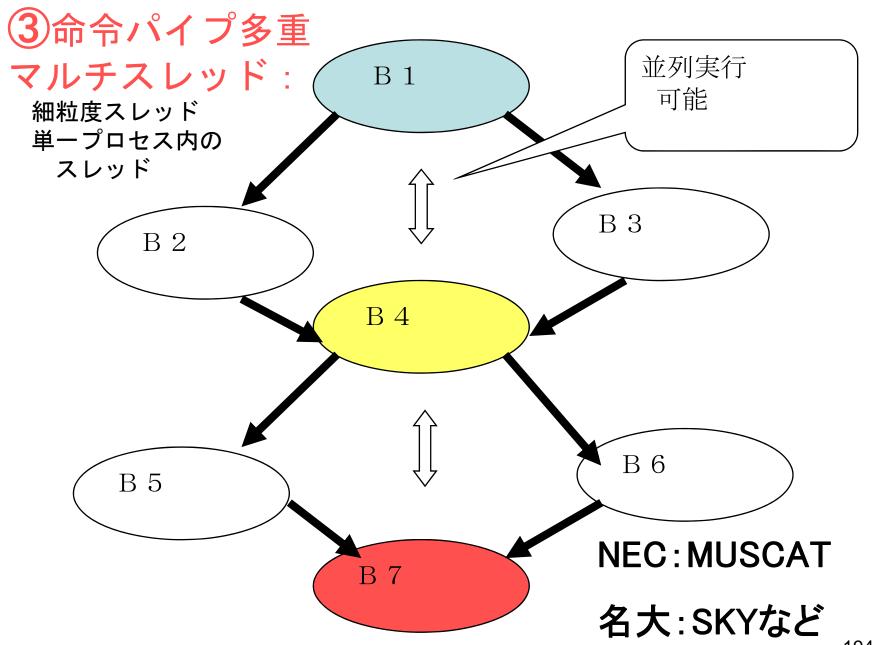

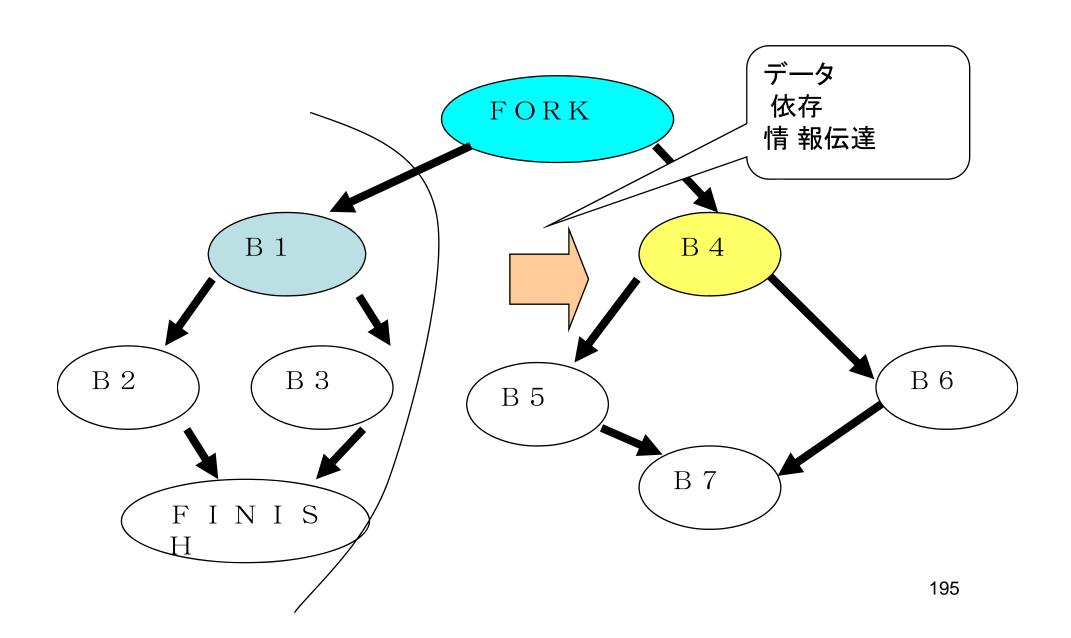

- ①命令パイプ共有時分割多重マルチスレッド (粗粒度、細粒度)

- Temporal Multi-Threading (TMT)

- ②命令パイプ共有同時多重マルチスレッド Simultaneous Multi-Threading(SMT)

- ③命令パイプ多重マルチスレッド

- ④CMP(チップマルチプロセッサ)

共有命令パイプライン方式

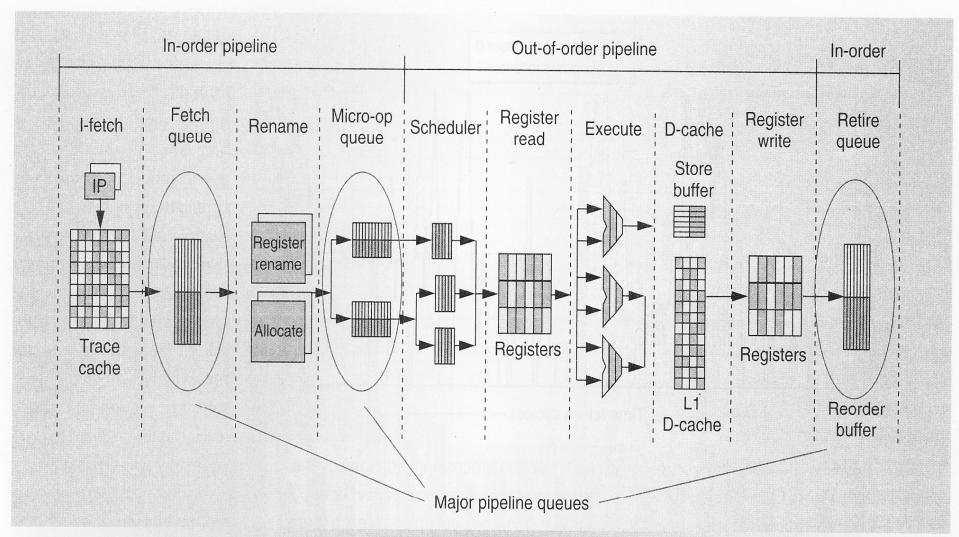

# **2SMT** Simultaneous Multithreading

命令パイプ共有同時多重マルチスレッド

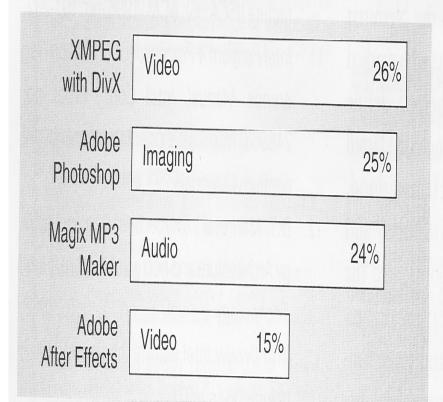

基本命令パイプライン: 1つ +複数のレジスタ、PCなど 多数のスレッドの実行 Intel Hyper Threading 15-25%性能向上、 チップサイズ5%増 2スレッド実行

Figure 4. In this view of a Netburst microarchitecture's execution pipeline, the light and dark areas indicate the resource utilization of the two software threads running on the two logical processors.

Figure 7. Hyperthreading technology performance gains on several popular multithreaded software packages.

Figure 8. Hyperthreading technology performance boost on multitasking workloads.

# 命令パイプ多重マルチ スレッド実行

B2を投機実行

B5を投機実行

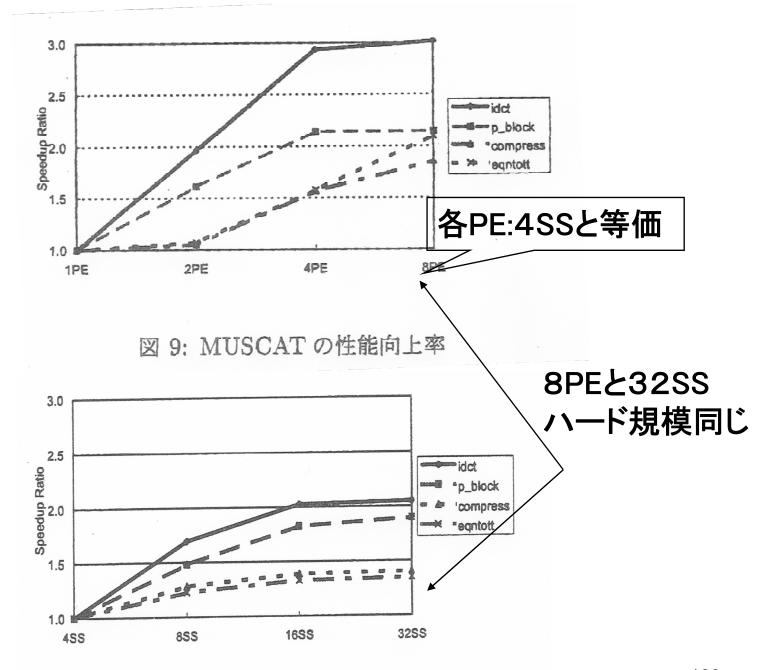

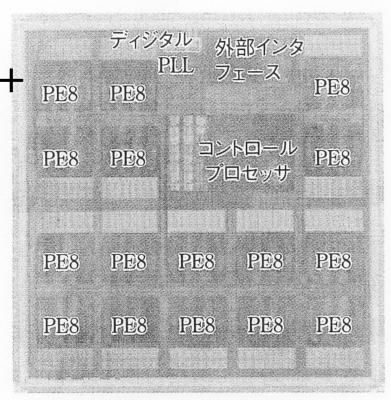

### NEC MUSCAT

表 2: シミュレーションパラメタ

| 項目        | パラメタ                                |

|-----------|-------------------------------------|

| 各 PE の構造  |                                     |

| パイプライン    | IF, ID, Issue/Reg, EX, WB, Graduate |

|           | Issue/Reg から WB まで out-of-order 実行  |

| 命令ウィンドウ   | PE 毎 32 命令 (整数 / ロードストア各 16)        |

| 演算リソース    | ALU 2×PE数 L/Sパイプ1×PE数               |

| ロード / ストア | 3 サイクルレイテンシ                         |

| スーパスカラ度   | 4 命令同時デコード / 終了                     |

| 分岐投機      | 4 分岐まで仮実行                           |

| 分岐履歴      | 2048entry 4 状態 (PE 間共有)             |

| キャッシュ     |                                     |

| キャッシュ方式   | 命令/データ分離                            |

| キャッシュ容量   | 各 32Kbyte (64byte × 512entry)       |

| マッピング方式   | 4Way Set Associative LRU 追い出し       |

|           |                                     |

鳥居、近藤、本村、西、小長谷: On Chip Multiprocessor 指向制御並列アーキテクチャMUSCATの提案、JSPP97、pp.229-236、1997 197

図 11: スーパスカラ強化モデルの性能向上率

小林、岩田、安藤、島田: 非数値計算プログラムのスレッド 間命令レベル並列を利用するプロセッサアーキテクチャSKY、 JSPP98、pp。87-94、1998

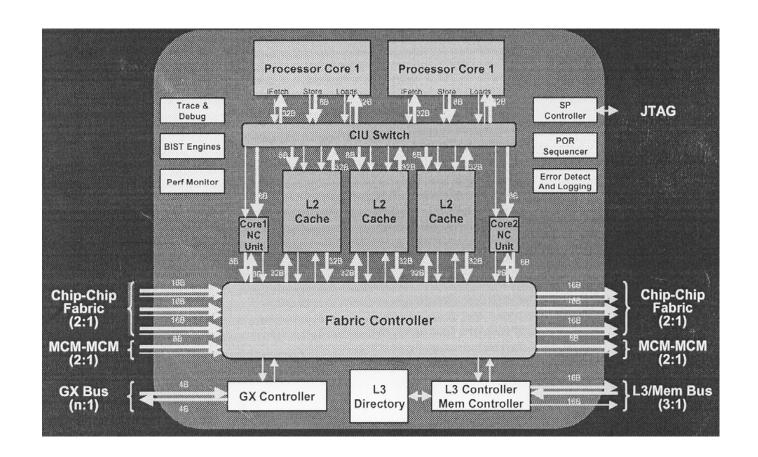

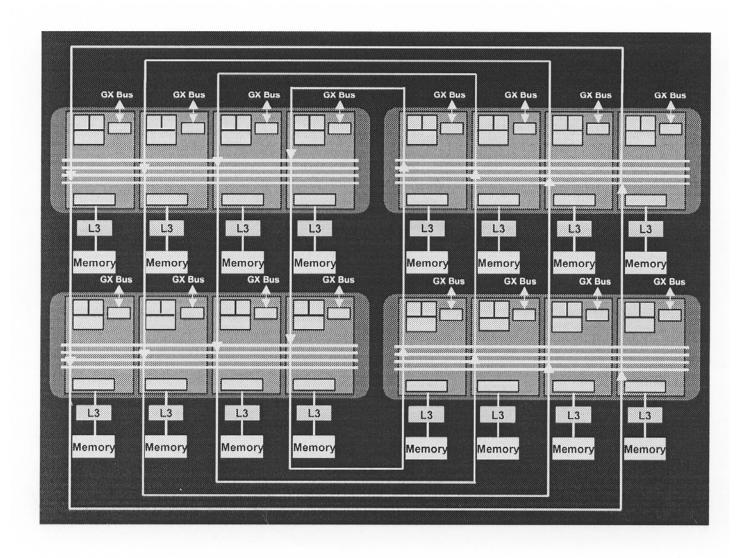

## ④オンチップマルチプロセッサ CMP

- IBM POWER4: 2台のSMP、スヌープキャッシュ

- MCM: 8台までのSMP、最大構成: 4 MCM (32台)

- L1 (I: 6 4 KBx2,D: 3 2 KBx2): 2 状態、L2 (1. 5 MB)

- 7 状態、L3 (3 2 MB): 5 状態

Figure 9: Multiple POWER4 multi-chip module interconnection

# Pentium EE840

```

デュアルコアプロセッサ

各プロセッサ:ハイパースレッデイング

9 Onmデザインルール

3. 2GHz

各プロセッサ

L1データキャッシュ: 16KB

L1トレースキャッシュ12KB

L2キャッシュ: 1 MB

SSE3

```

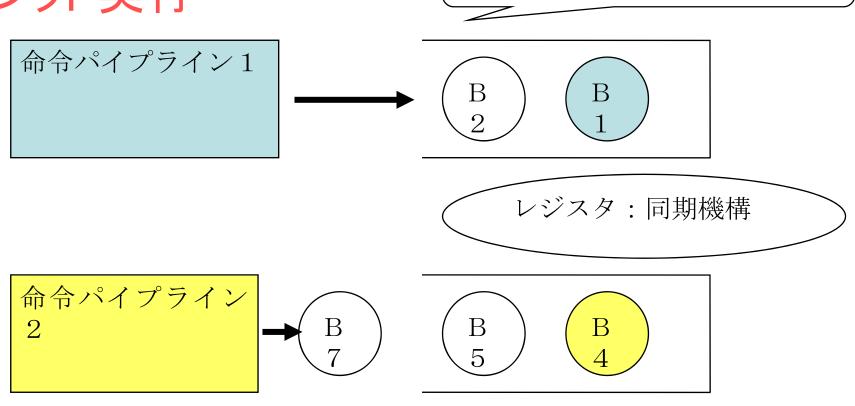

#### ●複数ソフトの同時実行に威力を発揮 性能ランキングテストの結果(標準機の結果を100とした相対値) 20 40 80 60 100 **Pentium** 101 **EE 840** Pentium 4 109 **EE 3.73GHz** 70 Pentium 4 100 3.4GHz テストのみ実行したときの結果 動画圧縮と同時実行したときの結果 ソフト同時実行テストの処理時間

デュアルコアはテスト単体を動かしたときは、その真価は発揮されない。複数のソフトを同時実行すると、全処理問 間がほかよりも短くなる。いろいろなソフトを同時に動かしたいユーザーにお薦めだ

#### テストの詳細

Pentium EE 840機: CPUはPentium EE 840(3.2GHz)、メモリーはDDR 2 667対応1GB、HDDは7200回転/分の250GB、グラフィックスはRADEON X850 XT 256MB

Pentium 4 EE機: CPUはPentium 4 EE (3.73GHz)、他はPentium EE 840機と同じ

Pentium 4機: CPUはPentium 4(3.4GHz)、メモリーはDDR 2 533対応1GB、HDDは7200回転/分の300GB、グラフィックスはRADEON X600Pro 128MB

上の図は性能ランキングテストのみと、動画圧縮をしながら性能ランキングテストを動かしたときの結果。下の図は動画圧縮しながら性能ランキングテストを動かしたときにかかった時間

## 日経パソコン 2005. 5. 9

Figure 2. Block diagram of Intel's Montecito. The dual cores and threads realize performance unattainable in the Itanium 2 processor. Montecito also addresses Itanium 2 port asymmetries and inefficiencies in branching, speculation, and cache hierarchy.

Itanium2-Montecito

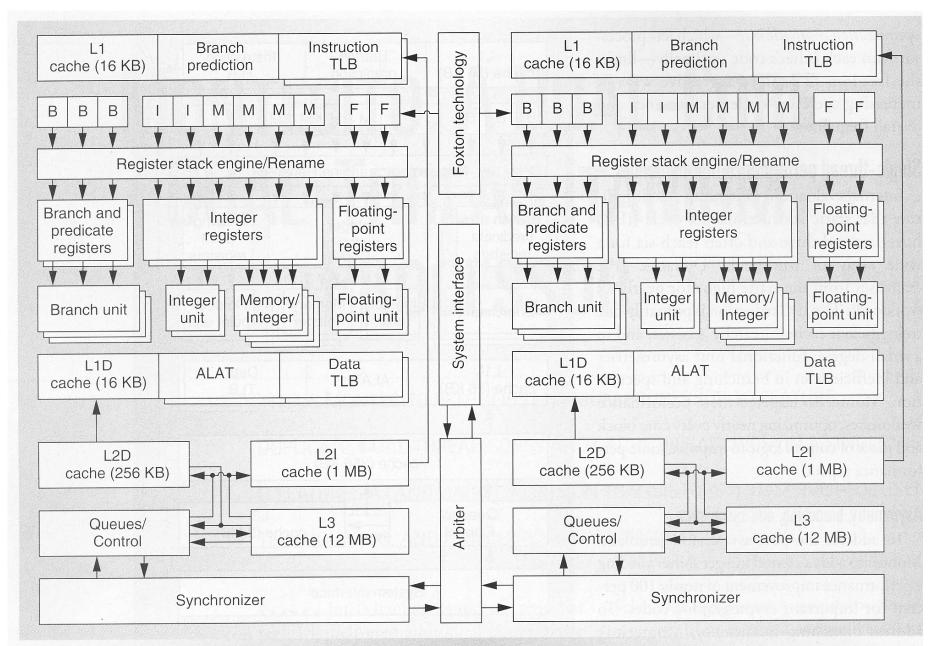

2個のItanium2プロセッサ、2スレッド 時分割多重マルチスレッド命令パイプ共有(TMT) 各クロセッサ

L1キャッシュ16KB、1サイクル

L2キャッシュ1MB、5サイクル

L3キャッシュ12MB、14サイクル

スレッドスイッチ:15サイクル(粗粒度TMT)

L3キャシュミス、タイムアウトなど5つの事象

1.72億TR

消費電力:100W

周波数: 1.8GHz IEEE Micro Vol 25 No 2 2005

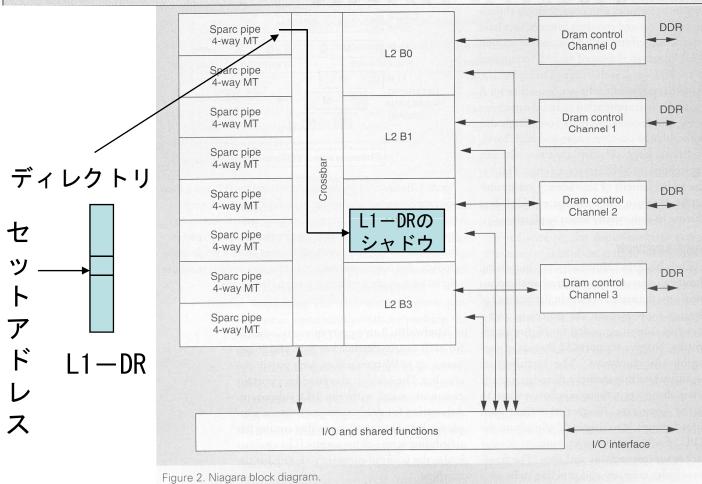

## SPARC: Niagara

1多重で6ステージのSPARCプロセッサ 8台 各プロセッサ:4スレッド 時分割多重マルチスレッド命令パイプ共有 (細粒度TMT)

L1キャッシュ: 8 KB、Write Through

L2キャッシュ: 3 MB、4 バンク、クロスバSWで共有 対応するバンクにL1キャッシュディレクトリのシャドウ 命令レベル並列が小さく、

スレッドレベル並列の大きなWEBやデータベース応用向き

| Table 1. Commercial server applications. |                              |                               |                          |                |              |  |  |

|------------------------------------------|------------------------------|-------------------------------|--------------------------|----------------|--------------|--|--|

| Benchmark                                | Application category         | Instruction-level parallelism | Thread-level parallelism | Working<br>set | Data sharing |  |  |

| Web99                                    | Web server                   | Low                           | High                     | Large          | Low          |  |  |

| JBB                                      | Java application server      | Low                           | High                     | Large          | Medium       |  |  |

| TPC-C                                    | Transaction processing       | Low                           | High                     | Large          | High         |  |  |

| SAP-2T                                   | Enterprise resource planning | Medium                        | High                     | Medium         | Medium       |  |  |

| SAP-3T                                   | Enterprise resource planning | Low                           | High                     | Large          | High         |  |  |

| TPC-H                                    | Decision support system      | High                          | High                     | Large          | Medium       |  |  |

森: 日経Micro devices, No242, 2005

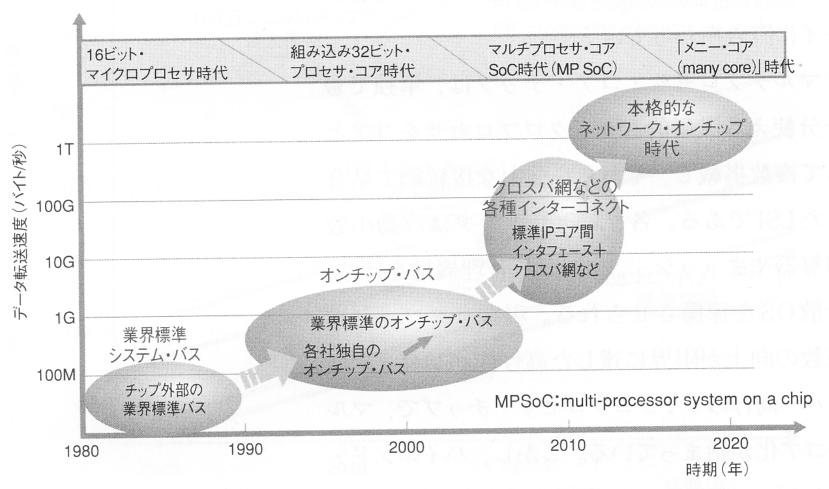

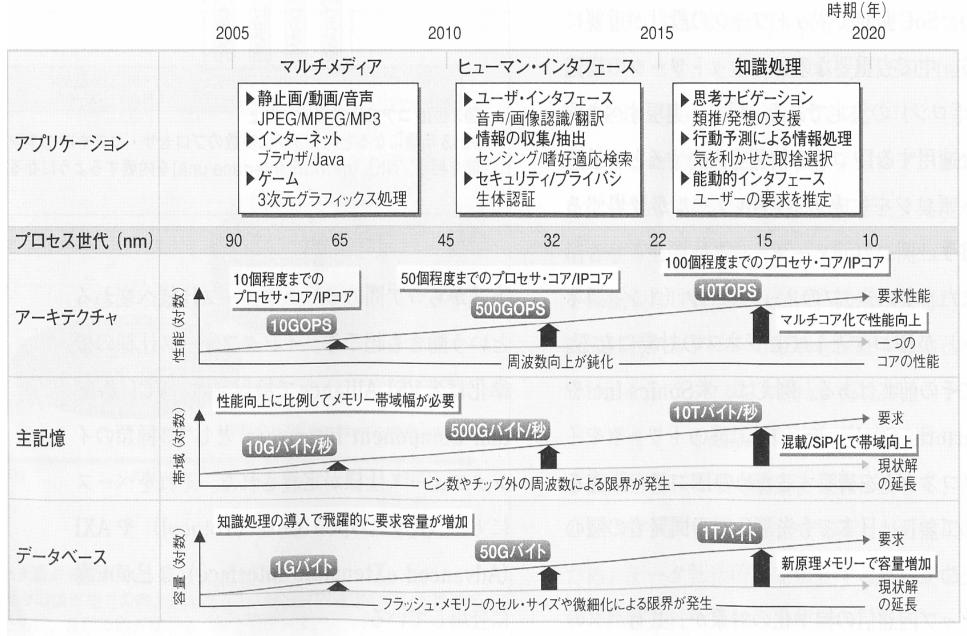

## 図1 ●チップ内通信のデータ転送速度が向上

チップに集積できるプロセサの演算能力の向上にあわせて、チップ内通信のバンド幅が拡大する。それを実現するために、通信手段が変わる。著者のデータ。

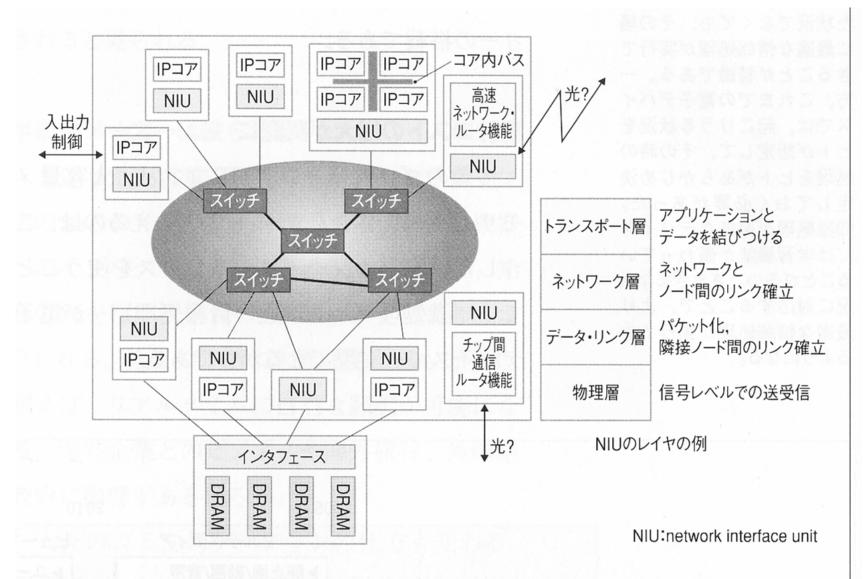

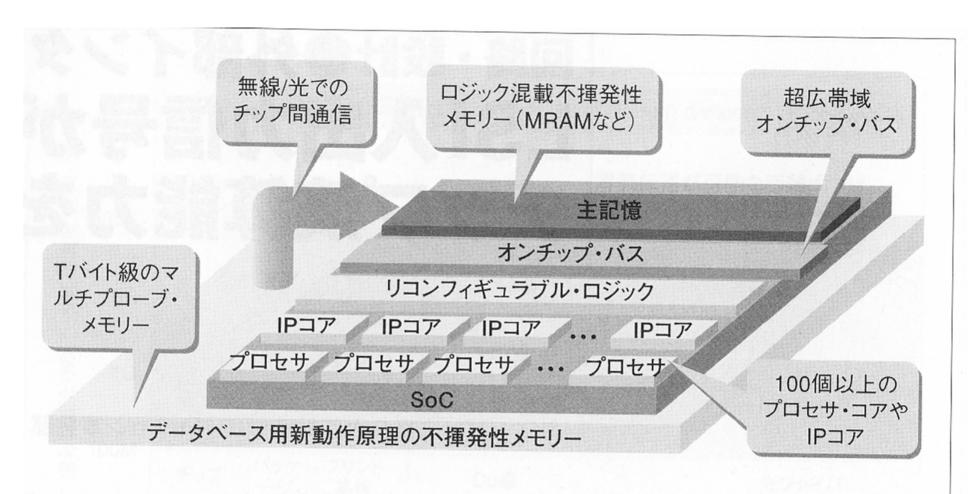

#### 図3 IPコアの通信機能が向上

2015年頃になると、チップに多数のプロセサ・コアやIPコアが載る。各IPコアが通信機能を担う、NIU (network interface unit)を内蔵するようになる。著者のデータ。

川崎、小沢:日経Micro devices, No242, 2005

## 図2 2015年のSoCアーキテクチャ

ローカル(SoC付近)に必要なデータベースの実現には、マルチプローブ・メモリーなどの次世代不揮発性メモリーが必要になる。著者のデータ。

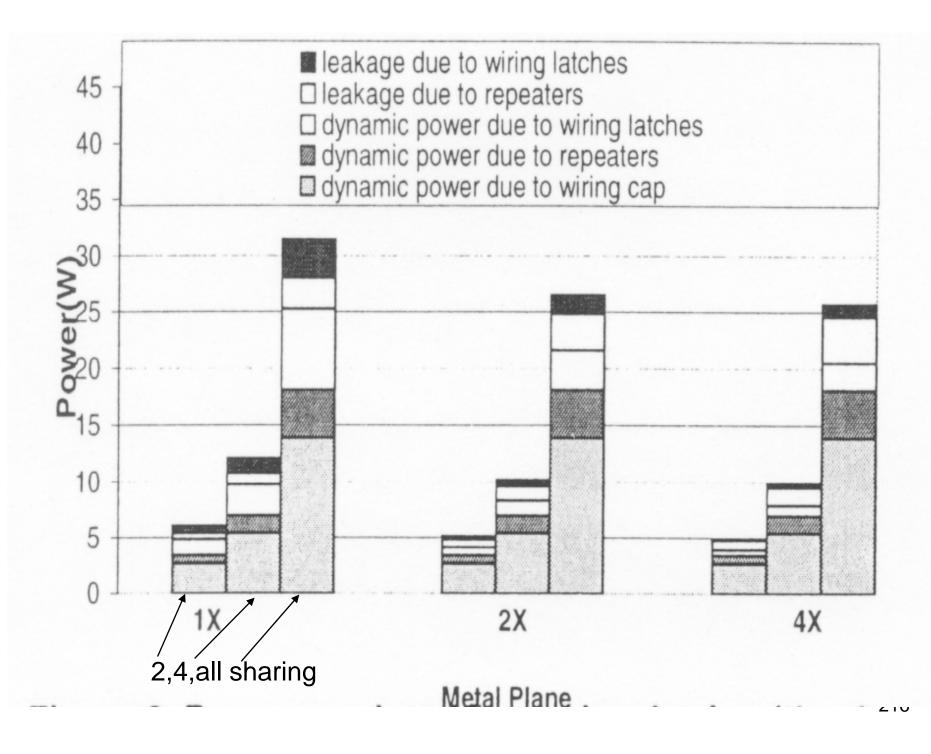

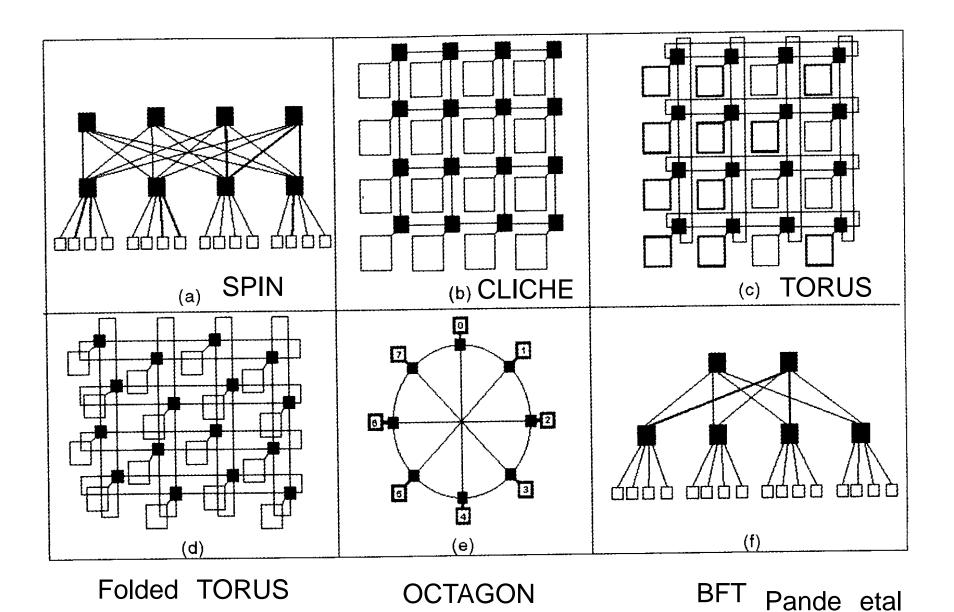

## マルチコアの相互結合網

### 評価項目

- ①スループット

- ②レイテンシ

- ③消費電力: スイッチ+配線

- 4面積

- 5配線層数

- •P.P.Pande etal: Performance Evaluation and Design Trade-offs for Network-on-Chip Interconnect Architectures, IEEE Trans. Computers, Vol54, No.8,pp.1025-1040,2005

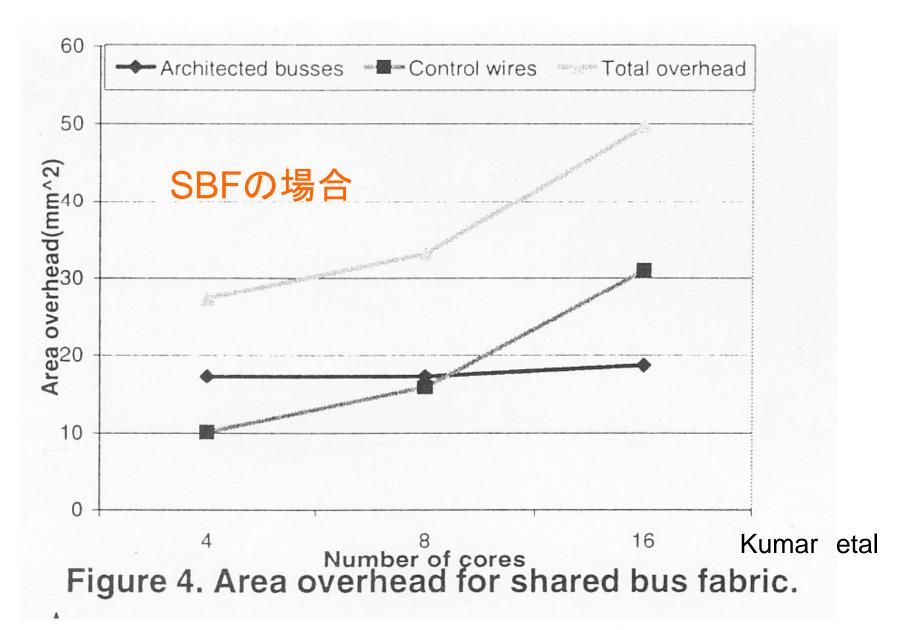

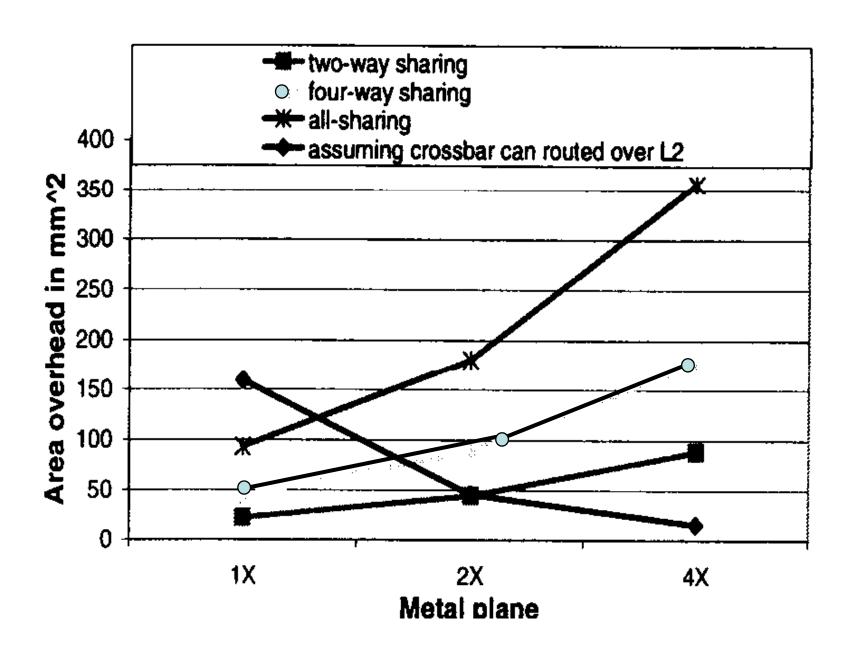

- •R.Kumar etal: Interconnections in Multi-core Architectures: Understanding Mechanisms, Overhead, and Scaling, pp.408-419, ISCA, 2005

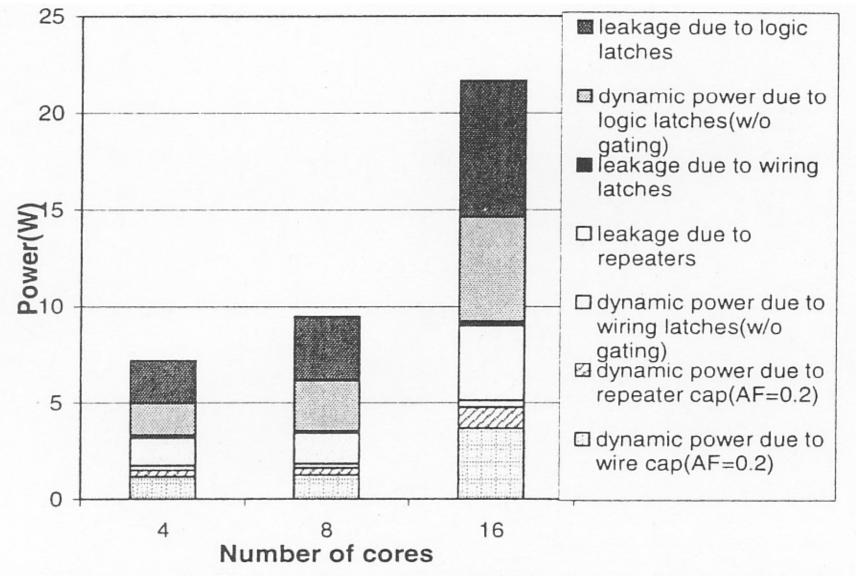

16コアで配線面積50mm<sup>2</sup> ⇔65nmデザイン、ダイサイズ: 400mm<sup>2</sup>、1コア: 10 mm<sup>2</sup>、L2キャッシュ: 0.125MB/mm<sup>2</sup>を仮定

ロジック(L2の下): 5.6mm²(4コア)、8.6mm²(8コア)、17.94mm²(16コア)

# 8コアX8L2キャッシュバンクのクロスバスイッチ

Figure 5. Power overhead for shared bus fabric.

1コア(Power4):10W

オーバヘッド: 2コア分に相当(22mm² 16コアの場合)

SPIN:Scalable,Programmable,Integrated Network, CLICHÉ: Chip-Level Integration of Communicating Heterogeneous Elements, BFT:Butterfly Fat Tree

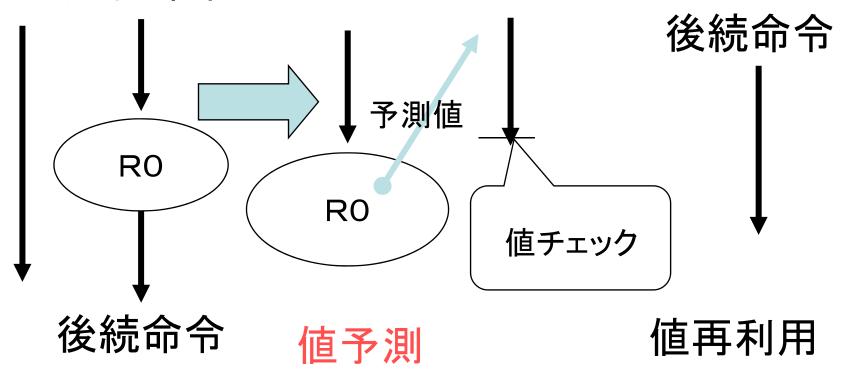

## (2) データ投機実行

未商用化 分岐予測

データ依存を超えて

制御依存を超えて

- ①值予測

- ②值再利用

## フロ一依存

## 同時実行

先行命令実行せず

先行命令 先行命令 後続命令

## ①值予測

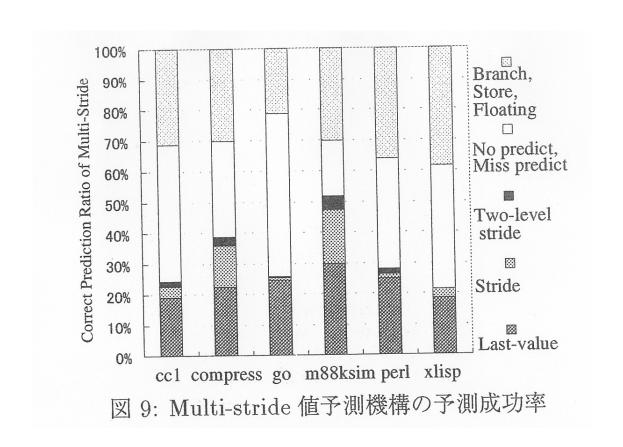

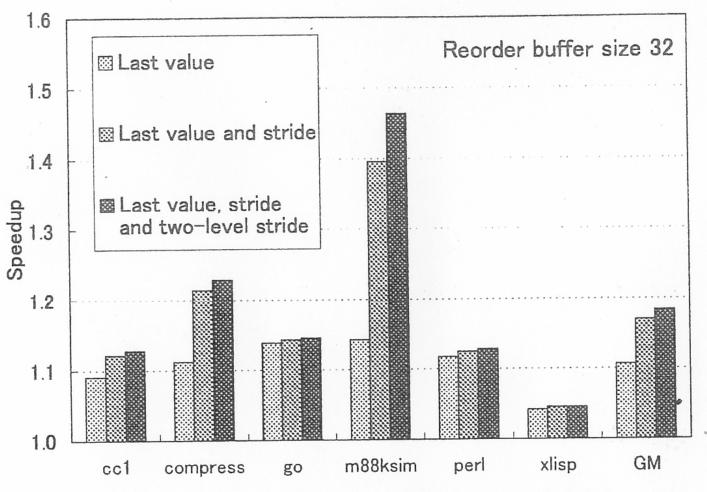

Last-Value値、ストライド値、2レベルストライド値などで予測

吉瀬、坂井、 田中:JSPP99

図 10: Multi-stride 値予測機構による性能向上率

吉瀬、坂井、 田中:JSPP99

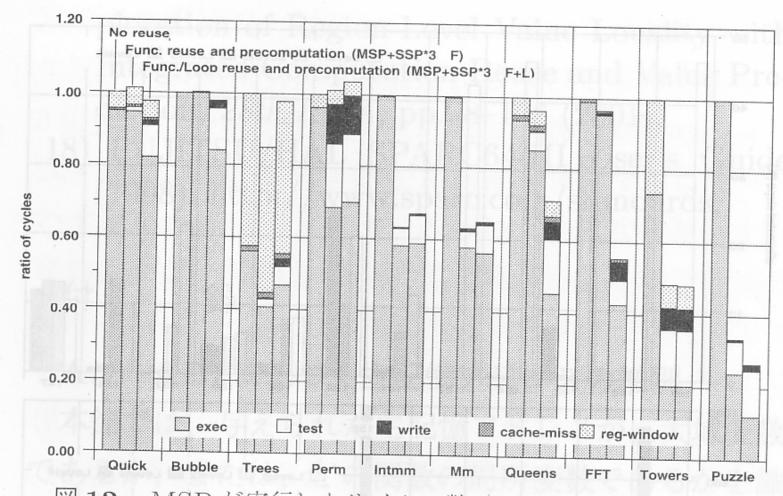

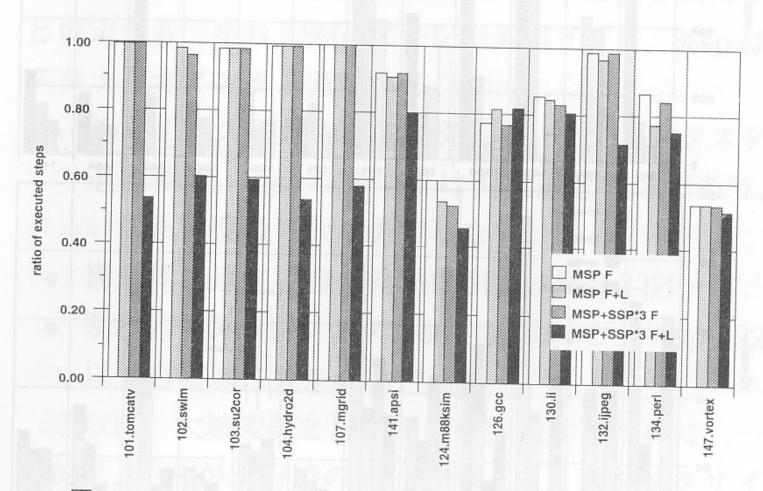

#### ②值再利用

- ・同一パラメータによる関数・ループ 実行自体の省略

- 事前実行による値再利用の可能性の増大化

- ・データ値の許容範囲設定による値再利用の 可能性の増大化

図 12 MSP が実行したサイクル数 (Stanford-Integer).

Fig. 12 Executed cycles on MSP (Stanford-Integer).

図13 MSP が実行した命令ステップ数 (SPEC95). Fig. 13 Executed steps on MSP (SPEC95).

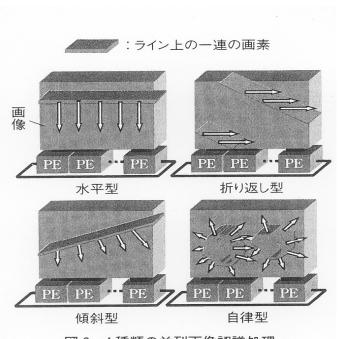

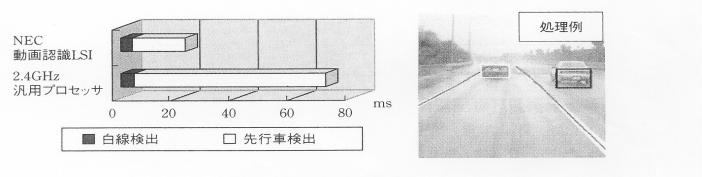

## 13.2 メディアプロセッサ

CG:浮動小数点演算、4×4行列演算

SH-4:500万ポリゴン/秒

プレステ2:1600万ポリゴン/秒

画像: MPEG

符号化: 100GOPS,

復号化: 10GOPS

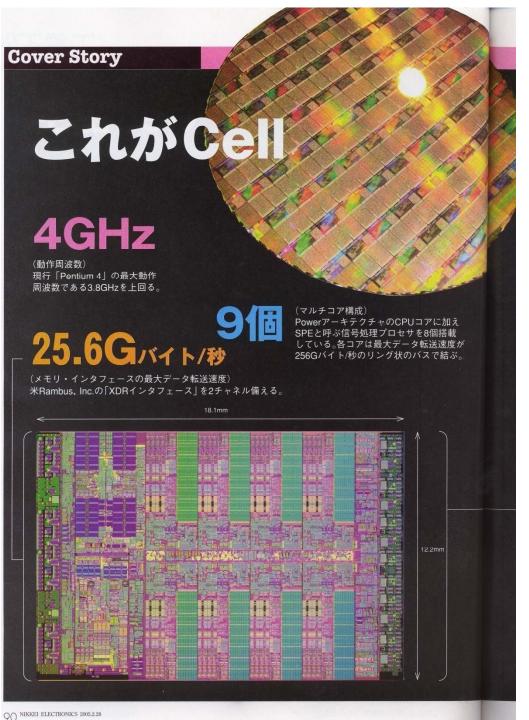

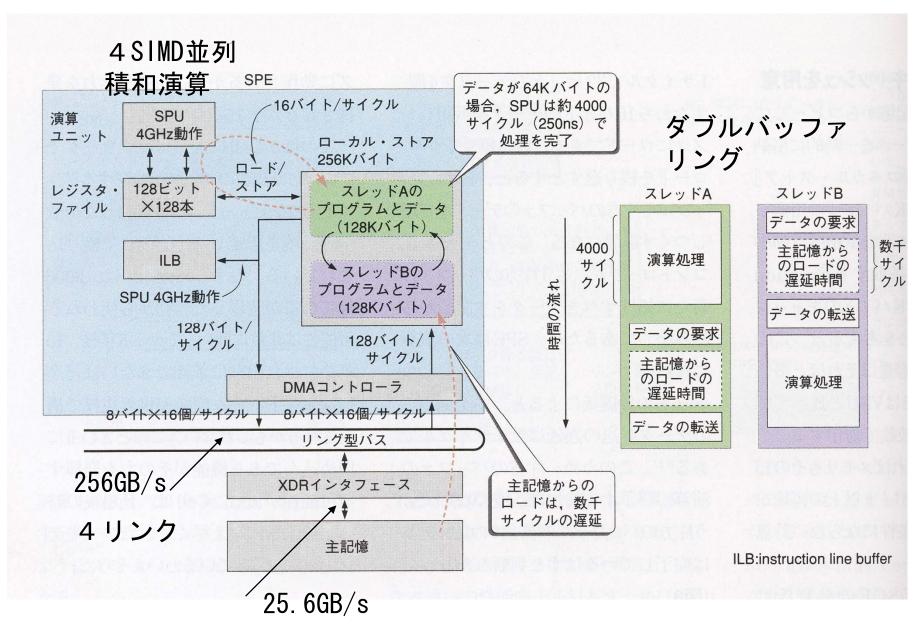

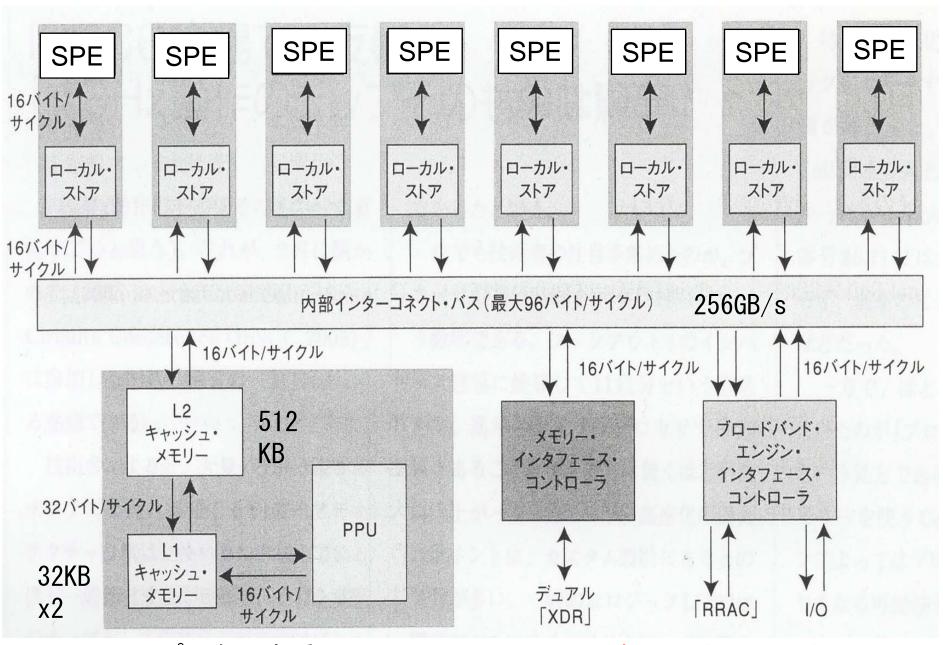

## (1) Sony:Cell マルチコア:ヘテロジニアス構成

1個のPPE:Power Processor Element IBM Power Architecture

2多重スーパスカラ、乱実行なし、

分岐予測なし、非常にシンプル

8個のSPE: Synergistic Prosessing Element

4 SIMD並列積和演算

4 GHz X 8 : 256 GFL OPS

相互結合: リングバス、256GB/s

応用:マルチメディア

日経エレクトロニ クス2005.2.28

## 256GFLOPS

(SPEの演算性能) 各SPEはSIMD命令によって32ビット浮動 小数点データの積和演算を4個並列に1サイ クルのスループットで処理可能。

## 1236端子

(パッケージ) 「Pentium 4」の約1.6倍。チップ上には2965個の C4バンプを形成してある。

### 2億3400万個

(トランジスタの数) 「Pentium 4」の約2倍。このうち8個の SPEの論理回路に合計5600万個を使う。

#### マルチスレッド

(メモリ管理の強化による支援) 各SPEに集積したDMAコントローラがメモリ管理を行う。 メモリ管理ユニットのアドレス変換テーブルをCPUコアが 制御するこで、並列処理するスレッドの動作を保証する。 SPEが専用メモリ空間へのCPUコアのアクセスを禁じる 動作モードを用意。

## **46nm**

(ゲート長) 90nmルールのSOI技術で製造。8層の Cu配線技術とひずみSi技術を使う。

## 仮想化

(複数OSの並列実行) 複数のOSを並列に動かすソフトウエアの 実行環境を実装。演算資源の割り当てを 保証しリアルタイム処理を可能に。

## 76.8Gバイト/秒

(システム・インタフェースの 最大データ転送速度) 米IBM Corp.の「POWER5」の 64Gバイト/秒を凌駕する。 「Pentium 4」や「Itanium 2」に 比べて10倍以上に当たる。 物理層には米Rambus、Inc.の 「FlexIO」を用いる。

|                      | Cell                   | Emotion Engine           |

|----------------------|------------------------|--------------------------|

| 発表時期                 | 2005年                  | 1999年                    |

| 動作周波数                | 4GHz                   | 300MHz                   |

| 32ビット浮動小数点データの演算性能   | 256GFLOPS              | 6.2GFLOPS                |

| トランジスタ数              | 2億3400万個               | 1350万個                   |

| 発売時の設計ルール            | 90nm                   | 250nm                    |

| 基板                   | SOI                    | バルクSi                    |

| チップ面積                | 221mm² (18.1mm×12.2mm) | 226mm² (15.02mm×15.04mm) |

| CPUコア                | Power(2命令同時発行)         | MIPS(2命令同時発行)            |

| 信号処理プロセサ             | 128ビットのSIMD型×8個        | 128ビットのVLIW型×2個          |

| メモリ・インタフェースのデータ転送速度  | 最大25.6Gバイト/秒           | 最大3.2Gバイト/秒              |

| システム・インタフェースのデータ転送速度 | 最大76.8Gバイト/秒           | 最大1.2Gバイト/秒              |

| パッケージ                | 1236端子のBGA             | 540端子のプラスチックBGA          |

|                      | Cell                   | Emotion Engine           |

|----------------------|------------------------|--------------------------|

| 発表時期                 | 2005年                  | 1999年                    |

| 動作周波数                | 4GHz                   | 300MHz                   |

| 32ビット浮動小数点データの演算性能   | 256GFLOPS              | 6.2GFLOPS                |

| トランジスタ数              | 2億3400万個               | 1350万個                   |

| 発売時の設計ルール            | 90nm                   | 250nm                    |

| 基板                   | SOI                    | バルクSi                    |

| チップ面積                | 221mm² (18.1mm×12.2mm) | 226mm² (15.02mm×15.04mm) |

| CPUコア                | Power(2命令同時発行)         | MIPS(2命令同時発行)            |

| 信号処理プロセサ             | 128ビットのSIMD型×8個        | 128ビットのVLIW型×2個          |

| メモリ・インタフェースのデータ転送速度  | 最大25.6Gバイト/秒           | 最大3.2Gバイト/秒              |

| システム・インタフェースのデータ転送速度 | 最大76.8Gバイト/秒           | 最大1.2Gバイト/秒              |

| パッケージ                | 1236端子のBGA             | 540端子のプラスチックBGA          |

PPE シンプルな2多重 スーパスカラ

日経エレクトロニクス231 2005. 2. 28

| 項目                       | 「Cell」の仕様                                                          |

|--------------------------|--------------------------------------------------------------------|

| 汎用プロセサ・コアの種類             | 64ビット「Power Architecture」(PPE), SIMD構造とローカル・ストアを持つRISCアーキテクチャ(SPE) |

| プロセサ・コアの数 (個)            | PPEが1, SPEが8                                                       |

| 動作周波数(Hz)                | 最大4.6G                                                             |

| L1キャッシュ・メモリー [命令] (バイト)  | 32K                                                                |

| L1キャッシュ・メモリー [データ] (バイト) | 32K                                                                |

| L2キャッシュ・メモリー (バイト)       | 512K                                                               |

| 外付けメイン・メモリー              | XDR DRAM                                                           |

| メモリーのバス・バンド幅(バイト/秒)      | 25.6G                                                              |

| 浮動小数点演算ユニット(個)           | 36個[単精度],9個[倍精度]                                                   |

| 浮動小数点演算性能(FLOPS/チップ)     | 256G[単精度] ·                                                        |

| データ・バス幅(ビット)             | 1024[内部]                                                           |

| プロセス                     | 90nm, SOI, 8層Cu配線                                                  |

| ゲート長 (nm)                | 46                                                                 |

| 消費電力(W)                  | 70~80W                                                             |

| トランジスタ数(個)               | 2億3400万                                                            |

| チップ面積 (mm²)              | 221                                                                |

#### 図3 『Cell』の主な仕様

「ISSCC 2005」で発表された試作チップ。公表値やヒアリングを基に本誌が作成。

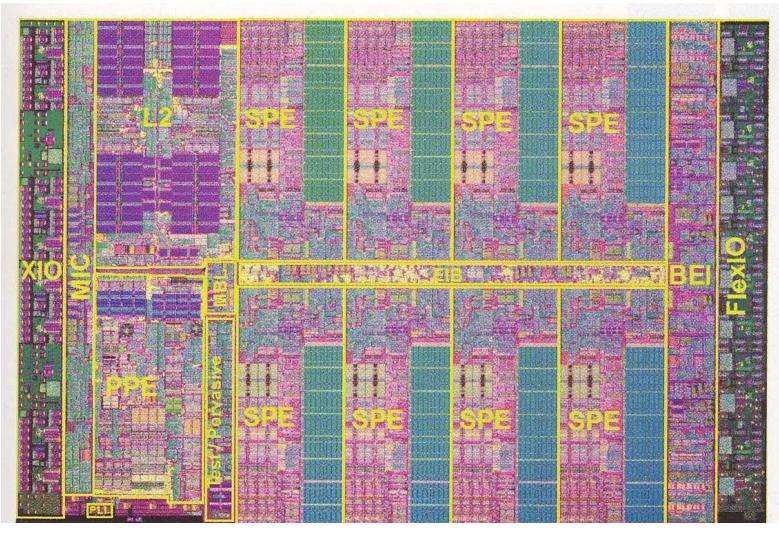

## 図1 試作チップ のレイアウト

90nmルールのSOI 技術を使い約2億 3400万個のトラン ジスタを18.1mm× 12.2mmのチップに 集積した。

BEI: broadband engine

interface

EIB: element inter-

connect bus

MBL: MIC Bus Logic

MIC: memory inter-

face controller

PPE: power proces-

sor element

SPE: synergistic pro-

cessing element

XIO: XDR i/o interface

保有する核兵器の信頼性

同開発。

#### 木曜 日

# 搭頭 載に

う一ペタフロップス (一秒間に千兆回) にも使われる高性能半導体「セル」を採用。セルがスパコンに搭載されるのは初めてという。 ユータエンタテインメント たと発表した。核兵器の模擬実験などに使うのが目的で、スパコンの頭脳部にはソニー・ ワシントン6日共同 米エネルギ (SCE) が今秋発売するゲーム機 のスーパーコンピューターの設計・製造を米IBMに発注 省核安全保障局は六日、最大演算速度が「世界最高」 「プレイステーション (PS) 3