# 第7章 並列処理

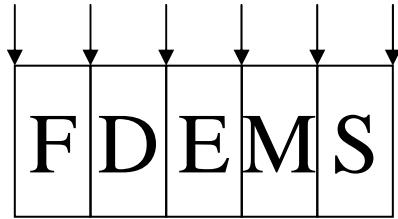

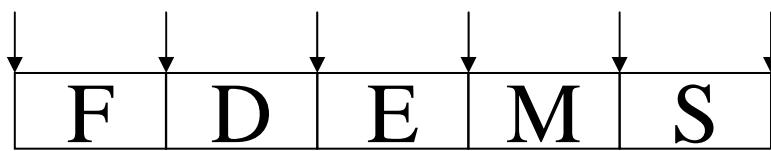

## 7.1 並列処理の分類

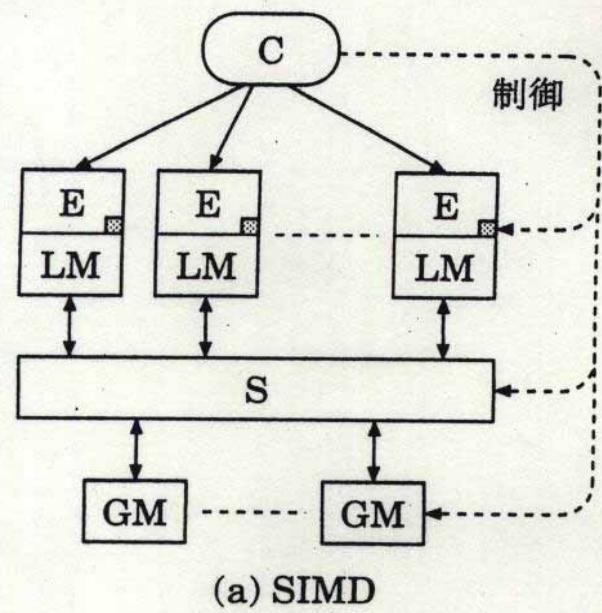

SIMD:Single Instruction

Multiple Data Stream

空間並列型(狭義SIMD)

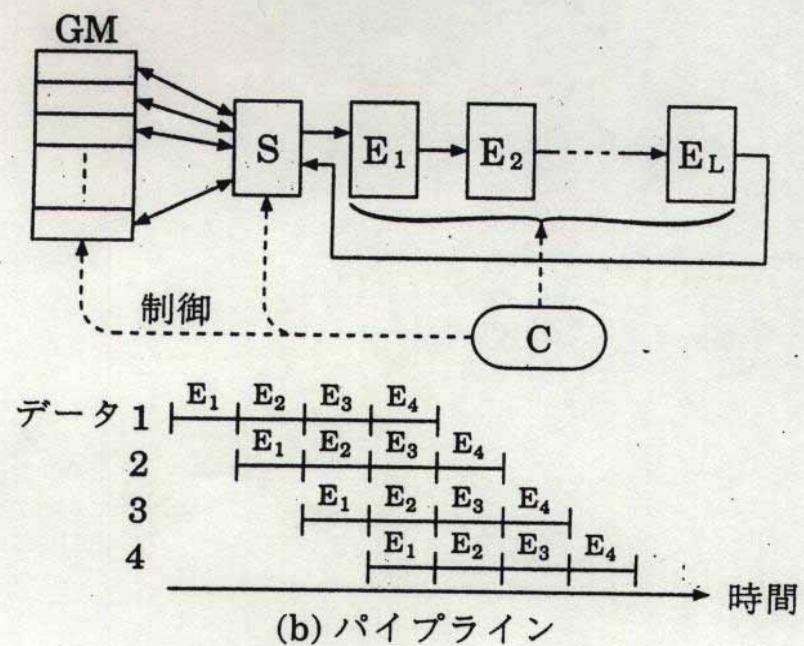

時間並列型(パイプライン)

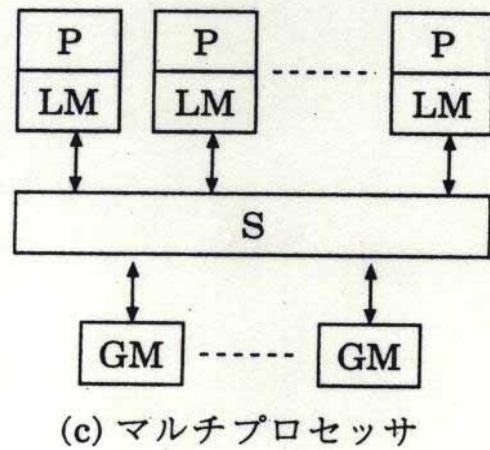

MIMD:Multiple Instruction

Multiple Data Stream

マルチプロセッサ

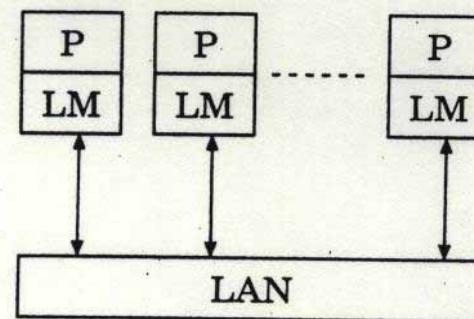

マルチコンピュータ

(a) SIMD

(b) パイプライン

(c) マルチプロセッサ

(d) マルチコンピュータ

(クラスタコンピュータ)

C : 制御装置

E : 演算装置

LM : ローカルメモリ

■ : 抑止フラグ

GM : グローバルメモリ

P : プロセッサ

S : 相互結合網

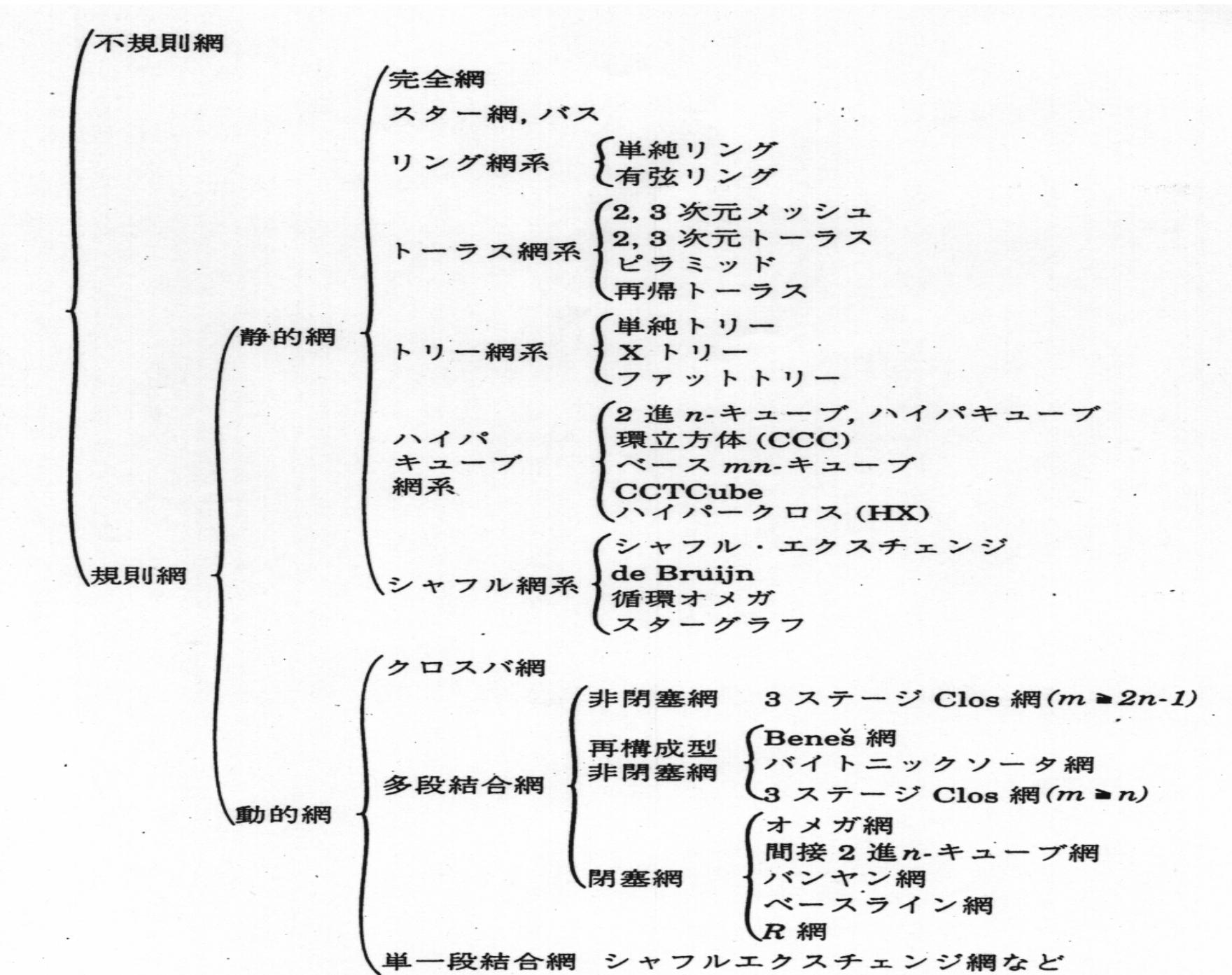

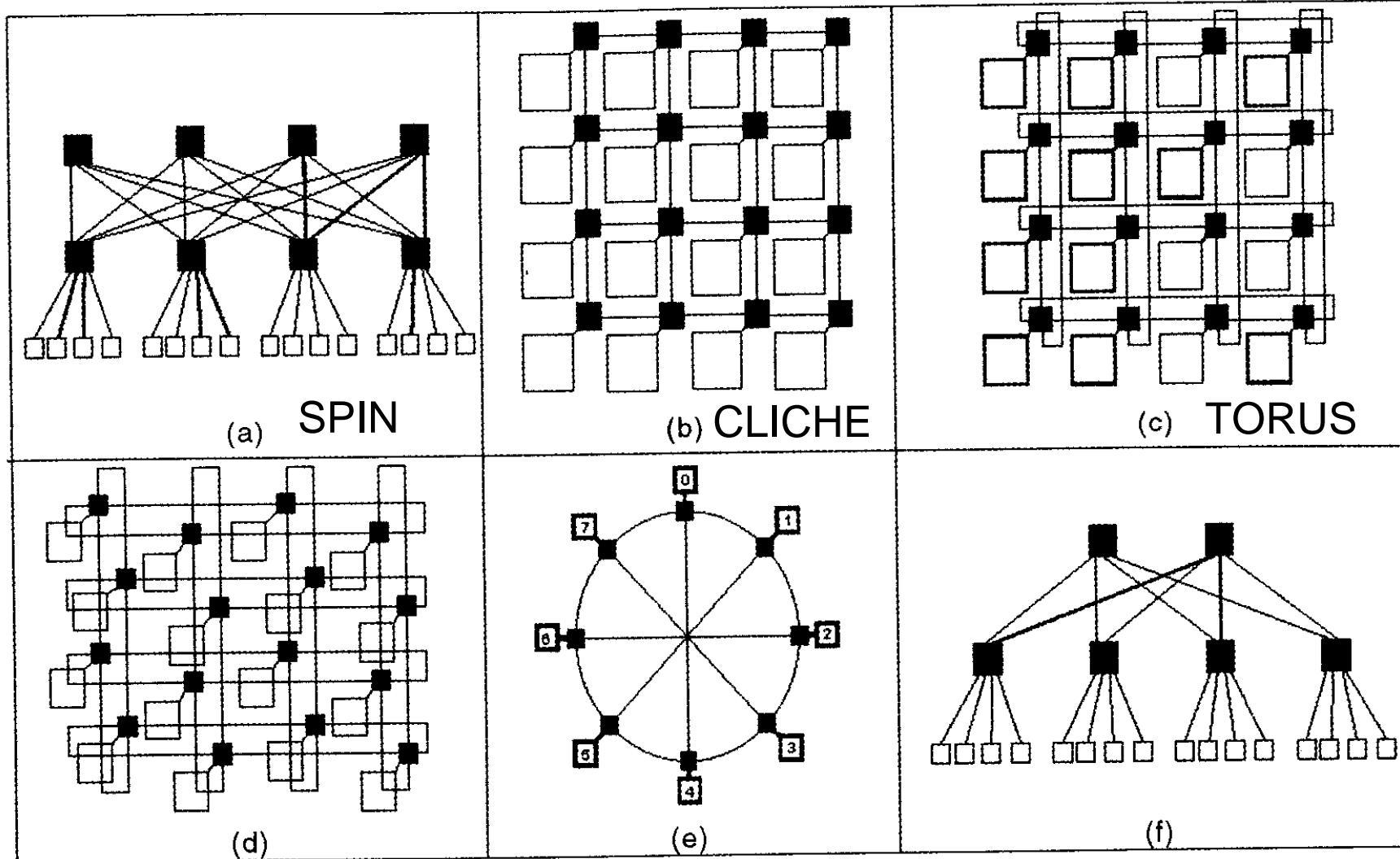

## 7.2 相互結合網

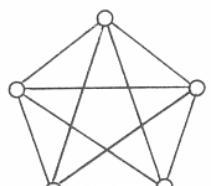

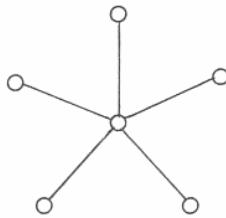

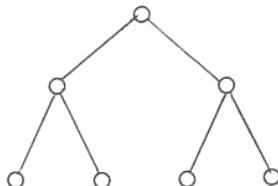

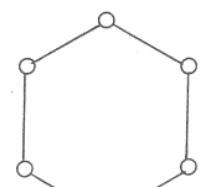

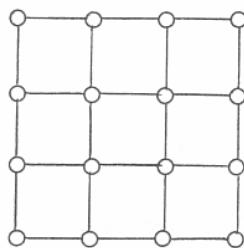

静的網

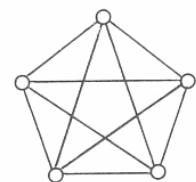

(a) 完全網

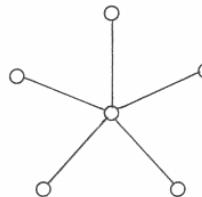

(b) スター網

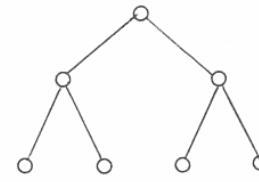

(c) 木状網

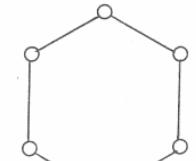

(d) リング網

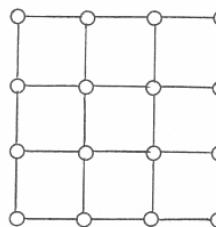

(e) 格子網(トーラス網)

(最上・下, 最左・右を結合)

(f) ハイパーキューブ網

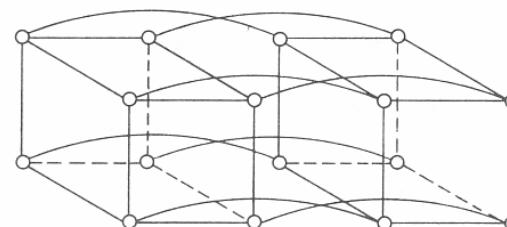

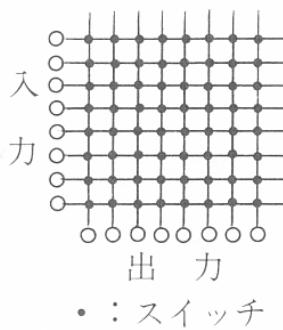

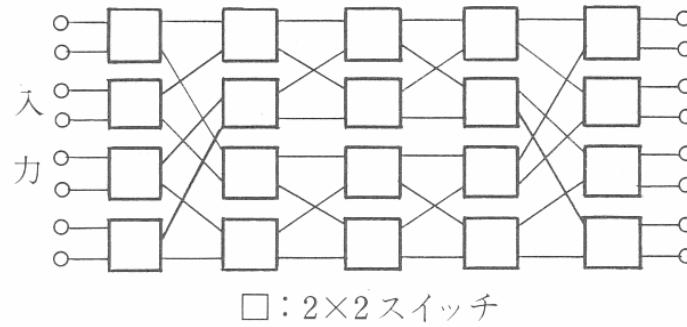

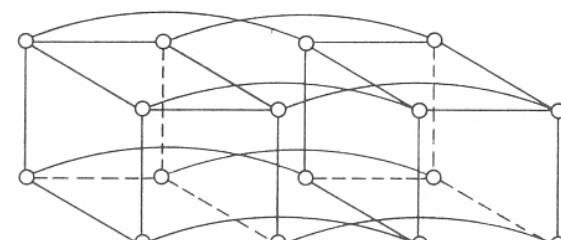

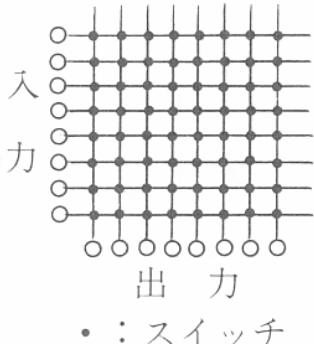

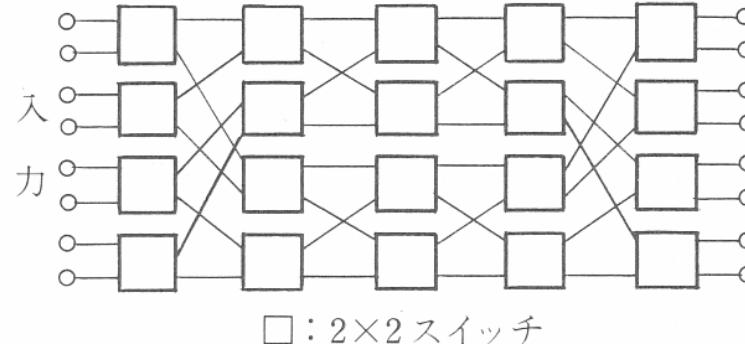

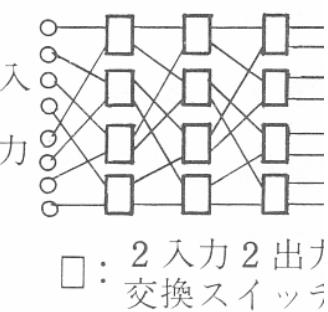

動的網

(a) クロスバー網

(b) Benes網

(c) オメガ網

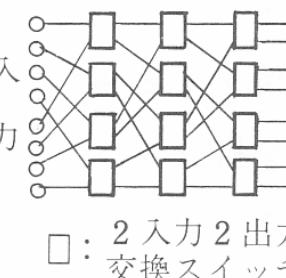

多段結合網

○：演算装置やプロセッサ

## 7.2.1評価項目

- (1) 距離(distance)

- (2) 次数(degree)

- (3) 総スイッチ数 / 総リンク数

- (4) 拡張性(scability)

- (5) 3次元実装の容易性

- (6) 耐故障性(fault tolerance)

- (7) 多様な網の埋込み能力(embedability)

- (8) 容易な経路選択(ルーティング)

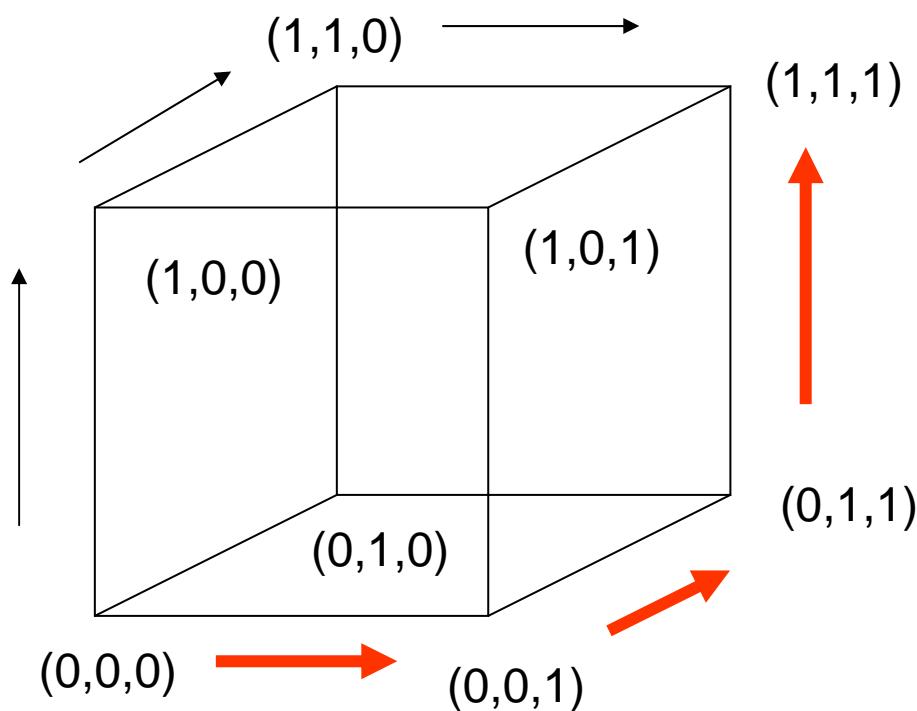

## 7.2.2 静的網 ハイパキューブ

$(a_n, a_{n-1}, \dots, a_2, a_1)$

ハミング距離: 1

$(a_n, a_{n-1}, \dots, a_2, \bar{a}_1)$

$(a_n, a_{n-1}, \dots, \bar{a}_2, a_1)$

⋮

$(0\ 0\ 1) \quad (1\ 1\ 0)$

ハミング距離: 3

$(a_n, \bar{a}_{n-1}, \dots, a_2, a_1)$

$(\bar{a}_n, a_{n-1}, \dots, a_2, a_1)$

ハミング距離: 各桁の比較。異なる桁の数

# ルーティング 下位ビットから宛先に合わせる

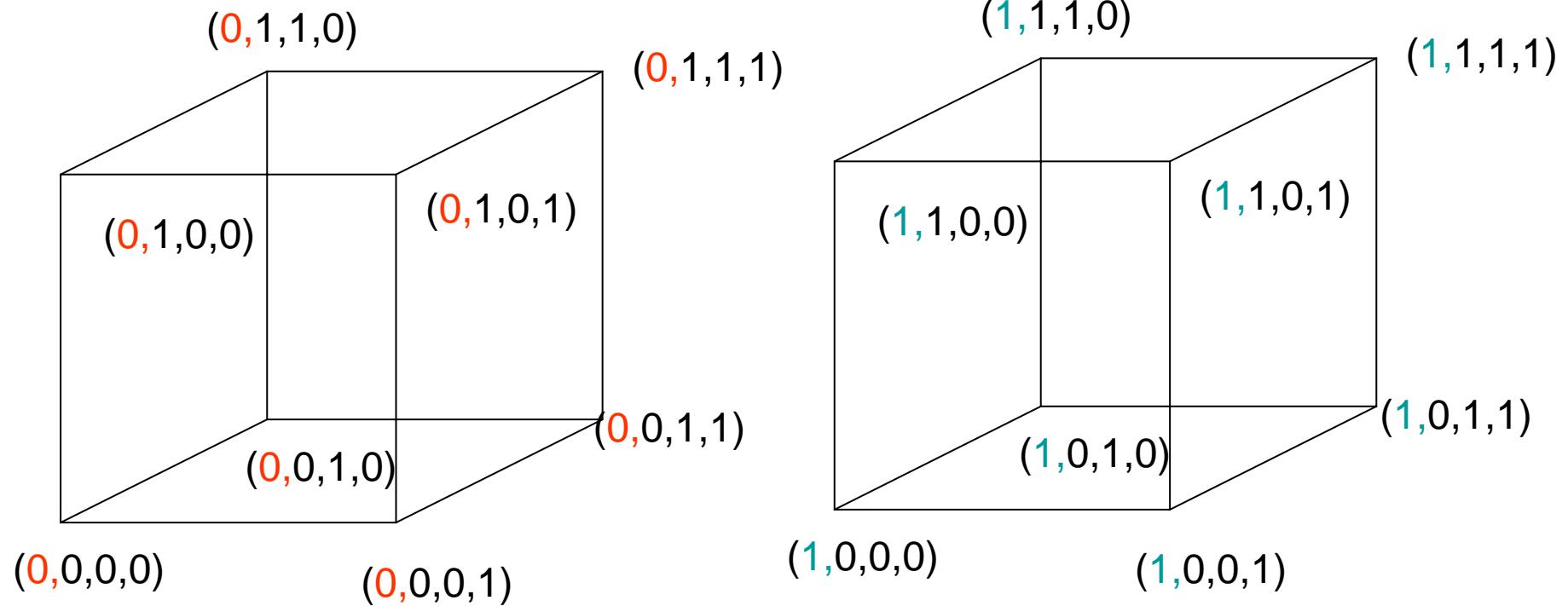

# 拡張性

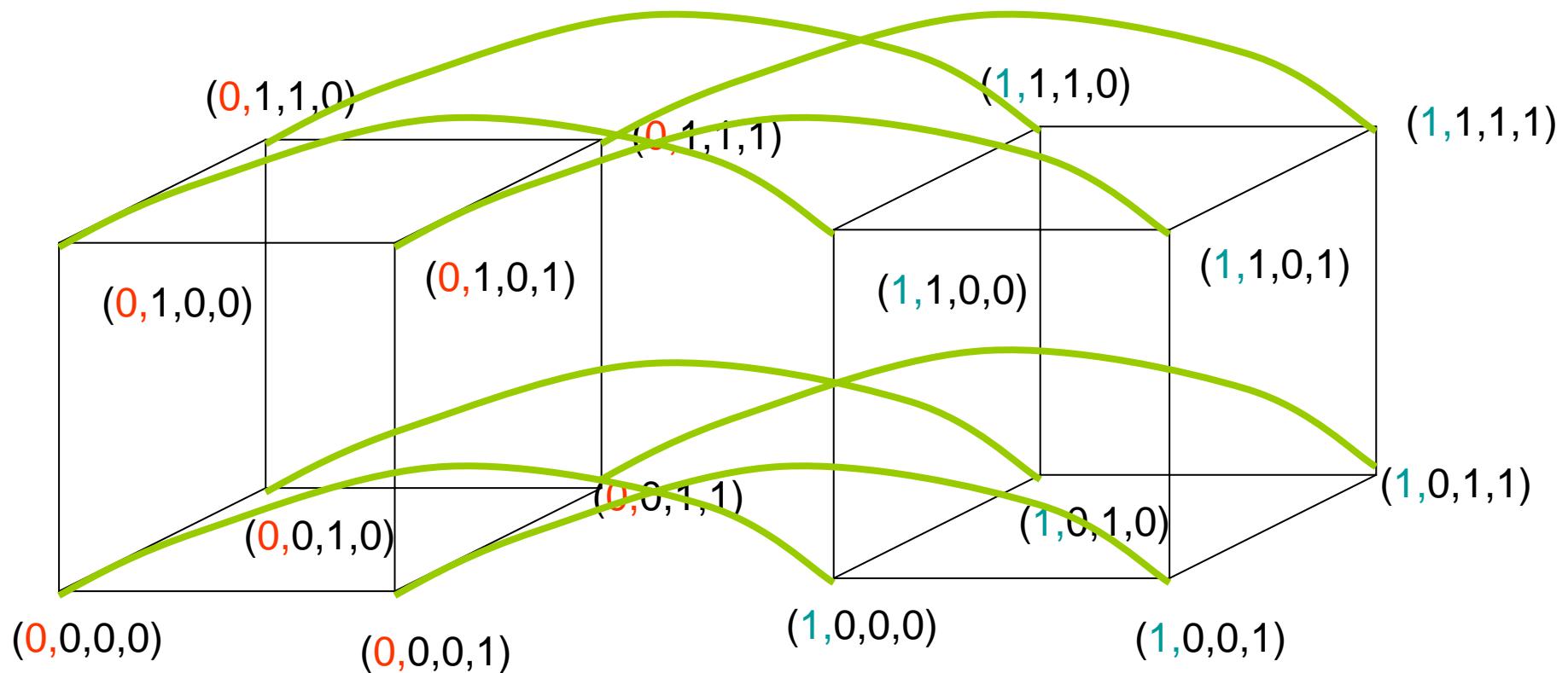

# 拡張 3キューブから4キューブへ

# 埋め込み能力

- リング

1次元の反射2進符号

- トーラス

2次元の反射2進符号

- トリー

1つのダミーノードを許すと可能

# 反射2進符号

## 符号間のハミング距離 = 1

### 通常2進 反射2進

|   |         |   |         |       |

|---|---------|---|---------|-------|

| 1 | { 0 0 0 | 1 | { 0 0 0 | 0 0 0 |

|   | 0 0 1   |   | 0 0 1   | 0 0 1 |

| 2 | { 0 1 0 | 1 | { 0 1 1 | 0 1 1 |

| 1 | 0 1 1   | 1 | { 0 1 0 | 0 1 0 |

| 3 | 1 0 0   | 1 | { 1 1 0 | 1 1 0 |

| 1 | 1 0 1   | 1 | { 1 1 1 | 1 1 1 |

| 2 | { 1 1 0 | 1 | { 1 0 1 | 1 0 1 |

| 1 | 1 1 1   | 1 | { 1 0 0 | 1 0 0 |

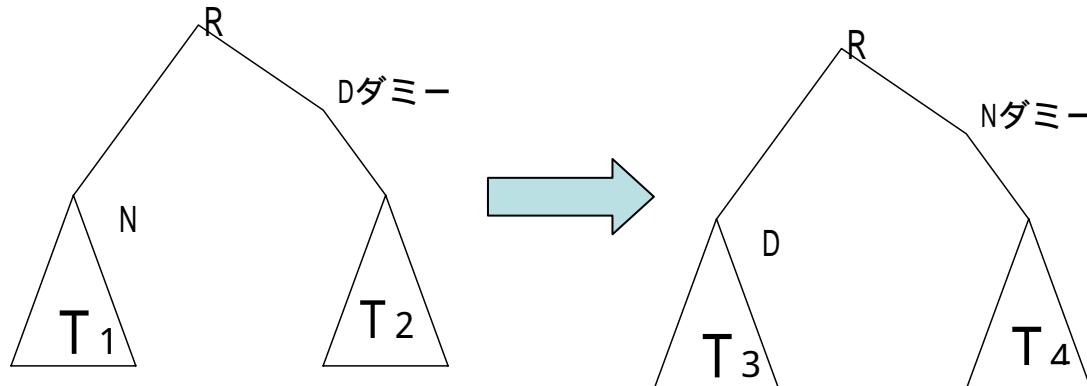

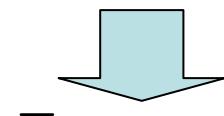

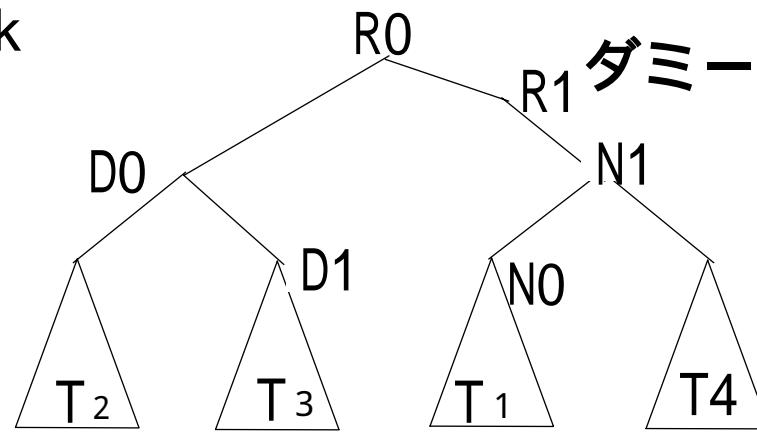

# トリーの埋め込み

証明

$n = k$

$R : (a_n a_{n-1} \dots a_N \dots a_D \dots a_1)$

$D : (a_n a_{n-1} \dots a_N \dots \bar{a}_D \dots a_1)$ で始まるダミー + T2

$N : (a_n a_{n-1} \dots \bar{a}_N \dots a_D \dots a_1)$ で始まるT1

$(a_n a_{n-1} \dots a_N \dots \bar{a}_D \dots a_1)$ で始まるT3

$(a_n a_{n-1} \dots \bar{a}_N \dots a_D \dots a_1)$ で始まるダミー + T4

が存在する。

$R : ( a_n a_{n-1} \dots a_N \dots a_D \dots a_1 )$

$R' : ( a_n a_{n-1} \dots a_D \dots a_N \dots a_1 )$

$R$  と  $R'$  は 1 対 1 対応

$( a_n a_{n-1} \dots \bar{a}_N \dots a_D \dots a_1 ), ( a_n a_{n-1} \dots a_N \dots \bar{a}_D \dots a_1 )$  から始まる

トリーに重なりがなければ

$( a_n a_{n-1} \dots \bar{a}_D \dots a_N \dots a_1 ), ( a_n a_{n-1} \dots a_D \dots \bar{a}_N \dots a_1 )$  から始まる

トリーに重なりがない。

# トリーの埋め込み

証明

$n=k$

$n=k+1$

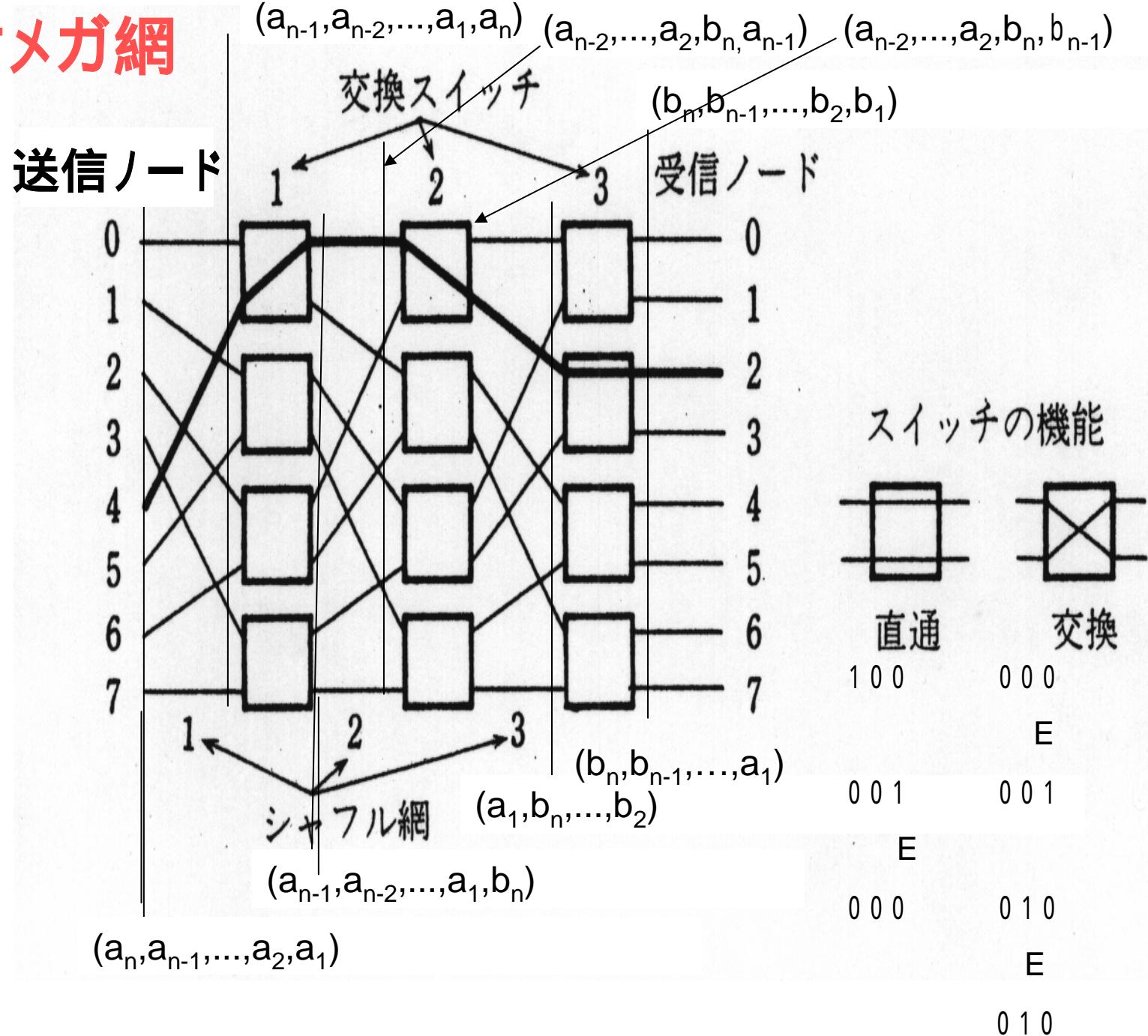

### 7.2.3 動的網

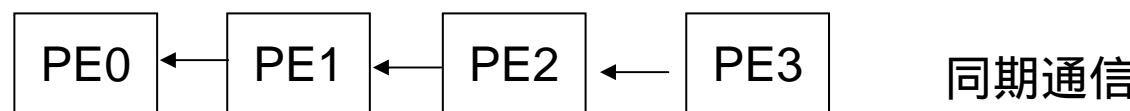

基本通信パターン

送信ノード番号Xの2進表示:( $a_n, \dots, a_2, a_1$ )

受信ノード番号Yの2進表示:( $b_n, \dots, b_2, b_1$ )

通信パターンの数(受信ノードにダブリなし): $N!$

送受信ノードの対応関係:ひとつの置換

送信                      受信

(1, 2, 3, 4) < - > (2, 3, 4, 1)

( a ) エクスチェンジ置換

( b ) シャフル置換

( c ) バタフライ置換と

ビット逆転置換

( d ) シフト置換

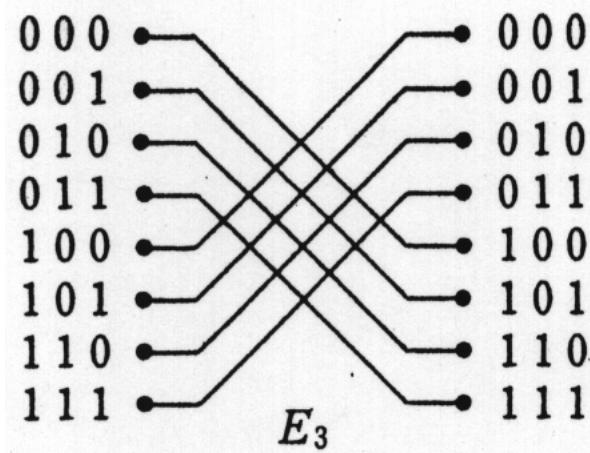

## (1) エクスチェンジ置換

$$y = E_i(x) = (a_n, \dots, \sim a_i, \dots, a_1)$$

$\sim a_i$  は  $a_i$  の否定を表す。

## (2) シャフル置換

$$y = (x) = (a_{n-1}, a_{n-2}, \dots, a_1, a_n)$$

$k$  - サブシャフル  $_k$  ,

$k$  - スーパシャフル  $_k$

$$y = {}_k(x) = (a_n, \dots, a_{k+1}, a_{k-1}, \dots, a_1, a_k)$$

$$y = {}^k(x) = (a_{n-1}, \dots, a_{n-k+1}, a_n, a_{n-k}, \dots, a_1)$$

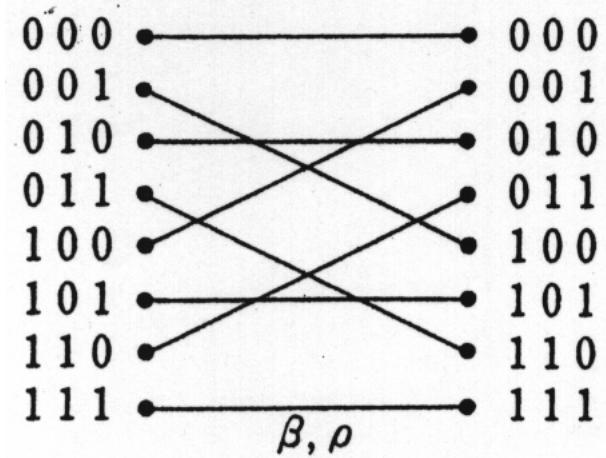

## (3) バタフライ置換

$$y = (x) = (a_1, a_{n-1}, \dots, a_2, a_n)$$

$k$  - サブバタフライ

$k$  - スーパバタフライ  $_k$   $_k$

$$y = {}_k(x) = (a_n, \dots, a_{k+1}, a_1, a_{k-1}, \dots, a_2, a_k)$$

$$y = {}^k(x) = (a_{n-k+1}, a_{n-1}, \dots, a_{n-k+2}, a_n, a_{n-k}, \dots, a_1)^{17}$$

#### (4) ビット逆転置換

$$y = \pi(x) = (a_1, a_2, \dots, a_n)$$

k - サブビット逆転置換

k - スーパビット逆転置換

$$y = \pi_k(x) = (a_n, \dots, a_{k+1}, a_1, a_2, \dots, a_{k-1}, a_k)$$

$$y = \pi^k(x) = (a_{n-k+1}, a_{n-k+2}, \dots, a_{n-1}, a_n, a_{n-k}, \dots, a_1)$$

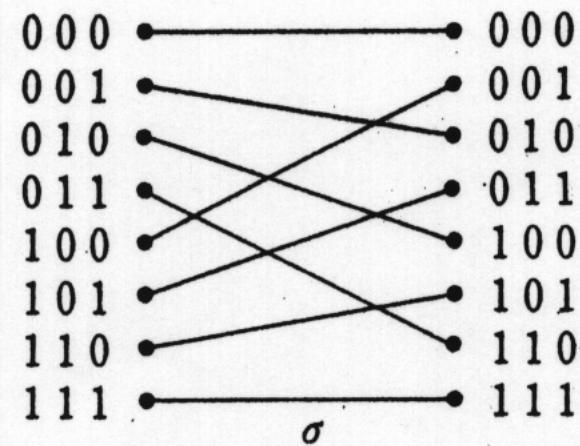

#### (5) シフト置換

$$y = \sigma(x) = X + 1 \mod N$$

### 動的網の分類

完全非閉塞網

再構成型非閉塞網

閉塞網

# オメガ網

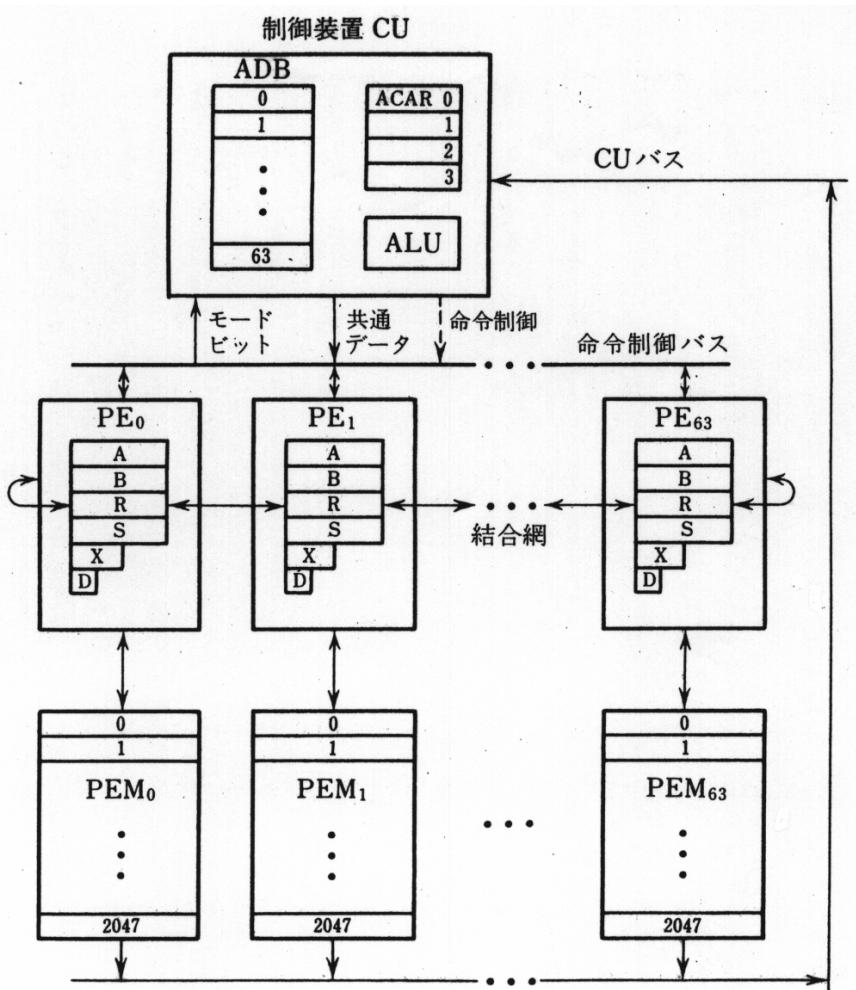

## 7.3 SIMD方式

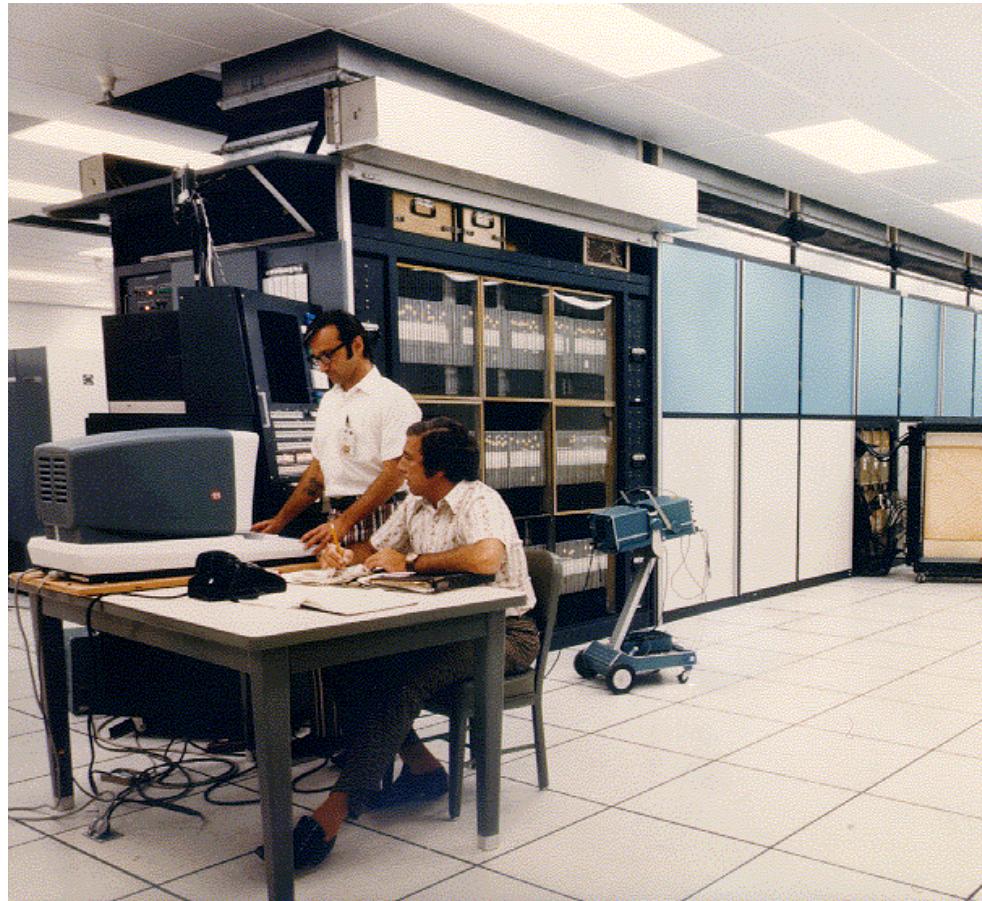

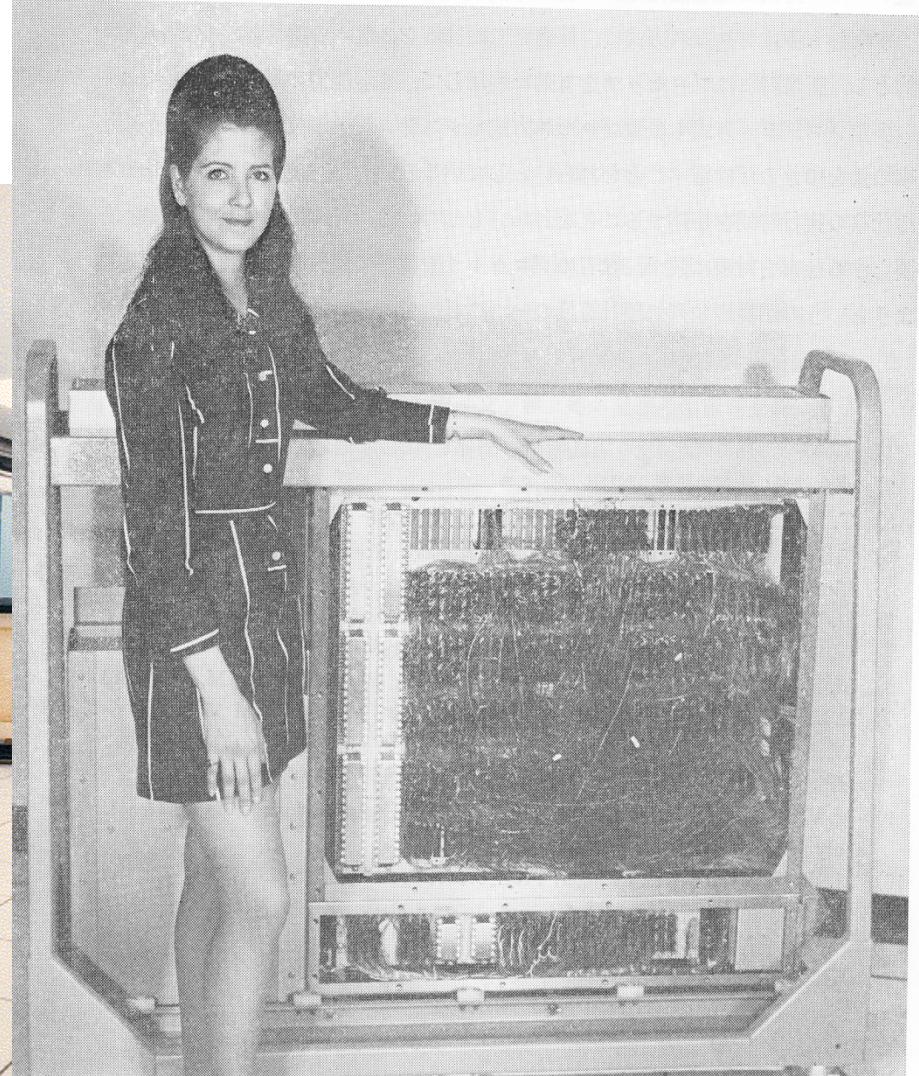

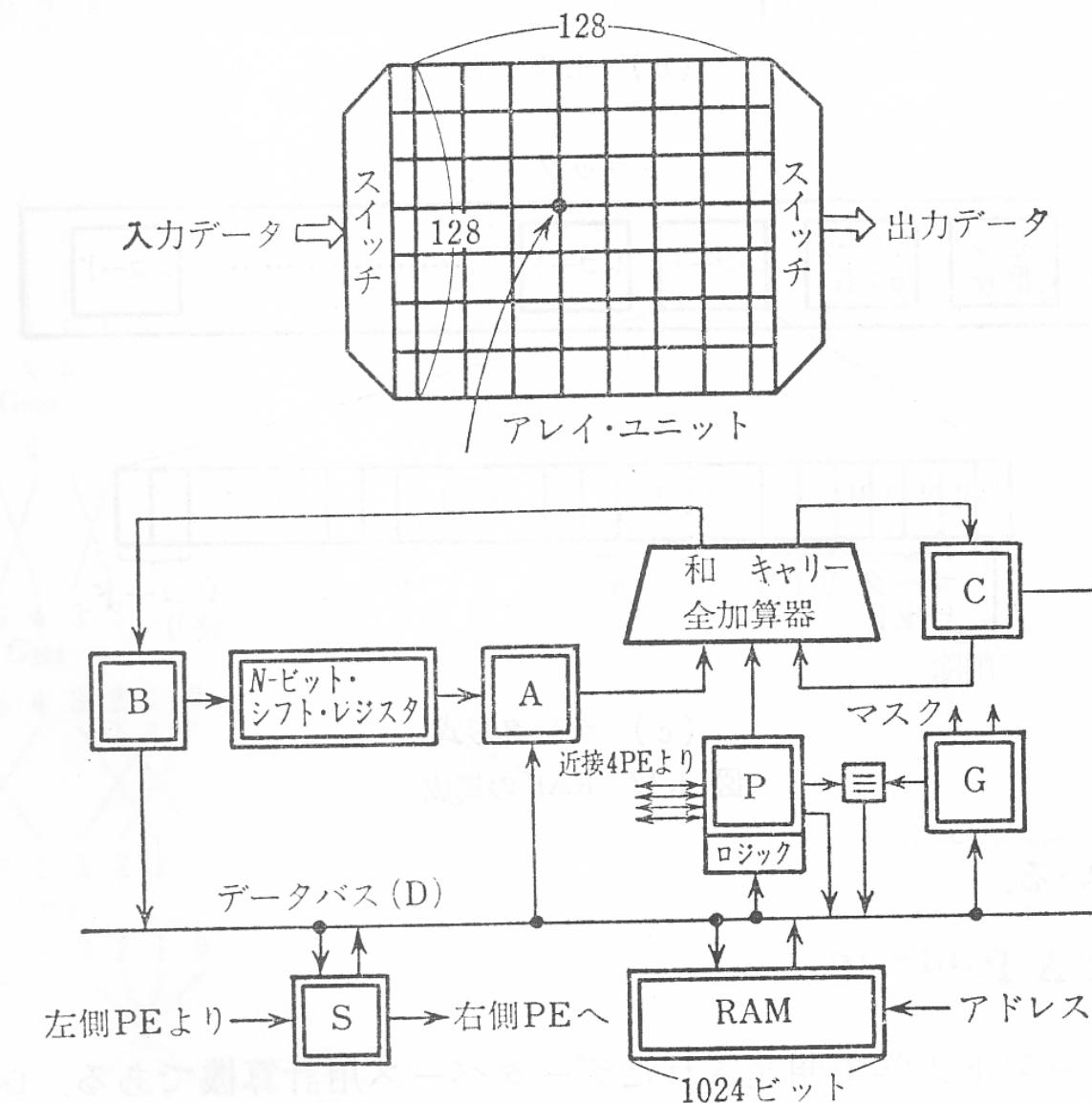

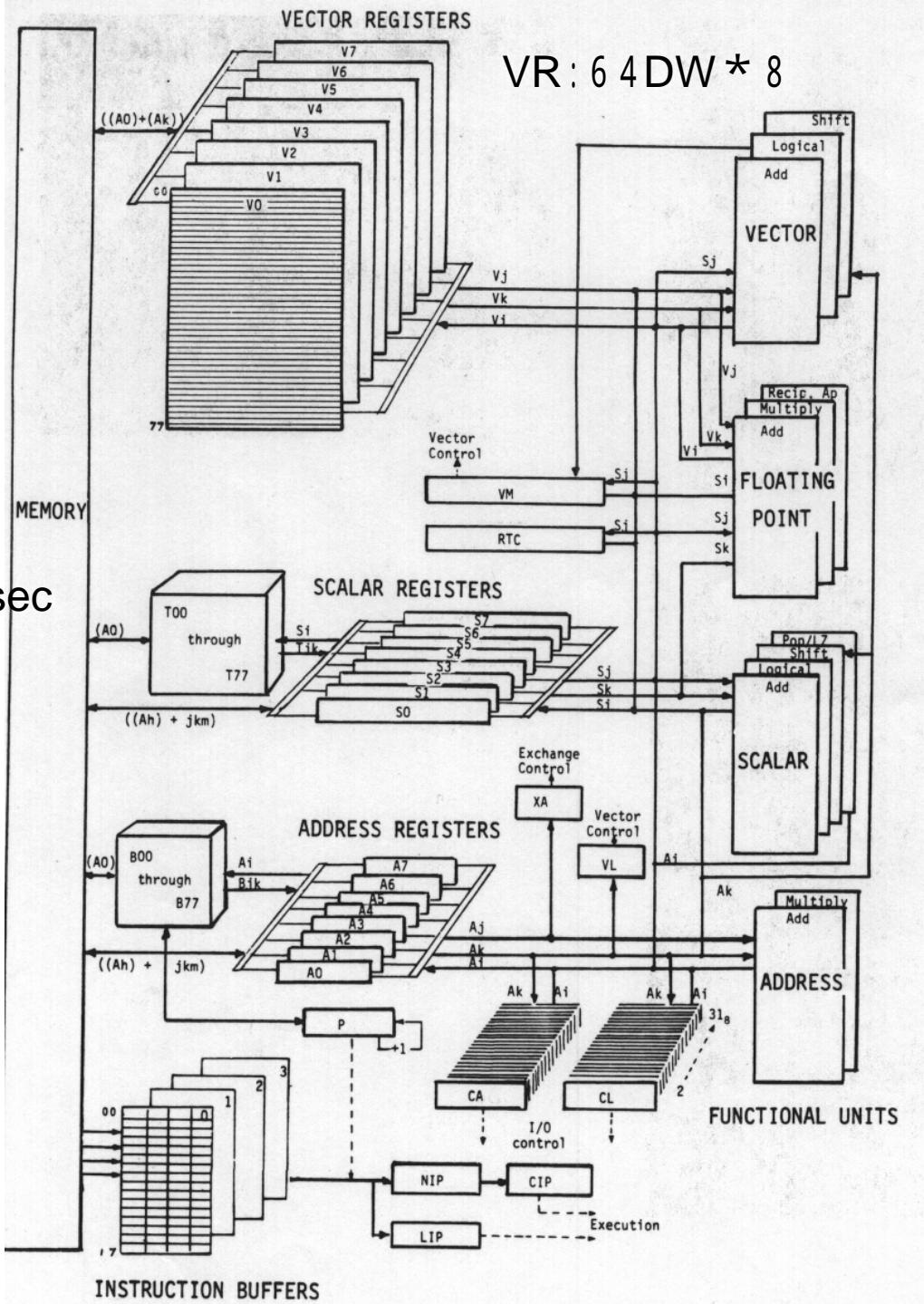

パイオニア:ILLIAC IV

1974 マシンサイクル

80nsec 50MFLOPS

ILLIAC IV

処理装置

アレイ内の 64 個の処理装置はすべて同じ機能をもち、同一の構成になっている。処理装置は、演算装置・記憶装置・メモリロジックユニットなどからなり、高さ 41.5 インチ、長さ 54 インチ、幅 7 インチ、重さ約 200 ポンドである。故障が生じたときは、アレイから処理装置をはずして運搬するための台車が用意されている。(p. 94, 114 参照)

加藤、苗村:並列処理計算機、オーム社、

1976

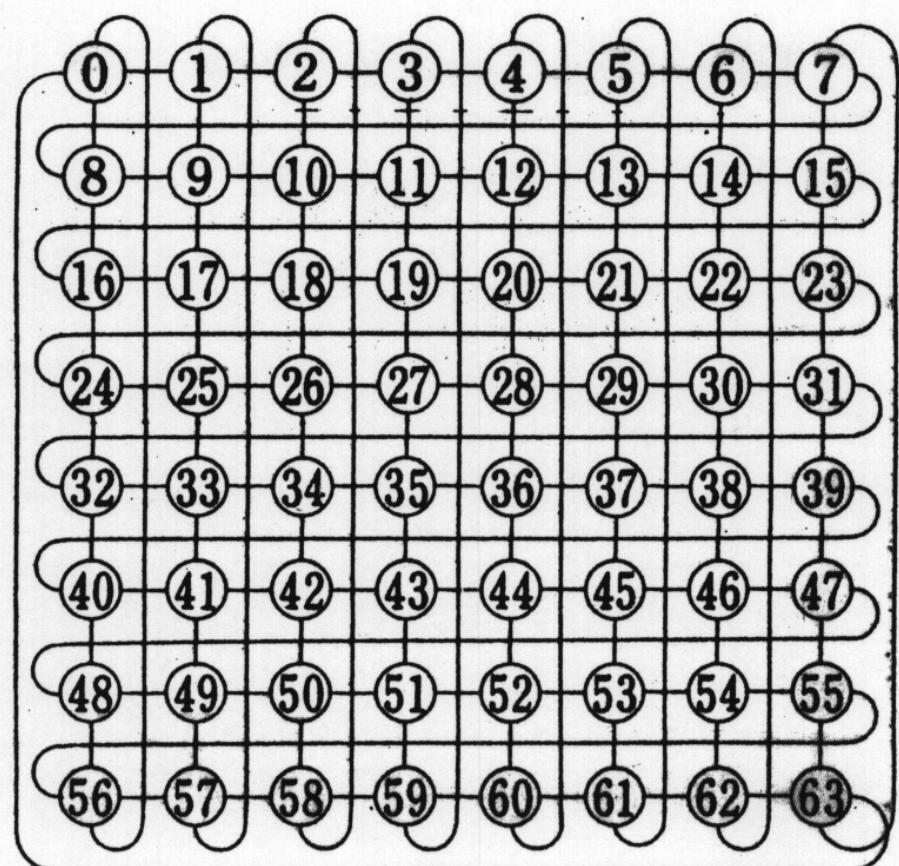

疑似トーラス網

### 7.3.1 SIMD基本方式

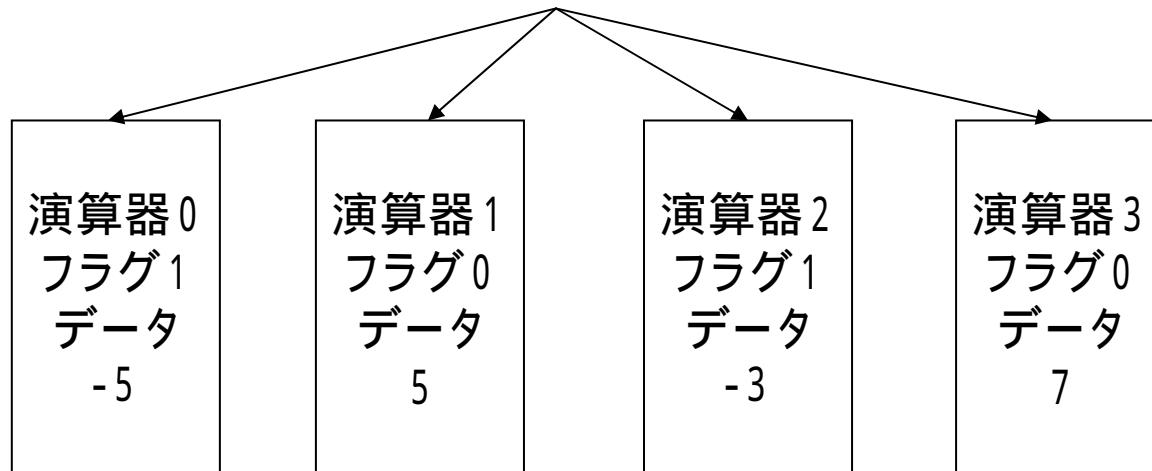

#### SIMD演算の例: 絶対値の計算

正のデータを持っているもの 抑止フラグ0

負のデータを持っているもの 抑止フラグ1

0-(データ)の一斉実行

引き算せよ

5

5

3

7

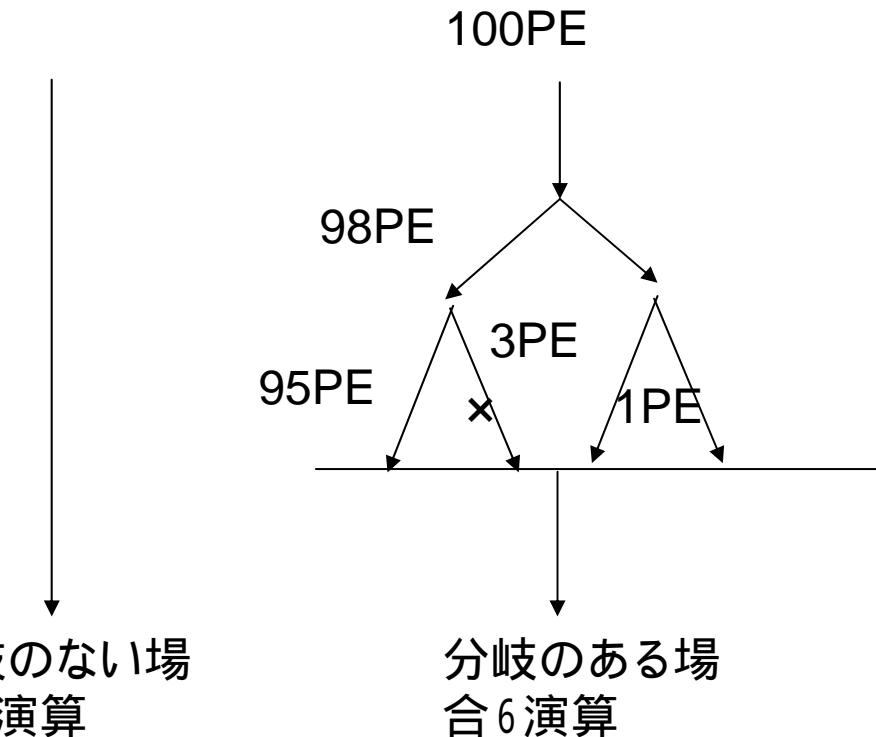

## SIMD方式の特徴

演算装置の簡略化

細粒度並列処理指向

定型処理指向

分岐少ない方がよい

命令同期型プログラミング

全PE終了後次命令発行

プログラミングの制約

標準的なプログラミング

生産性が向上？

コンパイラによる最適化

全PEが同時終了するよう、無資源競合

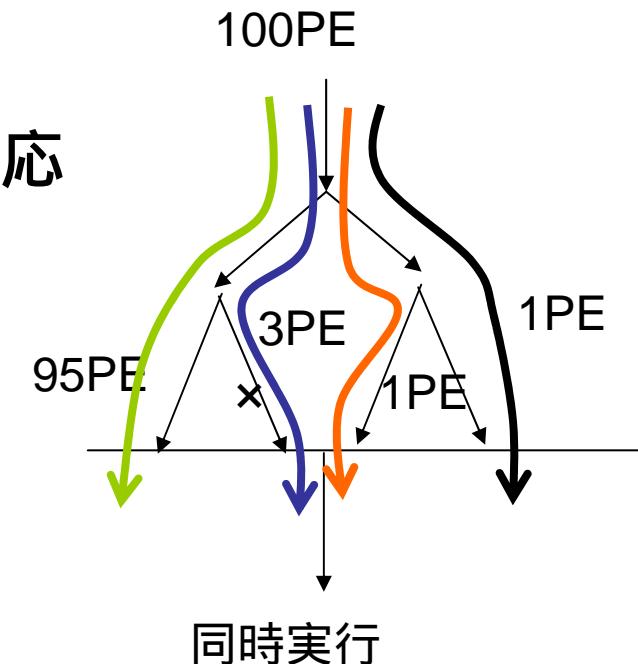

## SIMDの泣き所

非定型処理に弱い

一番遅い演算器で律速

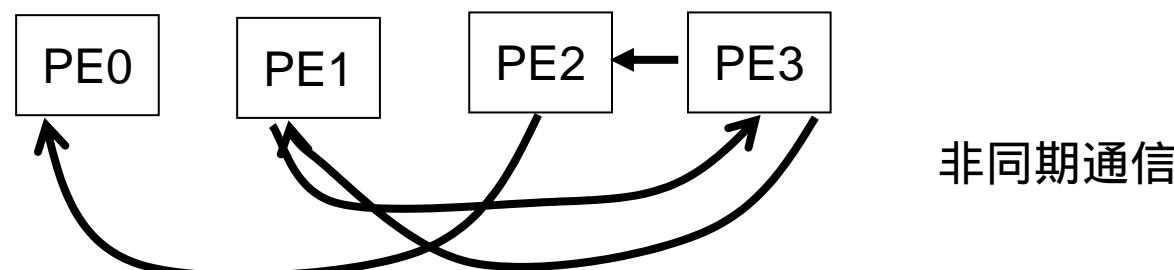

### 7.3.2 SIMDの柔構造化と非定型処理への対応

#### 通信の非同期化

SPMD化:Single Program Multiple Data

分岐点から合流点までをPEで非同期実行

MIMD化:マルチプロセッサ化！！

SIMDは歴史的な役割を終えたのか？

# MPP

図 4.18 MPP の構成(K. E.Batcher: Design of a Massively Parallel Processor,

IEEE Trans. C. Vol. 29, No. 9, 1980, pp. 836-840 による)

# フィルタ処理：輪郭線抽出など

## ラプラシアンオペレータ

$$\begin{aligned}\nabla^2 \varphi &= \partial^2 \varphi / \partial x^2 + \partial^2 \varphi / \partial y^2 \\&= \varphi(I+1, J) - \varphi(I, J) - \\&\quad (\varphi(I, J) - \varphi(I-1, J)) + \\&\quad \varphi(I, J+1) - \varphi(I, J) - \\&\quad (\varphi(I, J) - \varphi(I, J-1)) \\&= \varphi(I+1, J) + \varphi(I-1, J) \\&\quad + \varphi(I, J+1) + \varphi(I, J-1) \\&\quad - 4\varphi(I, J)\end{aligned}$$

|   |     |   |

|---|-----|---|

|   | 1   |   |

| 1 | - 4 | 1 |

|   | 1   |   |

Y, J

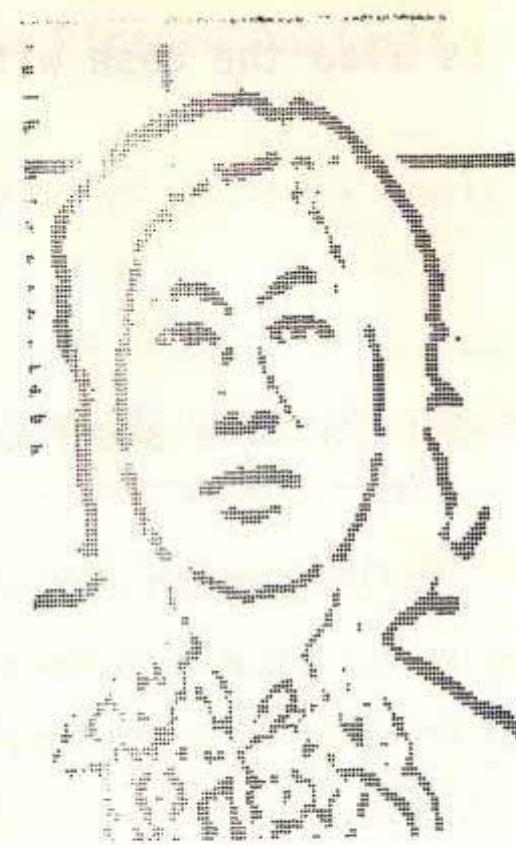

(a) Original photograph

(b) Printout of the digital gray-level picture

(c) Binary picture

Figure 3-2

Picture input and line extraction.

The dark horizontal line in the upper part is due to the burn in the CRT surface of the FSS used for digitization.

金出武雄博士論文

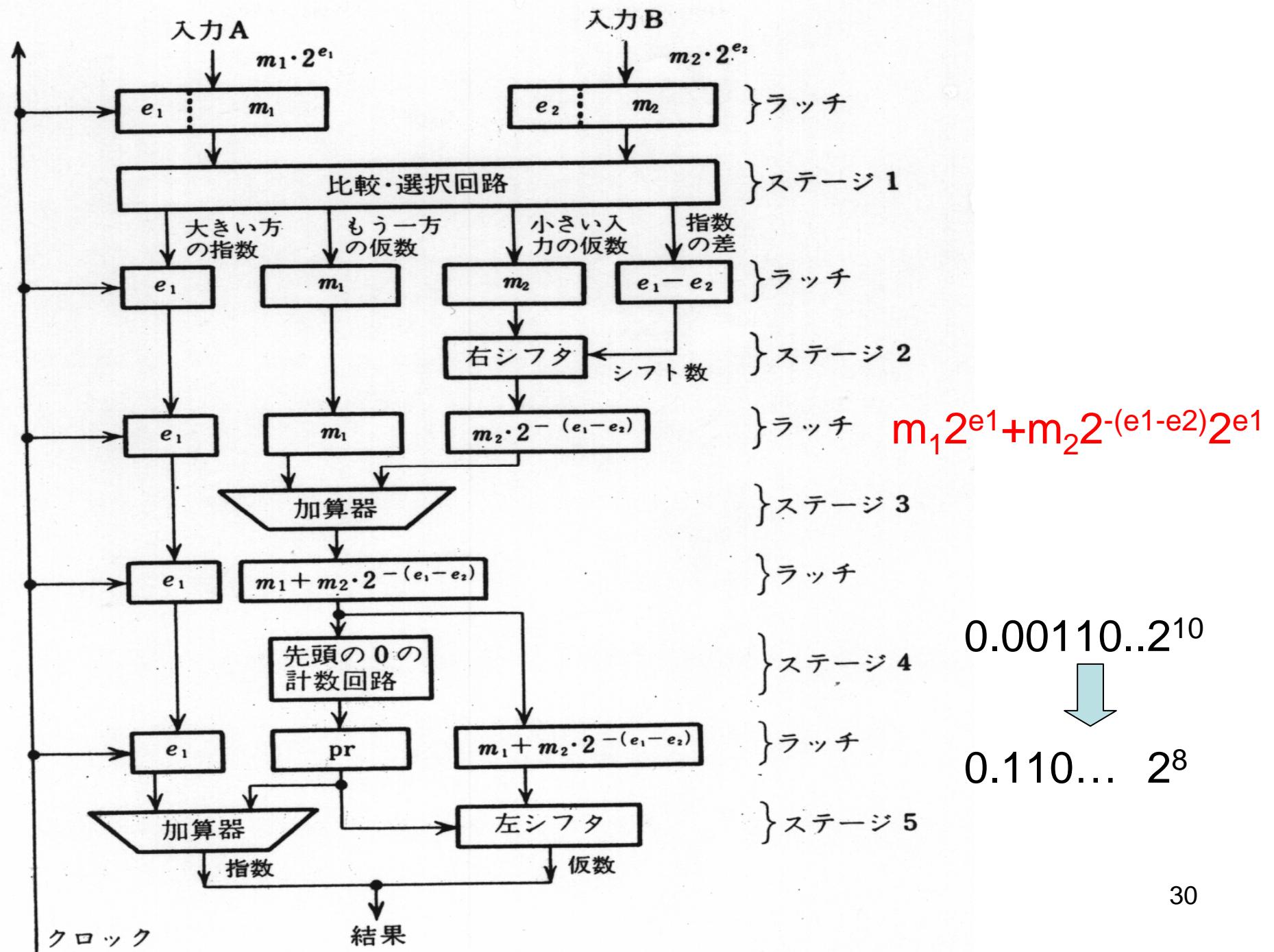

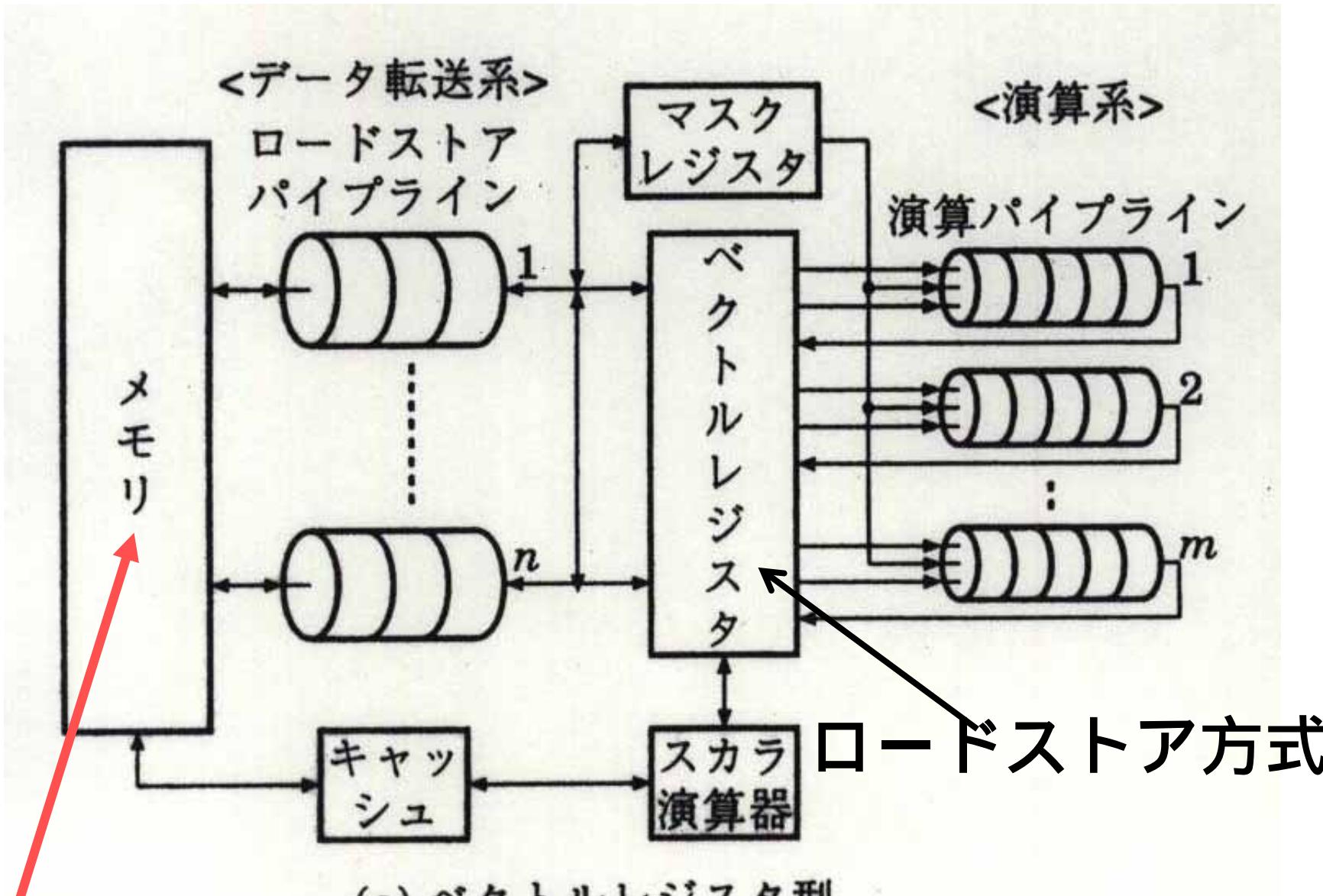

## 7.4パイプライン型スーパコンピュータ

### 7.4.1基本方式

- ・別名:ベクトルプロセッサ(コンピュータ)

- ・ベクトルデータの高速処理

$$Z(I) = X(I) + Y(I)$$

$$T = X(I) * Y(I) : \text{内積}$$

$$T = \text{MAX}(X(I)), \text{MIN}(X(I))$$

$$X(I+1) = A(I) * X(I) + B(I) : \text{漸化式}$$

- ・線形代数:行列、ベクトル

$$AX, AB, A^T, A^{-1}$$

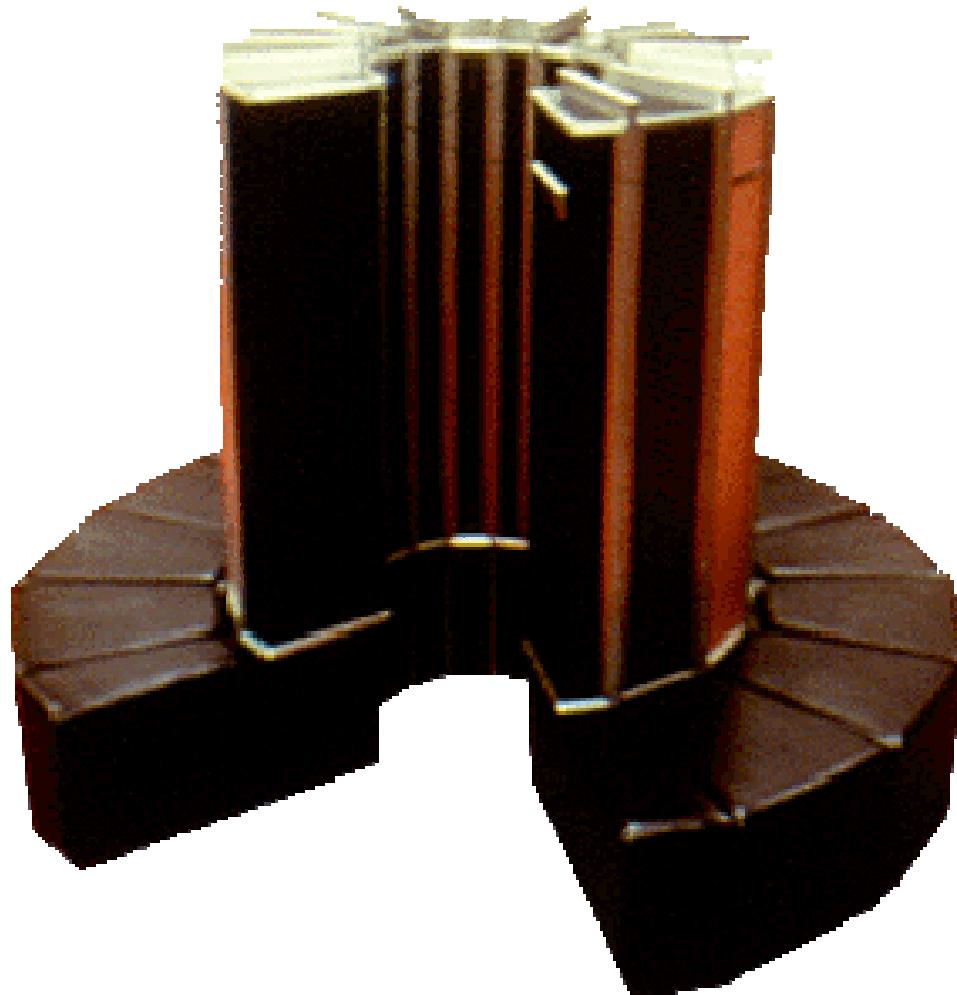

パイオニア:Cray-1 1976、マシンサイクル12.5

nsec、160MFLOPS

The World's Most Expensive Love-seat

CACM Vol21, No.1, 1978, pp. 63 - 72

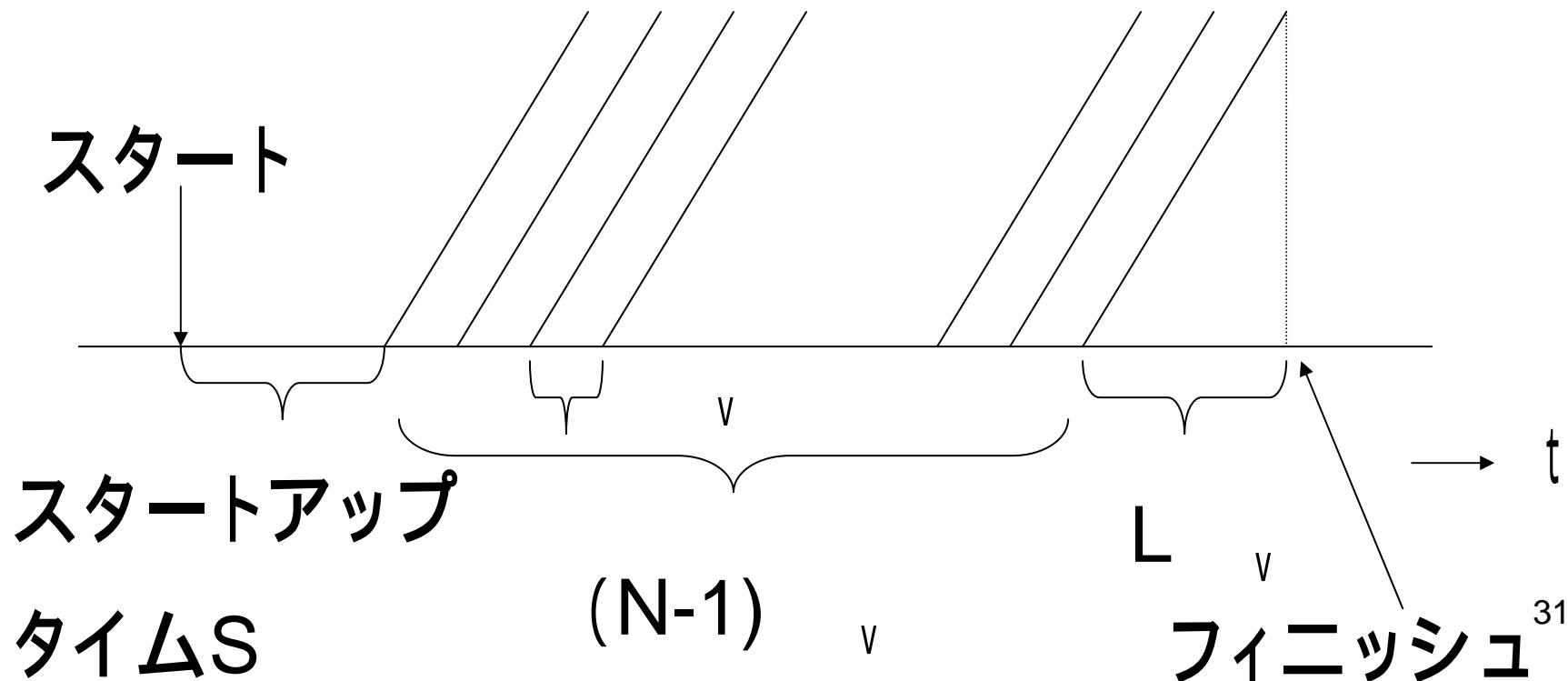

# 半性能長:最大性能( $1/v$ )の半分の性能となるデータ要素数 演算時間

$$T = S + \frac{(N-1+L)}{v}$$

$$= \frac{(N+N_{1/2})}{v}$$

$$\frac{1}{(2v)} = \frac{N_{1/2}}{(S + \frac{(N_{1/2}-1+L)}{v})}$$

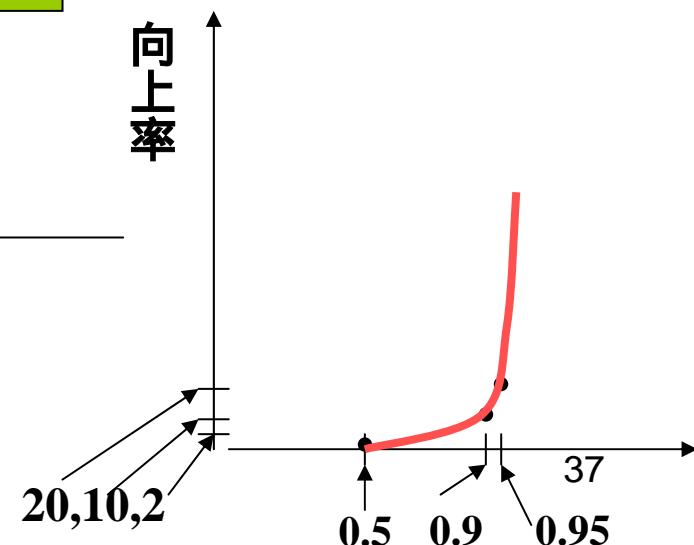

10GFLOPSのために1000台の100nsecメモリ

## ベクトル処理の高速化

$$Z(I) = X(I)^* Y(I)$$

SET Vector Length

LOADV VR0 M(R2+D1)

LOADV VR1 M(R2+D2)

MULFV VR2 VR1 VR0

STOREV M(R2+D3) VR2

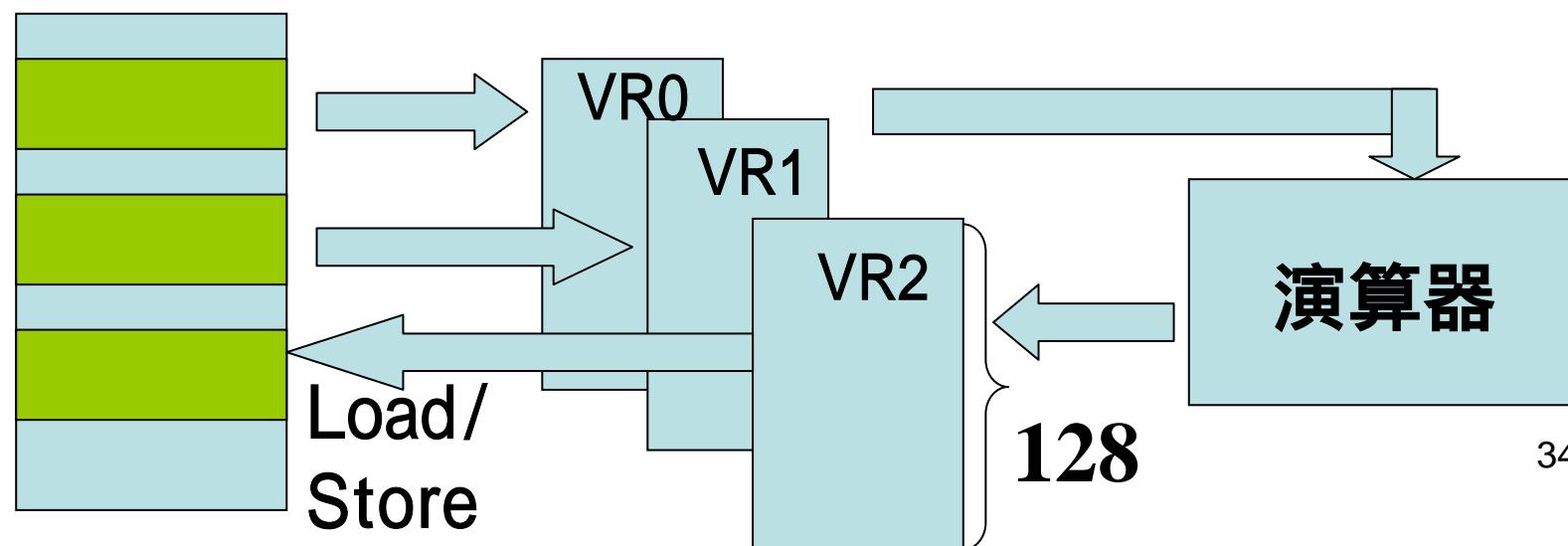

# ベクトル処理の高速化

$$Z(I) = X(I)^* Y(I)$$

SET Vector Length 128

LOADV VR0 M(1000)

LOADV VR1 M(2000)

MULFV VR2 VR1 VR0

STOREV M(3000) VR2

メモリ

1000

2000

3000

メモリ

8MB

16バンク

1DW/12.5nsec

1976年

12.5nsec

160 MFLOPS

115 KW

ECLロジック

## ベクトルプロセッサの普及理由

高速性: 通常の計算機より1桁以上高速

連續性: 過去に作成されたFORTRANプログラムがそのまま利用

単純性: ベクトル演算で問題が定式化できれば

最大性能、ベクトル: 高等学校数学

汎用性: 多様な数値計算分野に適応

单一性: 各社ハードウェアシステムの構造が同一

「よい」プログラムはどのスーパコンピュータでも高速実行

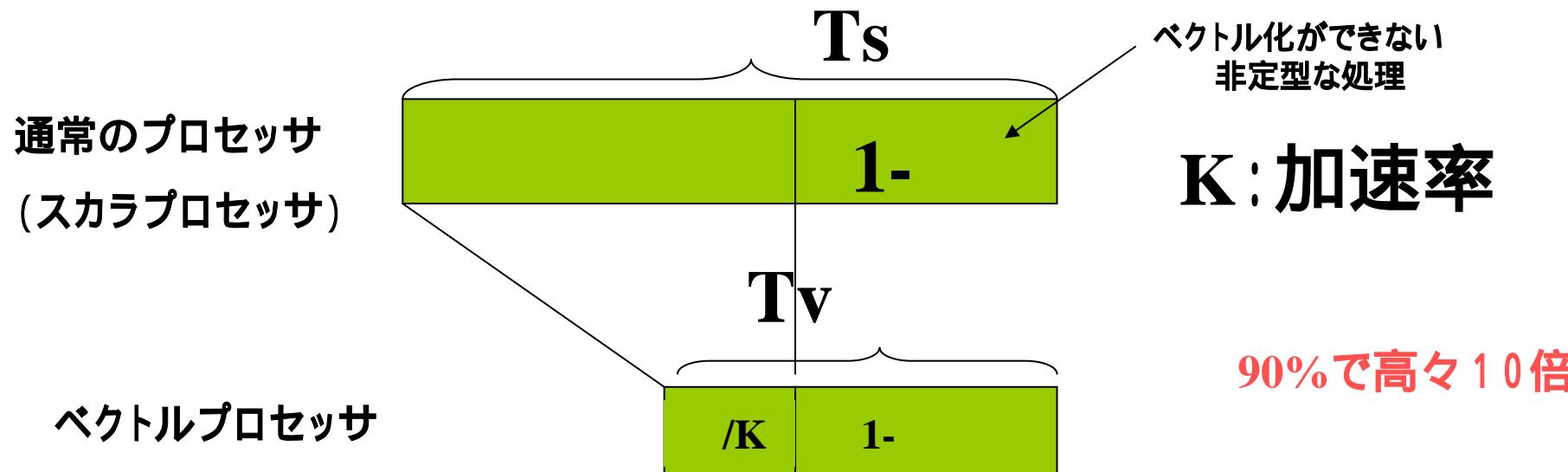

## 7.4.2 ベクトルプロセッサの泣き所：アムダールの法則

ベクトル化率( )が高くないとダメ

性能向上率

$$T_s/T_v = \frac{1}{1- + /K}$$

通常のプロセッサも高速

の必要：二重苦

90%で高々10倍

# ベクトルプロセッサの泣き所 : メモリバンド幅

- ・1024バンク構成

- ・スカラユニット + ベクトルユニットの開発

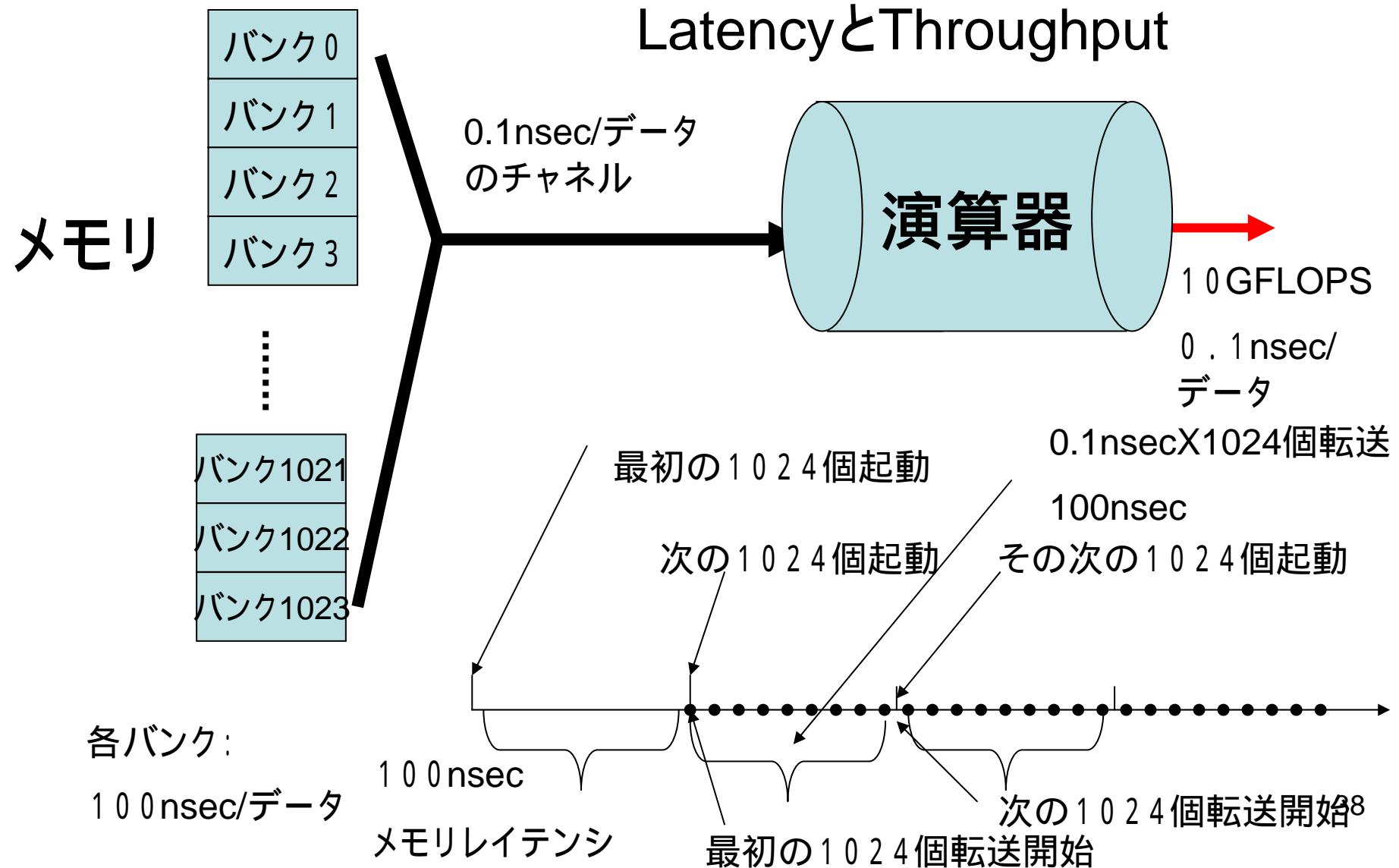

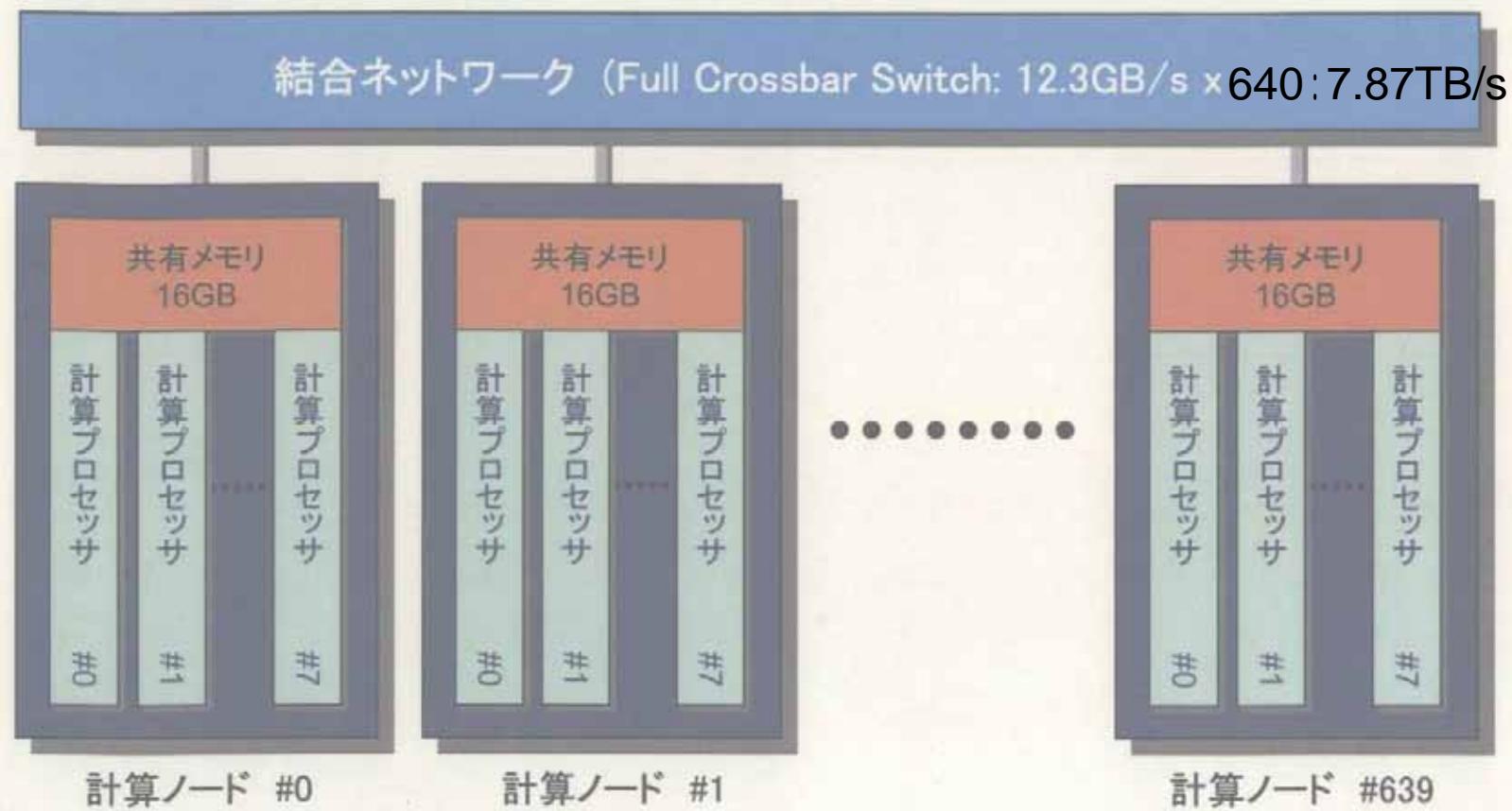

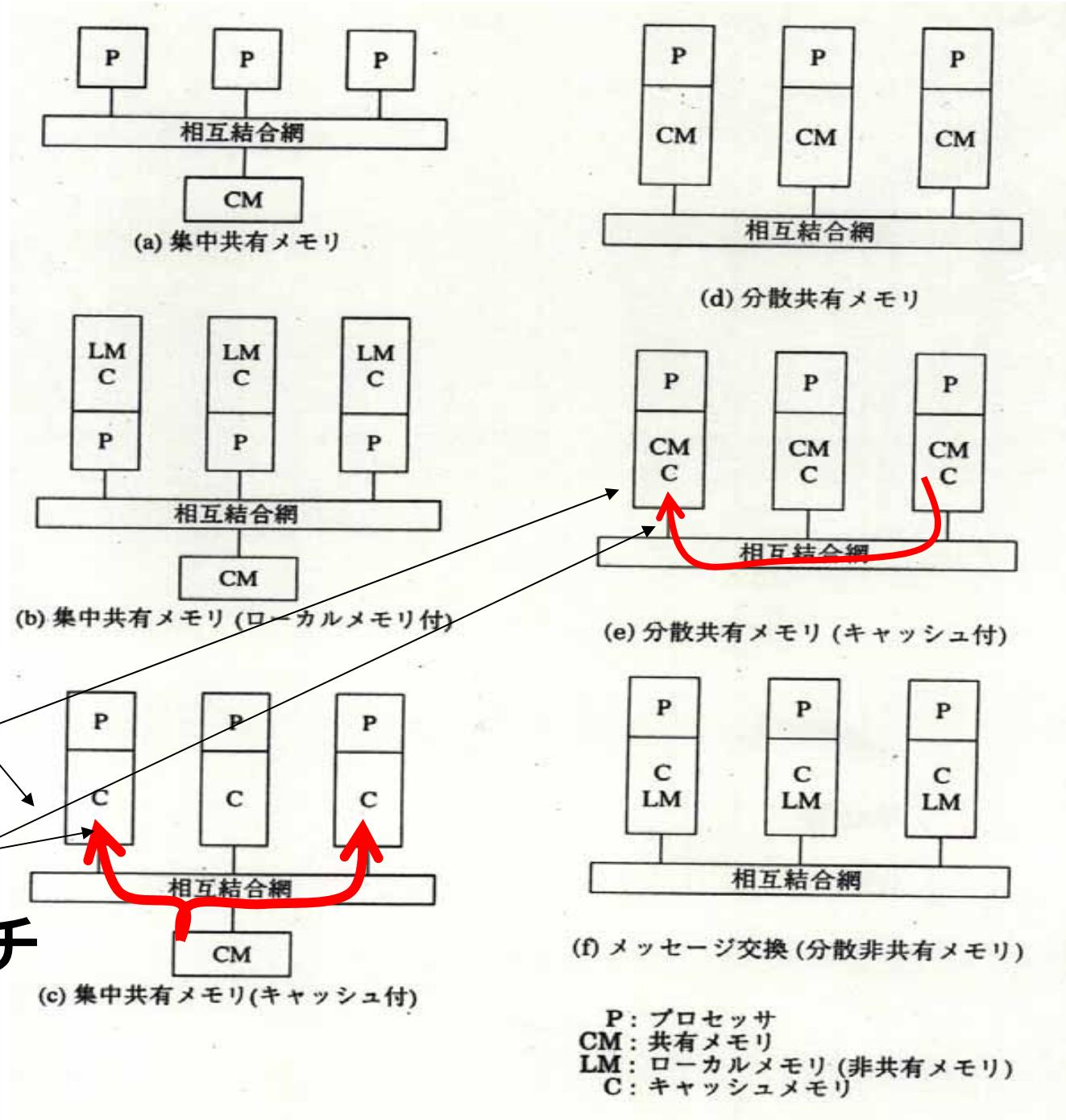

## 7.5マルチプロセッサとマルチコンピュータ

### 7.5.1マルチプロセッサの基本方式

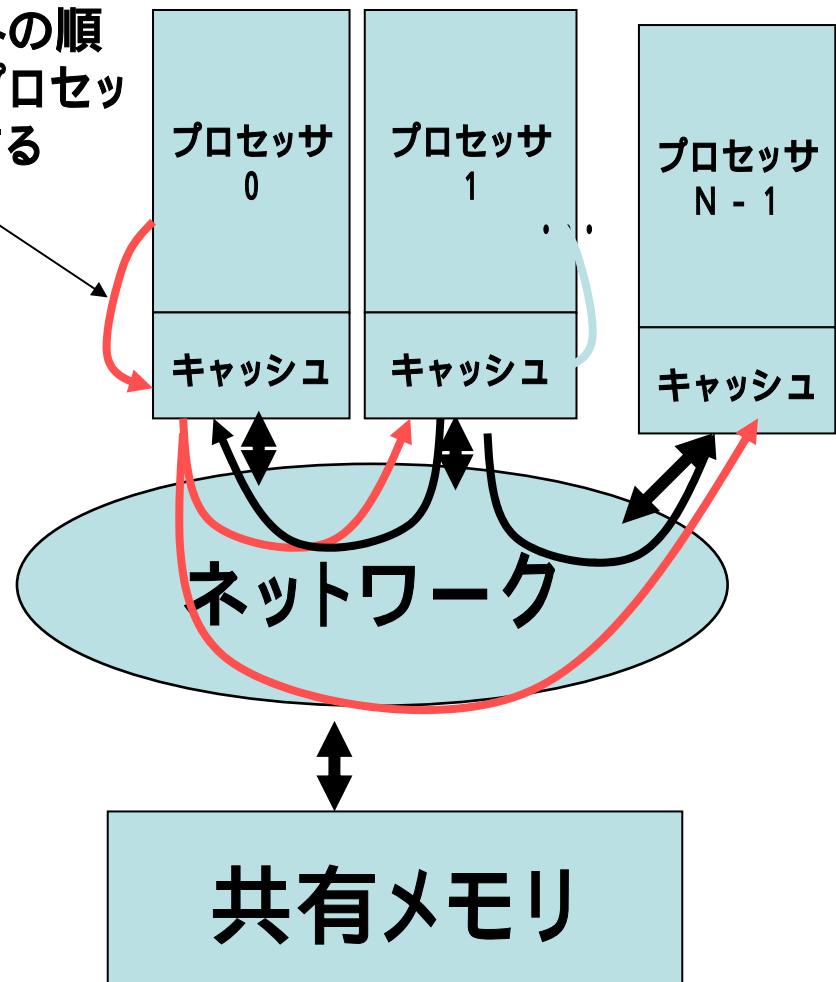

(1)メモリ共有型 VS メッセージ交換型

最大性能のシステム：

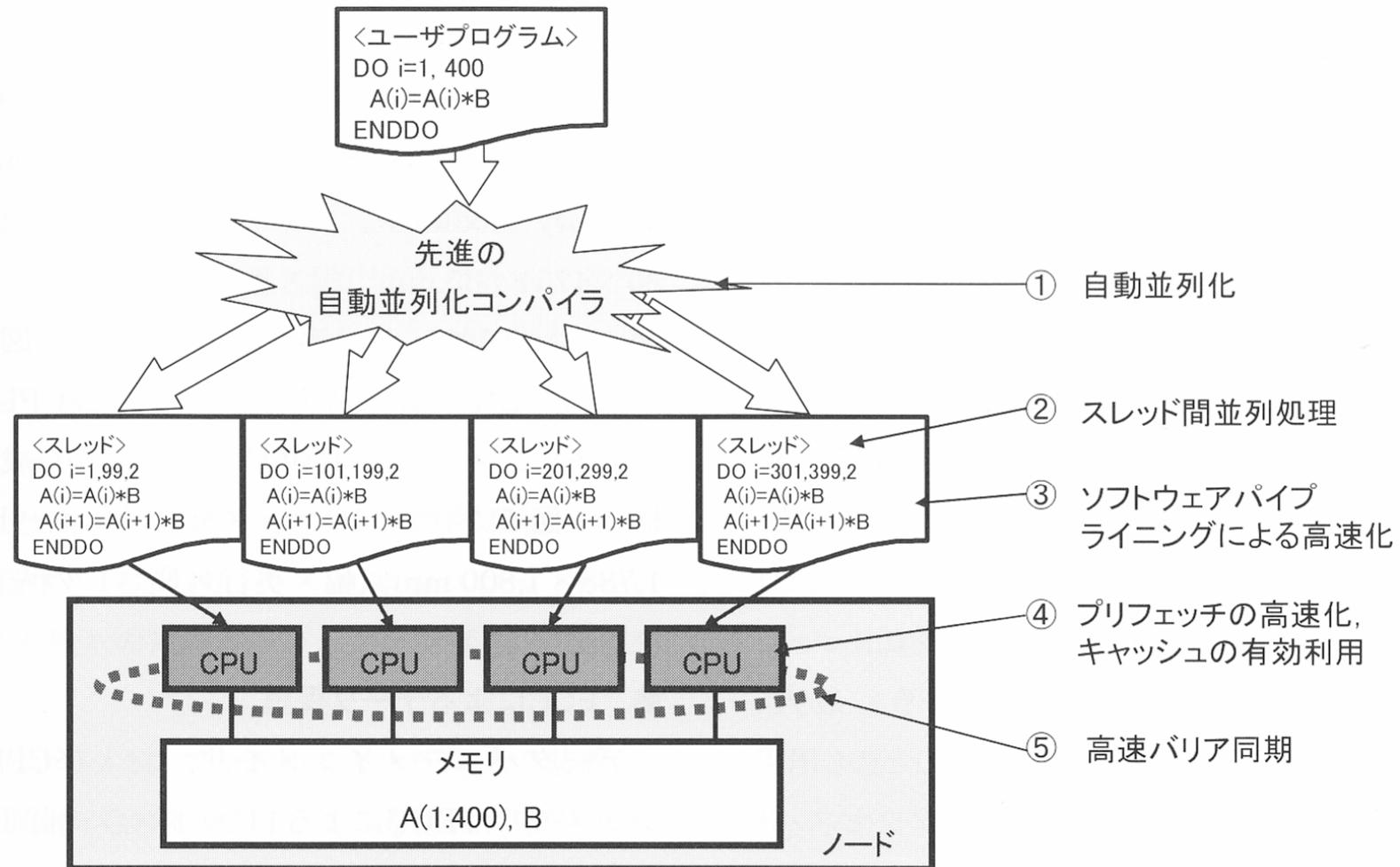

地球シミュレータ:5120台のマルチプロセッサ

ノード：8GFLOPSのプロセッサ8台、共有メモリ

システム：640ノード、メッセージ交換

(2)ベクトルパラレル VS スカラパラレル

SX-8、CRAY X1 VS SR11000,HPC2500

BlueGene/L

## メモリ共有型

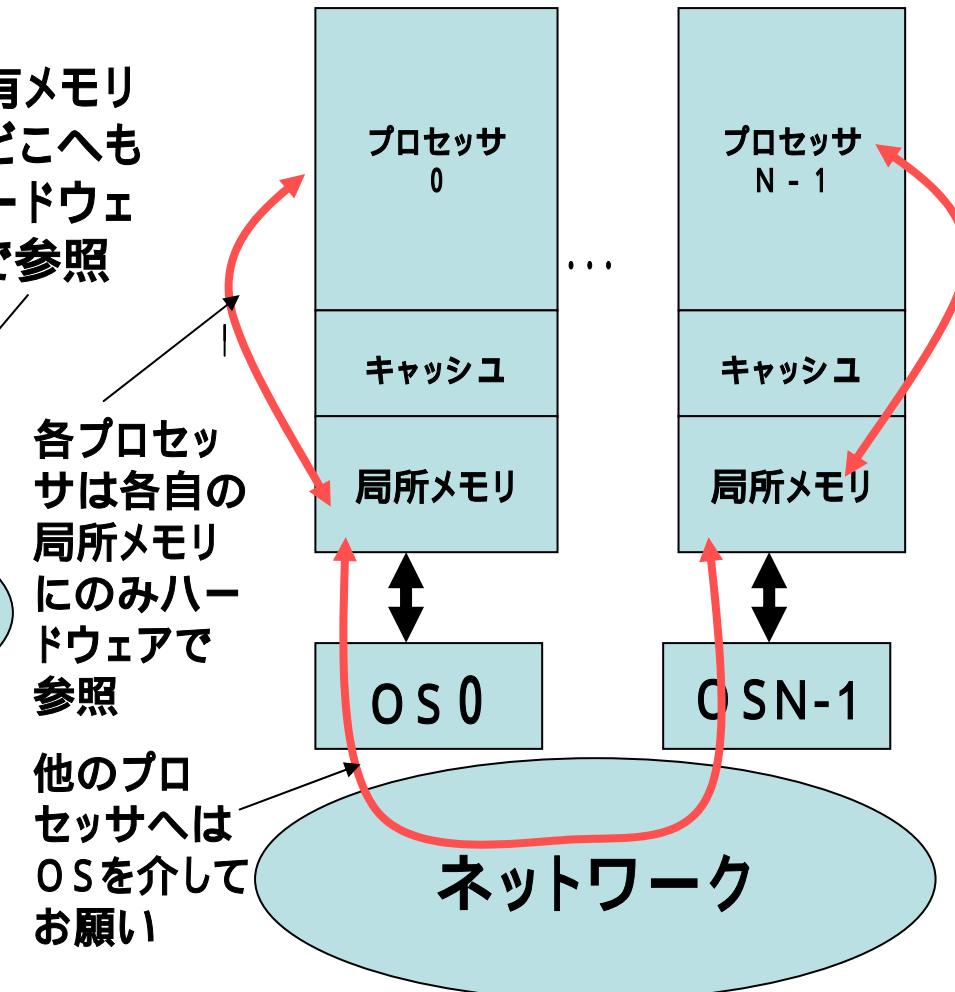

## メッセージ交換型

静的網

(a) 完全網

(b) スター網

(c) 木状網

(d) リング網

(e) 格子網(トーラス網)

(最上・下, 最左・右を結合)

(f) ハイパーキューブ網

動的網

(a) クロスバー網

(b) Benes網

(c) オメガ網

多段結合網

○：演算装置やプロセッサ

マルチプロセッサのパイオニア：

C.mmp：カーネギーメロン大、1971年、16台

PACS：筑波大、1984年、128台

LINCS：阪大、1985年、64台

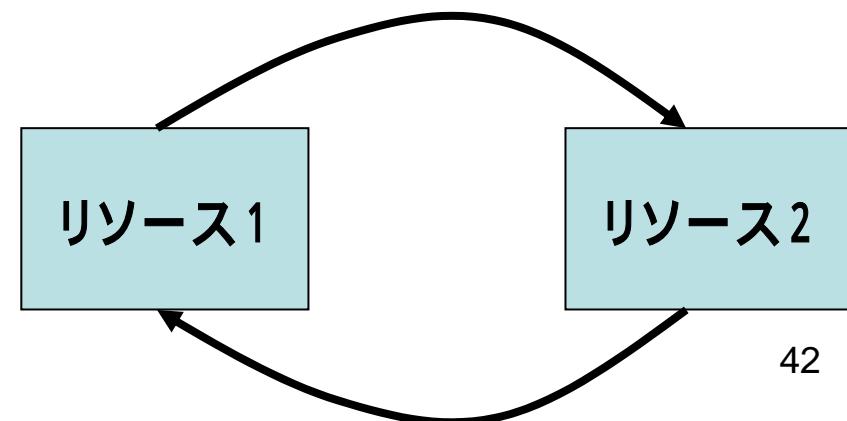

マルチプロセッサの課題

ネットワークを介した高速データ転送

プロセッサ間の高速同期機構

最適な処理粒度：通信時間に比べて処理時間が大き

くないとダメである

プログラム分割

デッドロック対策

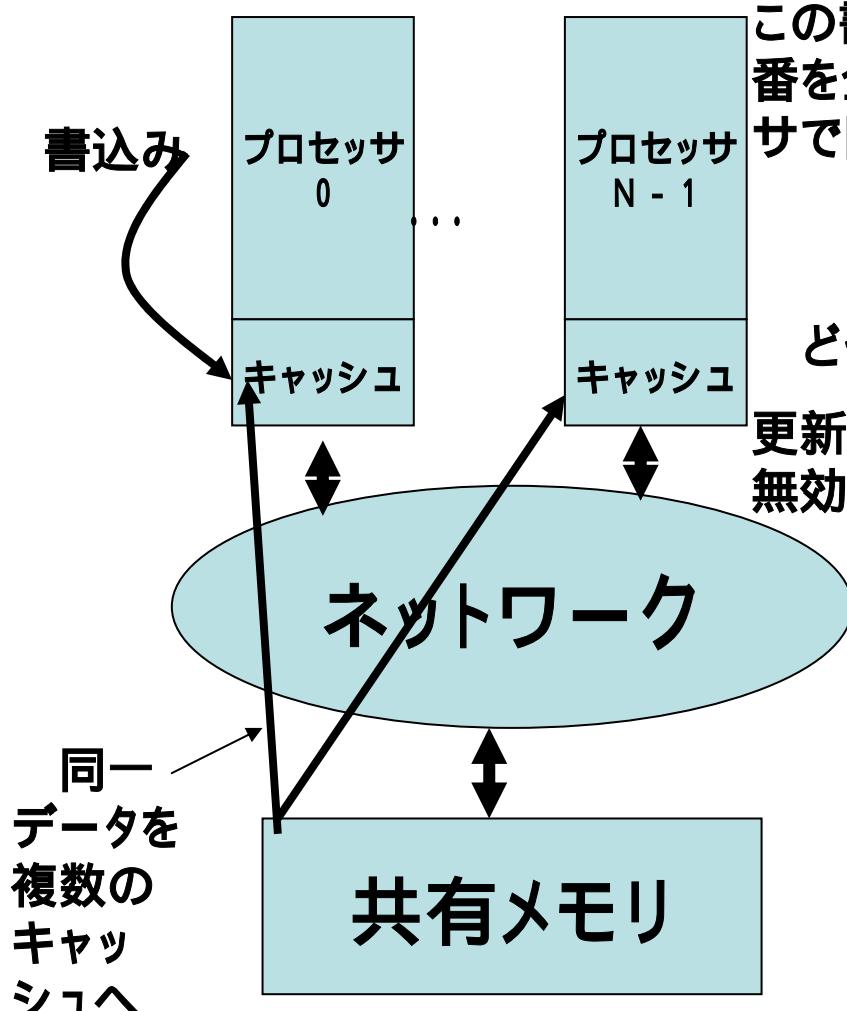

## 7.5.2 メモリ共有の2つの問題

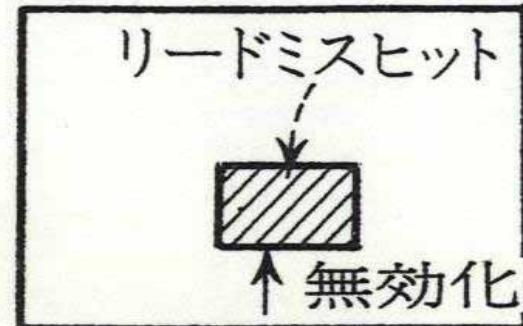

### キャッシュコヒーレンス問題

プロセッサ0、1続

けて書き込み

### メモリコンシステム問題

### 7.5.3メッセージ交換方式の問題点

OSの介在で処理時間が長い: 10 msec

ユーザレベル通信

OSの介在の少ない方式: OSバイパス

Zero-Copy

仮想記憶によるセキュリティ確保

数  $\mu$  秒へ

| MPI Benchmark                   | MX/Myrinet<br>Myricom<br>10G Myrinet<br>switch | MX/Ethernet<br>Fulcrum<br>10G Ethernet<br>switch | MX/Ethernet<br>Fujitsu<br>10G Ethernet<br>switch | OpenIB with<br>Intel MPI<br>Mellanox<br>InfiniBand |

|---------------------------------|------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------------------------|

| PingPong latency                | 2.4μs                                          | 2.4μs                                            | 2.8μs                                            | 4.0μs                                              |

| One-way data rate<br>(PingPong) | 1204 MByte/s                                   | 1201 MByte/s                                     | 1002 MByte/s                                     | 964 MByte/s                                        |

| Two-way data rate<br>(SendRecv) | 2397 MByte/s                                   | 2162 MByte/s                                     | 1762 MByte/s                                     | 1902 MByte/s                                       |

MX: Myrinet Express: メッセージパッシングソフト

Myri-10G: 10 Gigabit/s, dual protocol NIC

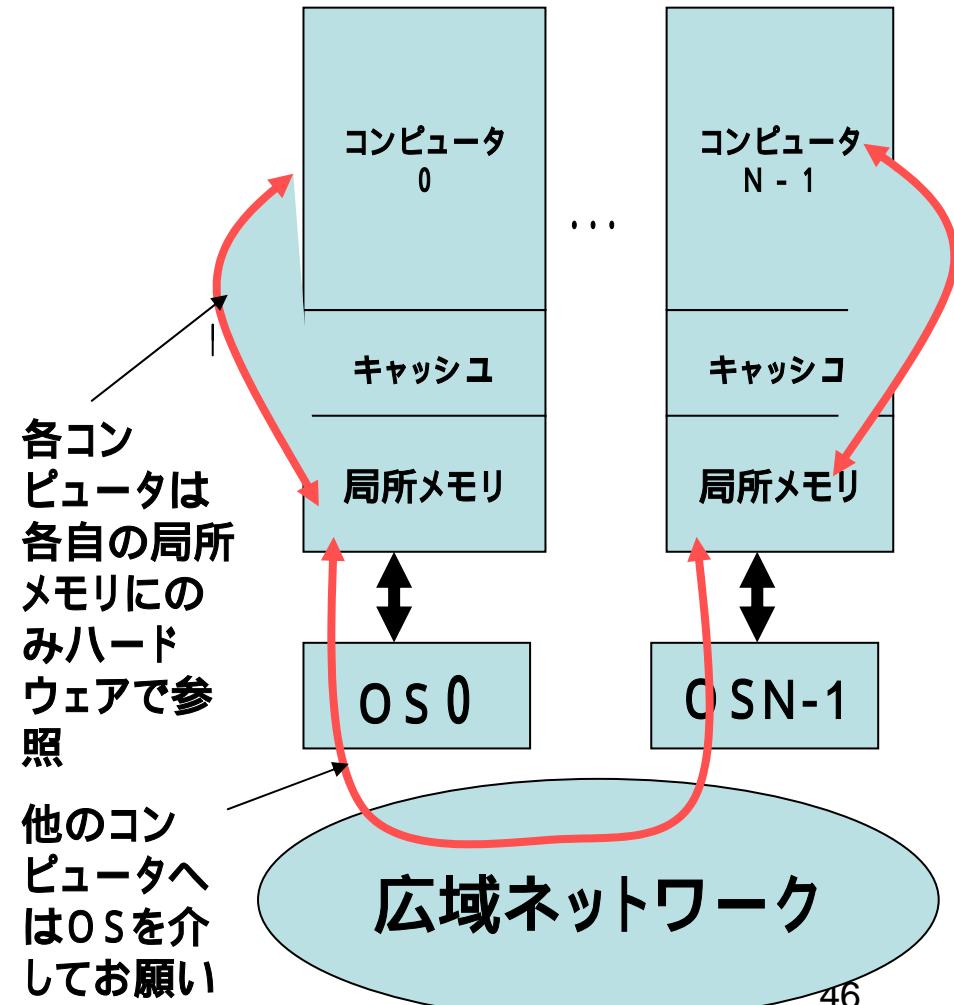

## 7.5.4マルチコンピュータ

- ・メッセージ交換型マルチプロセッサの広域版

- ・各コンピュータは他の仕事も行っている。

負荷の分散

- ・ネットワークの遅延大、

込み具合に依存

光1000km:3.3msec

- ・安全性の確保

NoW: Network of Workstations: ルーツ、1990年代

クラスタコンピューティング

パソコンと市販の高速ネットワーク (Myrinetなど) で接続

Commodity Computing (日常品によるシステム構築)

グリッドコンピューティング

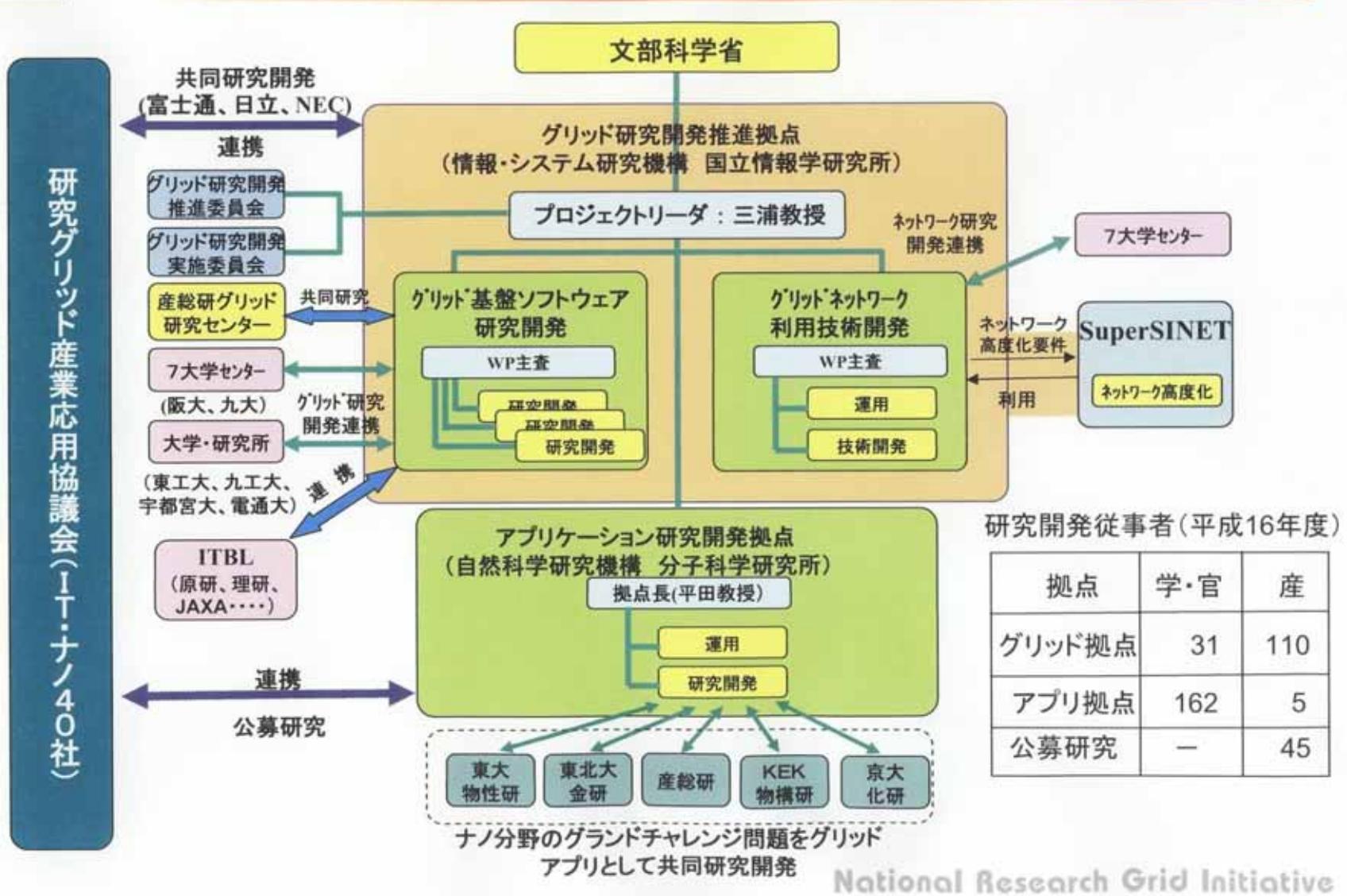

超高速コンピュータ網形成プロジェクト

(NAREGI: National Research Grid Initiative)

文部科学省: 平成15年から20年

100 TFLOPSの性能を目指

## 7.5.5 マルチプロセッサ、コンピュータの問題点

超高性能なコンピュータの実現：

マルチプロセッサやマルチコンピュータ

しかないが、…

# ユーザからみた問題点

## 不連続性

過去のプログラムの大幅な手直し

## 複雑性

- 並列アルゴリズムの複雑性

パイプライン方式: 1次元ベクトルを意識

マルチプロセッサ: 相互結合網

(ネットワーク)の2、3次元構造

効率のよいアルゴリズムを作成: 困難

たとえば、1から100までの数のすべての部分和

( $1+2, 1+2+3, \dots, 1+2+\cdots+100$ ) 計算

パイプラインでは非常に簡単

マルチプロセッサでは非常に難しい

- 並列プログラミングの複雑性

SIMD方式やパイプライン方式

- 1つの命令で多数のデータに対して同一演算

- 1つ1つの命令は逐次実行

- 集合データに対する「逐次」プログラム

- 逐次プログラムは何度実行して同一結果

- 決定的(deterministic)

- デバッグも簡単

- デッドロックなし

- 専用性

- 多様性 移植性

- 市場性

## 7.6 最新のスーパコンピュータと 地球シミュレータ

### 7.6.1 最新のシステム例

選択肢

要素プロセッサ

ベクトルプロセッサかスカラープロセッサ

メモリ共有かメッセージ交換か

ネットワークの構成は

FUJITSU PRIMEPOWER HPC2500

地球シミュレータ(NEC SX-8)

日立SR11000

CRAY X1

BlueGene/L

(1) ベクトルパラレル VS スカラパラレル

(2) メモリ共有 VS メッセージ交換

(3) ネットワーク

クロスバ

VS トーラスなど他網

ベクトルプロセッサを多数並べる

普通のマイクロプロセッサを多数並べる

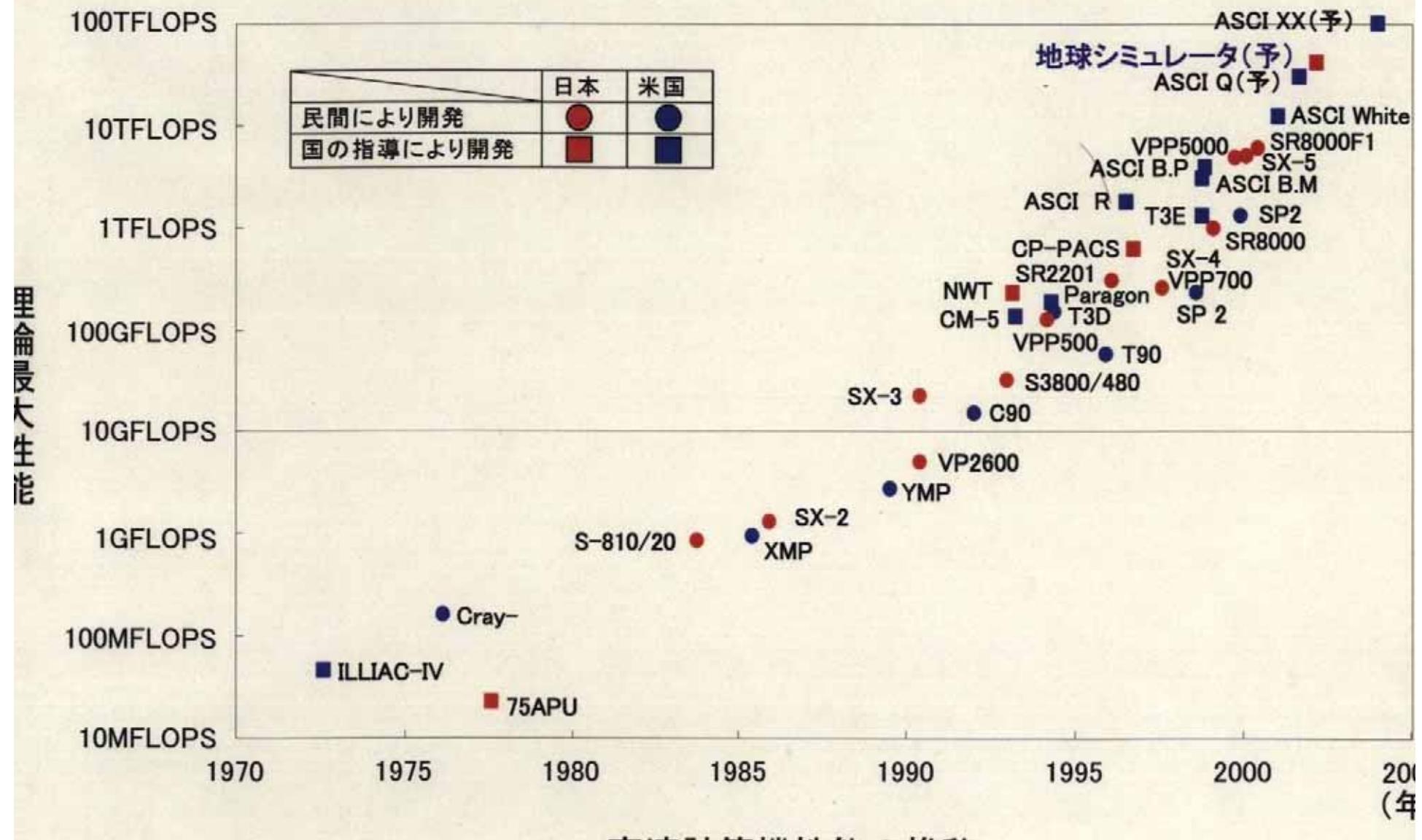

## 地球シミュレータの性能の位置づけ

# NEC

| 機種                                          | 年    | サイクル単体性能 | 最大性能   | 台数            |

|---------------------------------------------|------|----------|--------|---------------|

| Cray-1                                      | 1976 | 12.5ns   | 160MF  | 1台            |

| SX-1/2                                      | 1984 | 6ns      | 1.3GF  | 1台            |

| SX-3                                        | 1989 | 2.9ns    | 5.5GF  | 22GF<br>4台    |

| SX-4                                        | 1994 | 8ns      | 2GF    | 1TF<br>512台   |

| SX-5                                        | 1998 | 4ns      | 8GF    | 4TF<br>512台   |

| SX-6                                        | 2001 | 2ns      | 8GF    | 8TF<br>1024台  |

| (CMOSシングルチップ、8PE/1ノード、最大128ノード、<br>0.15 μm) |      |          |        |               |

| SX-7                                        | 2002 | 1.8ns    | 11.4GF | 23TF<br>2048台 |

| (32PE/1ノード、最大64ノード、0.15 μm)                 |      |          |        |               |

| SX-8                                        | 2004 | 0.5ns    | 16GF   | 65TF<br>4096台 |

| (8PE/1ノード、最大512ノード、0.09 μm)                 |      |          |        |               |

# 日立

## ベクトルパラレル

1982 S-810 630MFLOPS

1987 S-820 3GFLOPS

1992 S-3000 32GFLOPS

## スカラパラレル

1995 SR2201 600GFLOPS

1999 SR8000 7.3TFLOPS

2003 SR11000 62TFLOPS

(Power5(1.9GHz)、16PE/ノード、121.6GFLOPS/ノード、最大

512ノード、多段クロスバネット: 12GB/sx2(ノード当たり))

# FUJITSU PRIMEPOWER HPC

## VPPからSPPに切り替え

図-1 PRIMEPOWER HPCシステムの構成

Fig.1-System configuration of PRIMEPOWER HPC.

ノード: 共有メモリ、

スヌープ方式

SMP

512インタリーブ

メモリ(ノード内)

Fujitsu Vol.53, No.6,

2002,特集 サーバ

# • Fujitsu PRIMEPOWER HPC

表-1 PRIMEPOWER HPCノード諸元

| 項目             | 諸元         |

|----------------|------------|

| CPU            | SPARC64 V  |

| CPU周波数         | 1.3 GHz    |

| 最大CPU数         | 128        |

| アドレススヌープ性能     | 133 Gバイト/秒 |

| 最大メインメモリ容量     | 512 Gバイト   |

| 最大メインメモリインターブ数 | 512ウェイ     |

| 最大PCIスロット数     | 320        |

表-2 PRIMEPOWER HPCシステム諸元

| 項目         | 諸元                               |

|------------|----------------------------------|

| 最大ノード数     | 128                              |

| 最大CPU数     | 16,384                           |

| 最大論理性能     | 85.2 TFLOPS*                     |

| 最大メインメモリ容量 | 64 Tバイト                          |

| ノード間結合方式   | クロスバ                             |

| ノード間転送性能   | 1ノードあたり<br>最大16 Gバイト/秒×2 (入力/出力) |

\* : Tera FLoating point Operation Per Second

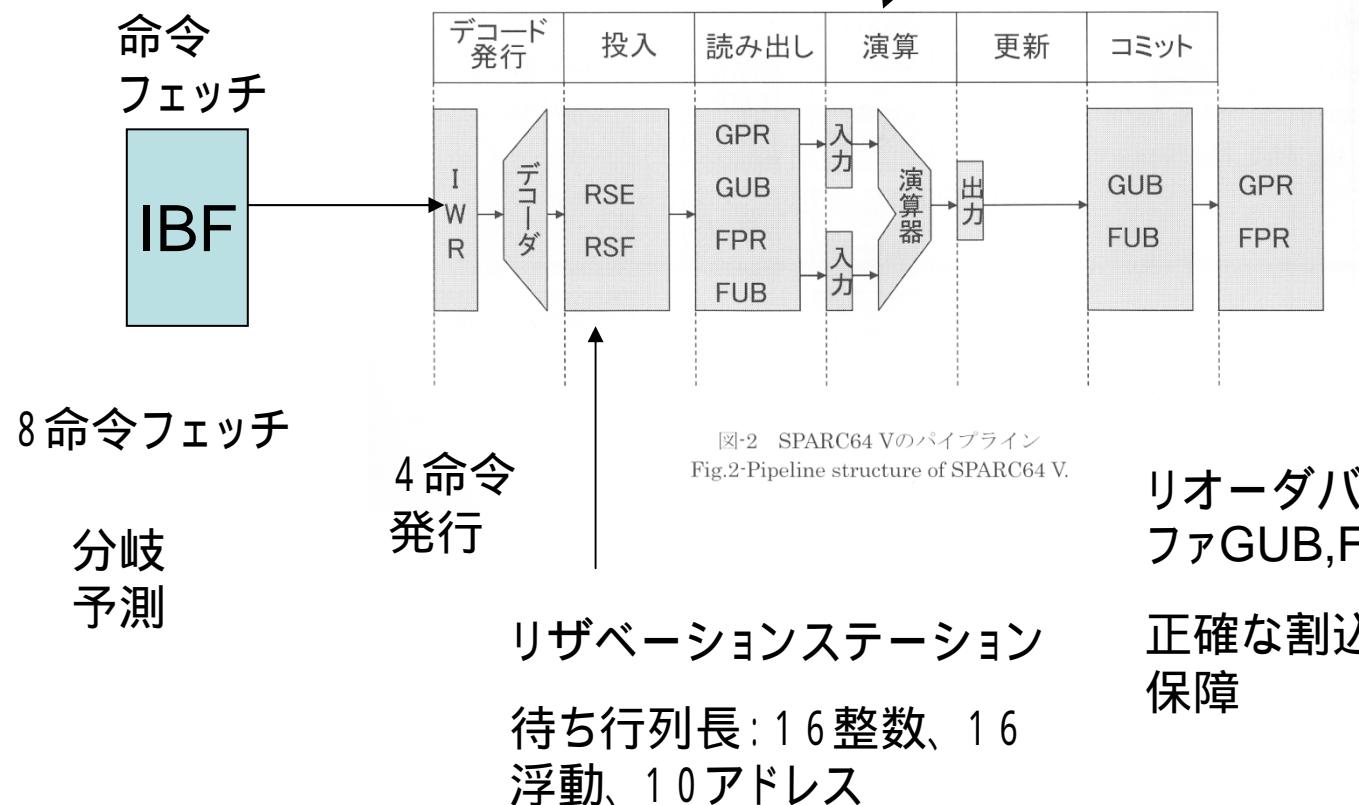

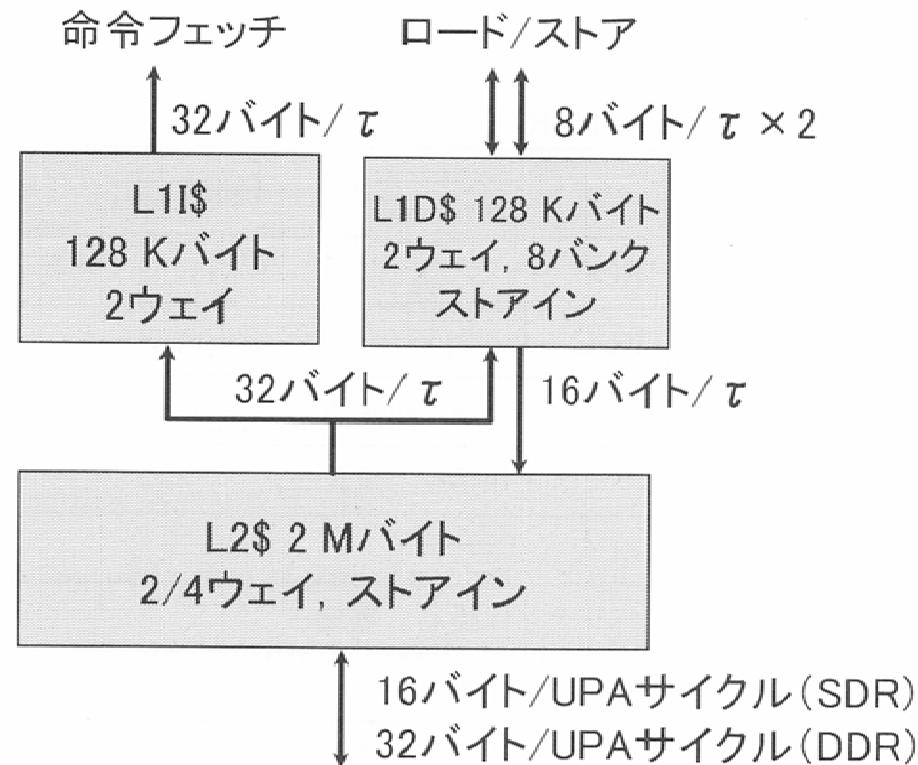

# SPARC64 V

整数演算2台、

浮動小数点2台、

アドレス計算2台

5.2GFLOPS

SDR: Single Data Rate DDR: Double Data Rate

$\tau$  : CPUコアサイクル

図-3 SPARC64 Vのキャッシュ

Fig.3-Cache structure of SPARC64 V.

デザインルール: 0.13 μ m

TR数: 19,100万個

信号ピン数: 269

チップサイズ: 17.8x15.7mm

動作周波数: 1 . 3 GHz

消費電力: 50W

## 7.6.2 TOP500

June2000

| Rank | Site                                                           | Computer                                     | Processors | Year | R <sub>max</sub> | R <sub>peak</sub> |

|------|----------------------------------------------------------------|----------------------------------------------|------------|------|------------------|-------------------|

| 1    | Sandia National Laboratories<br>United States                  | ASCI Red<br>Intel                            | 9632       | 1999 | 2379             | 3207              |

| 2    | Lawrence Livermore National Laboratory<br>United States        | ASCI Blue-Pacific SST,<br>IBM SP 604e<br>IBM | 5808       | 1999 | 2144             | 3856.5            |

| 3    | Los Alamos National Laboratory<br>United States                | ASCI Blue Mountain<br>SGI                    | 6144       | 1998 | 1608             | 3072              |

| 4    | IBM/Naval Oceanographic Office<br>(NAVOCEANO)<br>United States | SP Power3 375 MHz<br>IBM                     | 1336       | 2000 | 1417             | 2004              |

| 5    | Leibniz Rechenzentrum<br>Germany                               | SR8000-F1/112<br>Hitachi                     | 112        | 2000 | 1035             | 1344              |

| 6    | High Energy Accelerator Research<br>Organization /KEK<br>Japan | SR8000-F1/100<br>Hitachi                     | 100        | 2000 | 917              | 1200              |

| 7    | Government<br>United States                                    | T3E1200<br>Cray Inc.                         | 1084       | 1998 | 891              | 1300.8            |

| 8    | US Army HPC Research Center at NCS<br>United States            | T3E1200<br>Cray Inc.                         | 1084       | 2000 | 891              | 1300.8            |

| 9    | University of Tokyo<br>Japan                                   | SR8000/128<br>Hitachi                        | 128        | 1999 | 873              | 1024              |

| 10   | Government<br>United States                                    | T3E900<br>Cray Inc.                          | 1324       | 1997 | 815              | 1191.6            |

# TOP500LIST-June2001

| Rank | Site                                                                            | Computer                                                   | Processors | Year | R <sub>max</sub> | R <sub>peak</sub> |

|------|---------------------------------------------------------------------------------|------------------------------------------------------------|------------|------|------------------|-------------------|

| 1    | <u>Lawrence Livermore National Laboratory</u><br>United States                  | <u>ASCI White, SP Power3</u><br><u>375 MHz</u><br>IBM      | 8192       | 2000 | 7226             | 12288             |

| 2    | <u>NERSC/LBNL</u><br>United States                                              | <u>SP Power3 375 MHz 16</u><br><u>way</u><br>IBM           | 2528       | 2001 | 2526             | 3792              |

| 3    | <u>Sandia National Laboratories</u><br>United States                            | <u>ASCI Red</u><br>Intel                                   | 9632       | 1999 | 2379             | 3207              |

| 4    | <u>Lawrence Livermore National Laboratory</u><br>United States                  | <u>ASCI Blue-Pacific SST,</u><br><u>IBM SP 604e</u><br>IBM | 5808       | 1999 | 2144             | 3856.5            |

| 5    | <u>University of Tokyo</u><br>Japan                                             | <u>SR8000/MPP</u><br>Hitachi                               | 1152       | 2001 | 1709.1           | 2074              |

| 6    | <u>Los Alamos National Laboratory</u><br>United States                          | <u>ASCI Blue Mountain</u><br>SGI                           | 6144       | 1998 | 1608             | 3072              |

| 7    | <u>Naval Oceanographic Office</u><br><u>(NAVOCEANO)</u><br>United States        | <u>SP Power3 375 MHz</u><br>IBM                            | 1336       | 2000 | 1417             | 2004              |

| 8    | <u>Osaka University</u><br>Japan                                                | <u>SX-5/128M8 3.2ns</u><br>NEC                             | 128        | 2001 | 1192             | 1280              |

| 9    | <u>National Centers for Environmental</u><br><u>Prediction</u><br>United States | <u>SP Power3 375 MHz</u><br>IBM                            | 1104       | 2000 | 1179             | 1656              |

| 10   | <u>National Centers for Environmental</u><br><u>Prediction</u><br>United States | <u>SP Power3 375 MHz</u><br>IBM                            | 1104       | 2001 | 1179             | 1656              |

# TOP500LIST-

## June2002

| Rank | Site                                                       | Computer                                     | Processors | Year | R <sub>max</sub> | R <sub>peak</sub> |

|------|------------------------------------------------------------|----------------------------------------------|------------|------|------------------|-------------------|

| 1    | The Earth Simulator Center<br>Japan                        | Earth-Simulator<br>NEC                       | 5120       | 2002 | 35860            | 40960             |

| 2    | Lawrence Livermore National<br>Laboratory<br>United States | ASCI White, SP Power3 375<br>MHz<br>IBM      | 8192       | 2000 | 7226             | 12288             |

| 3    | Pittsburgh Supercomputing Center<br>United States          | AlphaServer SC45, 1 GHz<br>Hewlett-Packard   | 3016       | 2001 | 4463             | 6032              |

| 4    | Commissariat a l'Energie Atomique<br>(CEA)<br>France       | AlphaServer SC45, 1 GHz<br>Hewlett-Packard   | 2560       | 2001 | 3980             | 5120              |

| 5    | NERSC/LBNL<br>United States                                | SP Power3 375 MHz 16 way<br>IBM              | 3328       | 2001 | 3052             | 4992              |

| 6    | Los Alamos National Laboratory<br>United States            | AlphaServer SC45, 1 GHz<br>Hewlett-Packard   | 2048       | 2002 | 2916             | 4096              |

| 7    | Sandia National Laboratories<br>United States              | ASCI Red<br>Intel                            | 9632       | 1999 | 2379             | 3207              |

| 8    | Oak Ridge National Laboratory<br>United States             | pSeries 690 Turbo 1.3GHz<br>IBM              | 864        | 2002 | 2310             | 4492.8            |

| 9    | Lawrence Livermore National<br>Laboratory<br>United States | ASCI Blue-Pacific SST,<br>IBM SP 604e<br>IBM | 5808       | 1999 | 2144             | 3856.5            |

| 10   | IBM/US Army Research Laboratory<br>(ARL)<br>United States  | pSeries 690 Turbo 1.3GHz<br>IBM              | 768        | 2002 | 2050             | 3993.6            |

# TOP500LIST-June2003

| Rank | Site                                                       | Computer                                                                             | Processors | Year | R <sub>max</sub> | R <sub>peak</sub> |

|------|------------------------------------------------------------|--------------------------------------------------------------------------------------|------------|------|------------------|-------------------|

| 1    | The Earth Simulator Center<br>Japan                        | Earth-Simulator<br>NEC                                                               | 5120       | 2002 | 35860            | 40960             |

| 2    | Los Alamos National Laboratory<br>United States            | ASCI Q - AlphaServer SC45, 1.25<br>GHz<br>Hewlett-Packard                            | 8192       | 2002 | 13880            | 20480             |

| 3    | Lawrence Livermore National<br>Laboratory<br>United States | MCR Linux Cluster Xeon 2.4 GHz<br>- Quadrics<br>Linux Networx/Quadrics               | 2304       | 2002 | 7634             | 11060             |

| 4    | Lawrence Livermore National<br>Laboratory<br>United States | ASCI White, SP Power3 375 MHz<br>IBM                                                 | 8192       | 2000 | 7304             | 12288             |

| 5    | NERSC/LBNL<br>United States                                | Seaborg - SP Power3 375 MHz 16<br>way<br>IBM                                         | 6656       | 2002 | 7304             | 9984              |

| 6    | Lawrence Livermore National<br>Laboratory<br>United States | xSeries Cluster Xeon 2.4 GHz -<br>Quadrics<br>IBM/Quadrics                           | 1920       | 2003 | 6586             | 9216              |

| 7    | National Aerospace Laboratory of<br>Japan<br>Japan         | PRIMEPOWER HPC2500 (1.3<br>GHz)<br>Fujitsu                                           | 2304       | 2002 | 5406             | 11980             |

| 8    | Pacific Northwest National<br>Laboratory<br>United States  | Cluster Platform 6000 rx2600<br>Itanium2 1 GHz Cluster - Quadrics<br>Hewlett-Packard | 1540       | 2003 | 4881             | 6160              |

| 9    | Pittsburgh Supercomputing<br>Center<br>United States       | AlphaServer SC45, 1 GHz<br>Hewlett-Packard                                           | 3016       | 2001 | 4463             | 6032              |

| 10   | Commissariat a l'Energie<br>Atomique (CEA)<br>France       | AlphaServer SC45, 1 GHz<br>Hewlett-Packard                                           | 2560       | 2001 | 3980             | 5120              |

# TOP500LIST-June2004

| <b>Rank</b> | <b>Site</b>                                                 | <b>Computer</b>                                                                        | <b>Processors</b> | <b>Year</b> | <b>R<sub>max</sub></b> | <b>R<sub>peak</sub></b> |

|-------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------|-------------|------------------------|-------------------------|

| 1           | The Earth Simulator Center<br>Japan                         | Earth-Simulator<br>NEC                                                                 | 5120              | 2002        | 35860                  | 40960                   |

| 2           | Lawrence Livermore National<br>Laboratory<br>United States  | Thunder - Intel Itanium2 Tiger4<br>1.4GHz - Quadrics<br>California Digital Corporation | 4096              | 2004        | 19940                  | 22938                   |

| 3           | Los Alamos National<br>Laboratory<br>United States          | ASCI Q - AlphaServer SC45, 1.25<br>GHz<br>Hewlett-Packard                              | 8192              | 2002        | 13880                  | 20480                   |

| 4           | IBM - Rochester<br>United States                            | BlueGene/L DD1 Prototype (0.5GHz<br>PowerPC 440 w/Custom)<br>IBM/ LLNL                 | 8192              | 2004        | 11680                  | 16384                   |

| 5           | NCSA<br>United States                                       | Tungsten - PowerEdge 1750, P4<br>Xeon 3.06 GHz, Myrinet<br>Dell                        | 2500              | 2003        | 9819                   | 15300                   |

| 6           | ECMWF<br>United Kingdom                                     | eServer pSeries 690 (1.9 GHz<br>Power4+)<br>IBM                                        | 2112              | 2004        | 8955                   | 16051                   |

| 7           | Institute of Physical and<br>Chemical Res. (RIKEN)<br>Japan | RIKEN Super Combined Cluster<br>Fujitsu                                                | 2048              | 2004        | 8728                   | 12534                   |

| 8           | IBM Thomas J. Watson<br>Research Center<br>United States    | BlueGene/L DD2 Prototype (0.7<br>GHz PowerPC 440)<br>IBM/ LLNL                         | 4096              | 2004        | 8655                   | 11469                   |

| 9           | Pacific Northwest National<br>Laboratory<br>United States   | Mpp2 - Cluster Platform 6000<br>rx2600 Itanium2 1.5 GHz, Quadrics<br>Hewlett-Packard   | 1936              | 2003        | 8633                   | 11616                   |

| 10          | Shanghai Supercomputer Center<br>China                      | Dawning 4000A, Opteron 2.2 GHz,<br>Myrinet<br>Dawning                                  | 2560              | 2004        | 8061                   | 11264                   |

# TOP500LIST-June2005

| <b>Rank</b> | <b>Site</b>                                             | <b>Computer</b>                                                                        | <b>Processors</b> | <b>Year</b> | <b>R<sub>max</sub></b> | <b>R<sub>peak</sub></b> |

|-------------|---------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------|-------------|------------------------|-------------------------|

| 1           | DOE/NNSA/LLNL<br>United States                          | BlueGene/L - eServer Blue Gene Solution<br>IBM                                         | 65536             | 2005        | 136800                 | 183500                  |

| 2           | IBM Thomas J. Watson Research Center<br>United States   | BGW - eServer Blue Gene Solution<br>IBM                                                | 40960             | 2005        | 91290                  | 114688                  |

| 3           | NASA/Ames Research Center/NAS<br>United States          | Columbia - SGI Altix 1.5 GHz,<br>Voltaire Infiniband<br>SGI                            | 10160             | 2004        | 51870                  | 60960                   |

| 4           | The Earth Simulator Center<br>Japan                     | Earth-Simulator<br>NEC                                                                 | 5120              | 2002        | 35860                  | 40960                   |

| 5           | Barcelona Supercomputer Center<br>Spain                 | MareNostrum - JS20 Cluster, PPC<br>970, 2.2 GHz, Myrinet<br>IBM                        | 4800              | 2005        | 27910                  | 42144                   |

| 6           | ASTRON/University Groningen<br>Netherlands              | Stella - eServer Blue Gene Solution<br>IBM                                             | 12288             | 2005        | 27450                  | 34406.4                 |

| 7           | Lawrence Livermore National Laboratory<br>United States | Thunder - Intel Itanium2 Tiger4<br>1.4GHz - Quadrics<br>California Digital Corporation | 4096              | 2004        | 19940                  | 22938                   |

| 8           | Computational Biology Research Center, AIST<br>Japan    | Blue Protein - eServer Blue Gene Solution<br>IBM                                       | 8192              | 2005        | 18200                  | 22937.6                 |

| 9           | Ecole Polytechnique Federale de Lausanne<br>Switzerland | eServer Blue Gene Solution<br>IBM                                                      | 8192              | 2005        | 18200                  | 22937.6                 |

| 10          | Sandia National Laboratories<br>United States           | Red Storm, Cray XT3, 2.0 GHz<br>Cray Inc.                                              | 5000              | 2005        | 15250                  | 20000                   |

# TOP500LIST-June2006

| Rank | Site                                                         | Computer                                                                                       | Processors | Year | R <sub>max</sub> | R <sub>peak</sub> |

|------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|------|------------------|-------------------|

| 1    | <u>DOE/NNSA/LLNL</u><br>United States                        | <u>BlueGene/L - eServer Blue Gene Solution</u><br>IBM                                          | 131072     | 2005 | 280600           | 367000            |

| 2    | <u>IBM Thomas J. Watson Research Center</u><br>United States | <u>BGW - eServer Blue Gene Solution</u><br>IBM                                                 | 40960      | 2005 | 91290            | 114688            |

| 3    | <u>DOE/NNSA/LLNL</u><br>United States                        | <u>ASC Purple - eServer pSeries p5 575 1.9 GHz</u><br>IBM                                      | 12208      | 2006 | 75760            | 92781             |

| 4    | <u>NASA/Ames Research Center/NAS</u><br>United States        | <u>Columbia - SGI Altix 1.5 GHz, Voltaire Infiniband</u><br>SGI                                | 10160      | 2004 | 51870            | 60960             |

| 5    | <u>Commissariat a l'Energie Atomique (CEA)</u><br>France     | <u>Tera-10 - NovaScale 5160, Itanium2 1.6 GHz, Quadrics</u><br>Bull SA                         | 8704       | 2006 | 42900            | 55705.6           |

| 6    | <u>Sandia National Laboratories</u><br>United States         | <u>Thunderbird - PowerEdge 1850, 3.6 GHz, Infiniband</u><br>Dell                               | 9024       | 2006 | 38270            | 64972.8           |

| 7    | <u>GSIC Center, Tokyo Institute of Technology</u><br>Japan   | <u>TSUBAME Grid Cluster - Sun Fire X64 Cluster, Opteron 2.4/2.6 GHz, Infiniband</u><br>NEC/Sun | 10368      | 2006 | 38180            | 49868.8           |

| 8    | <u>Forschungszentrum Juelich (FZJ)</u><br>Germany            | <u>JUBL - eServer Blue Gene Solution</u><br>IBM                                                | 16384      | 2006 | 37330            | 45875             |

| 9    | <u>Sandia National Laboratories</u><br>United States         | <u>Red Storm Cray XT3, 2.0 GHz</u><br>Cray Inc.                                                | 10880      | 2005 | 36190            | 43520             |

| 10   | <u>The Earth Simulator Center</u><br>Japan                   | <u>Earth-Simulator</u><br>NEC                                                                  | 5120       | 2002 | 35860            | 40960             |

## 7.6.3 地球シミュレータとNECスーパコンピュータ

| 機種                                      | 年           | サイクル単体性能   | 最大性能       | 台数         | Cray-1       |

|-----------------------------------------|-------------|------------|------------|------------|--------------|

|                                         | 1976        | 12.5ns     | 160MF      | 160MF      | 1台           |

| SX-1/2                                  | 1984        | 6ns        | 1.3GF      | 1.3GF      | 1台           |

| SX-3                                    | 1989        | 2.9ns      | 5.5GF      | 22GF       | 4台           |

| SX-4                                    | 1994        | 8ns        | 2GF        | 1TF        | 512台         |

| SX-5                                    | 1998        | 4ns        | 8GF        | 4TF        | 512台         |

| <u>SX-6</u>                             | <u>2001</u> | <u>2ns</u> | <u>8GF</u> | <u>8TF</u> | <u>1024台</u> |

| (CMOSシングルチップ、8PE/1ノード、最大128ノード、0.15 μm) |             |            |            |            |              |

| SX-7                                    | 2002        | 1.8ns      | 11.4GF     | 23TF       | 2048台        |

| (32PE/1ノード、最大64ノード、0.15 μm)             |             |            |            |            |              |

| SX-8                                    | 2004        | 0.5ns      | 16GF       | 65TF       | 4096台        |

| (8PE/1ノード、最大512ノード、0.09 μm)             |             |            |            |            |              |

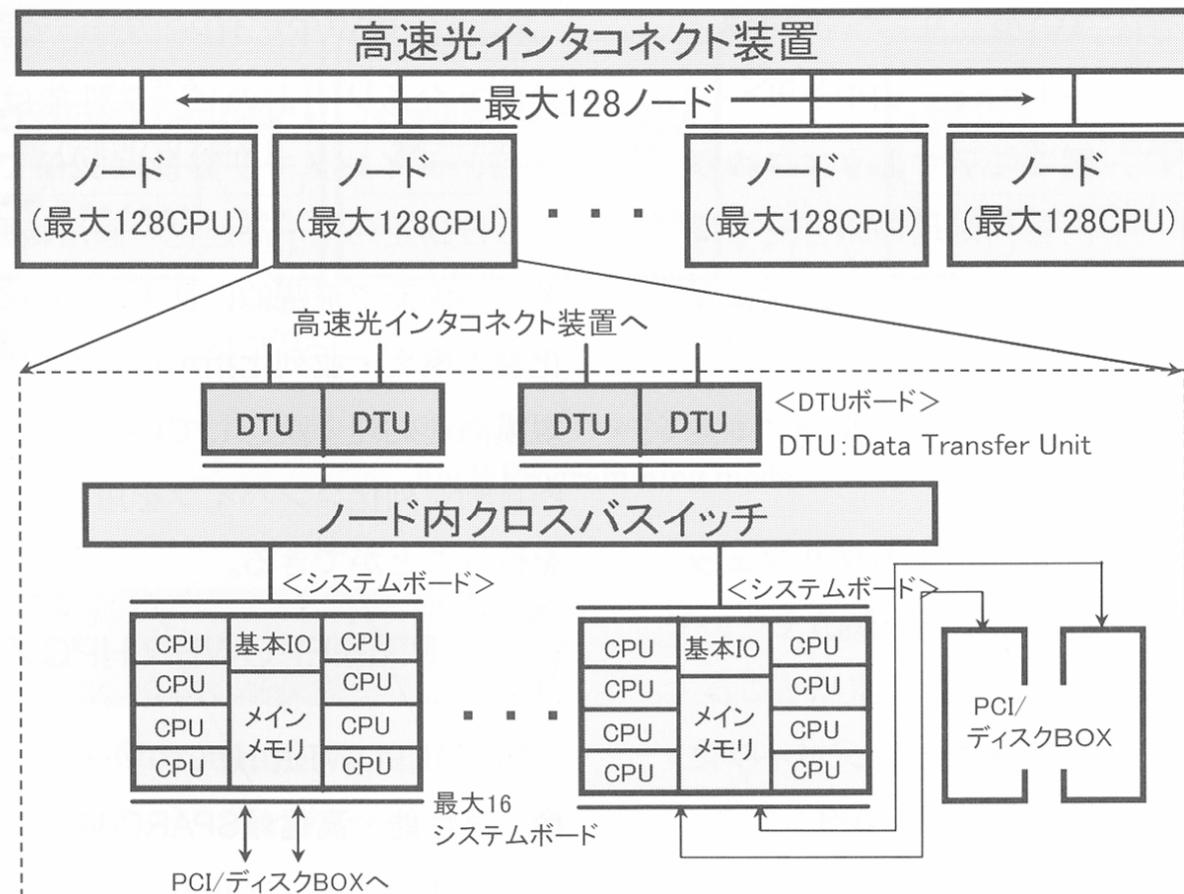

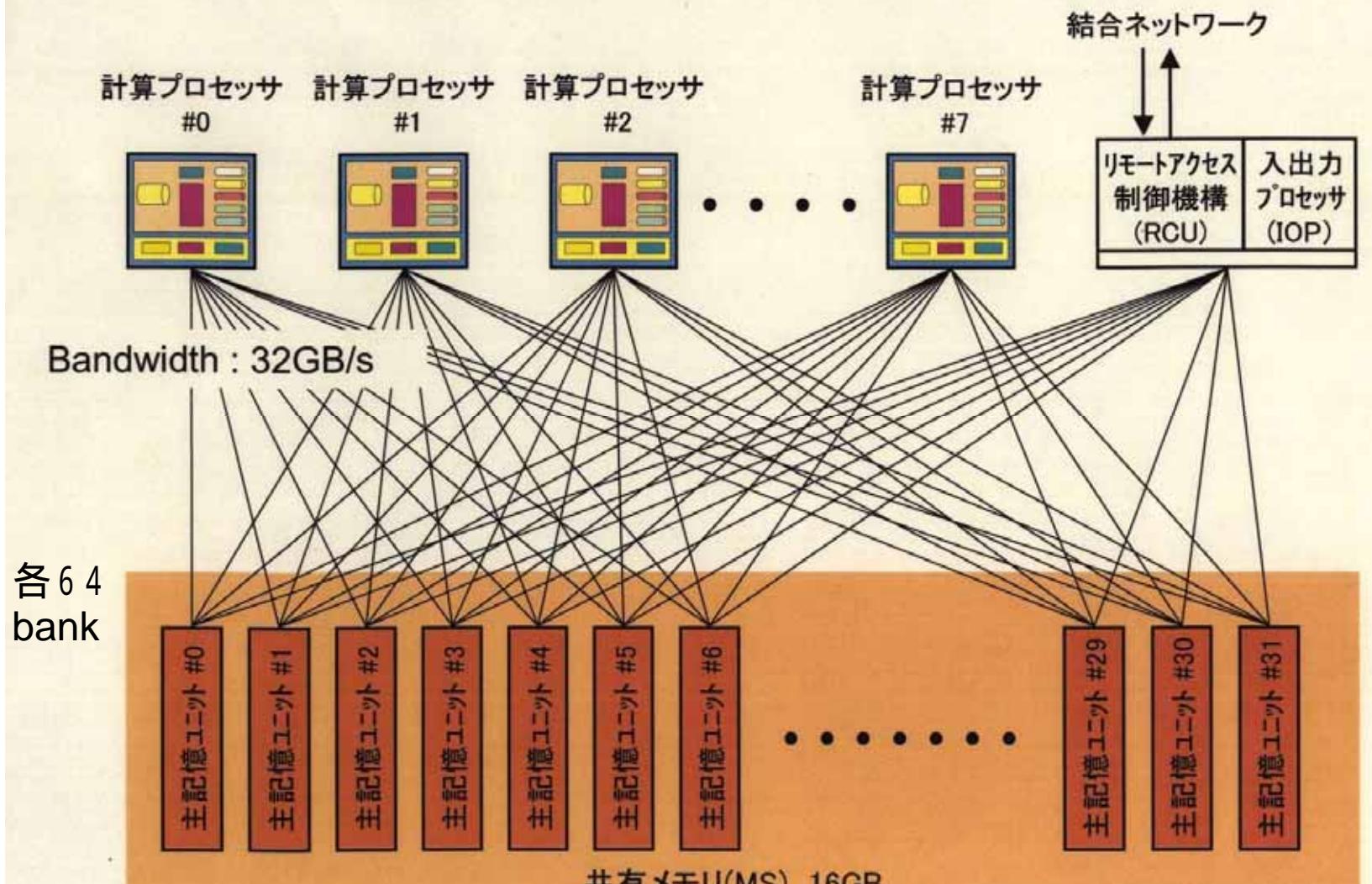

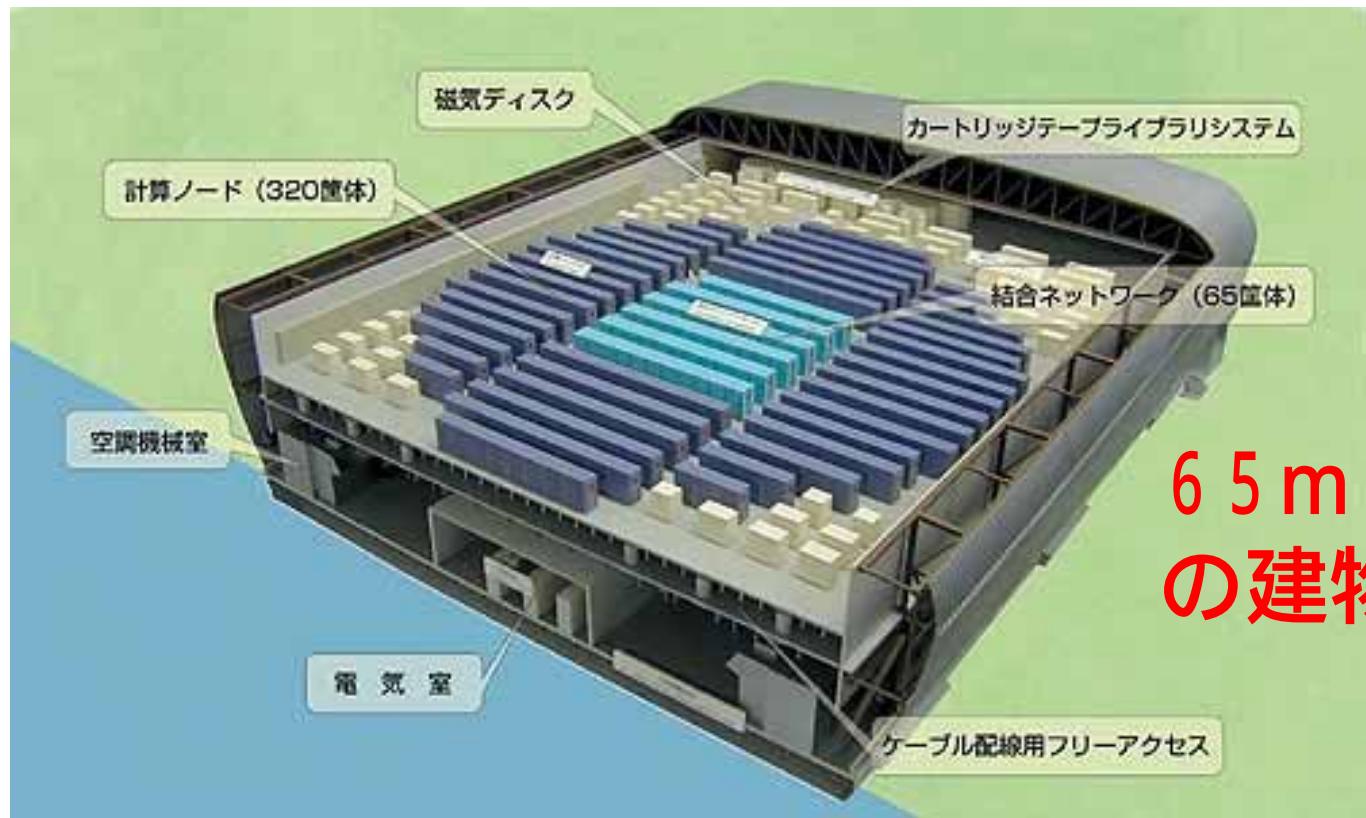

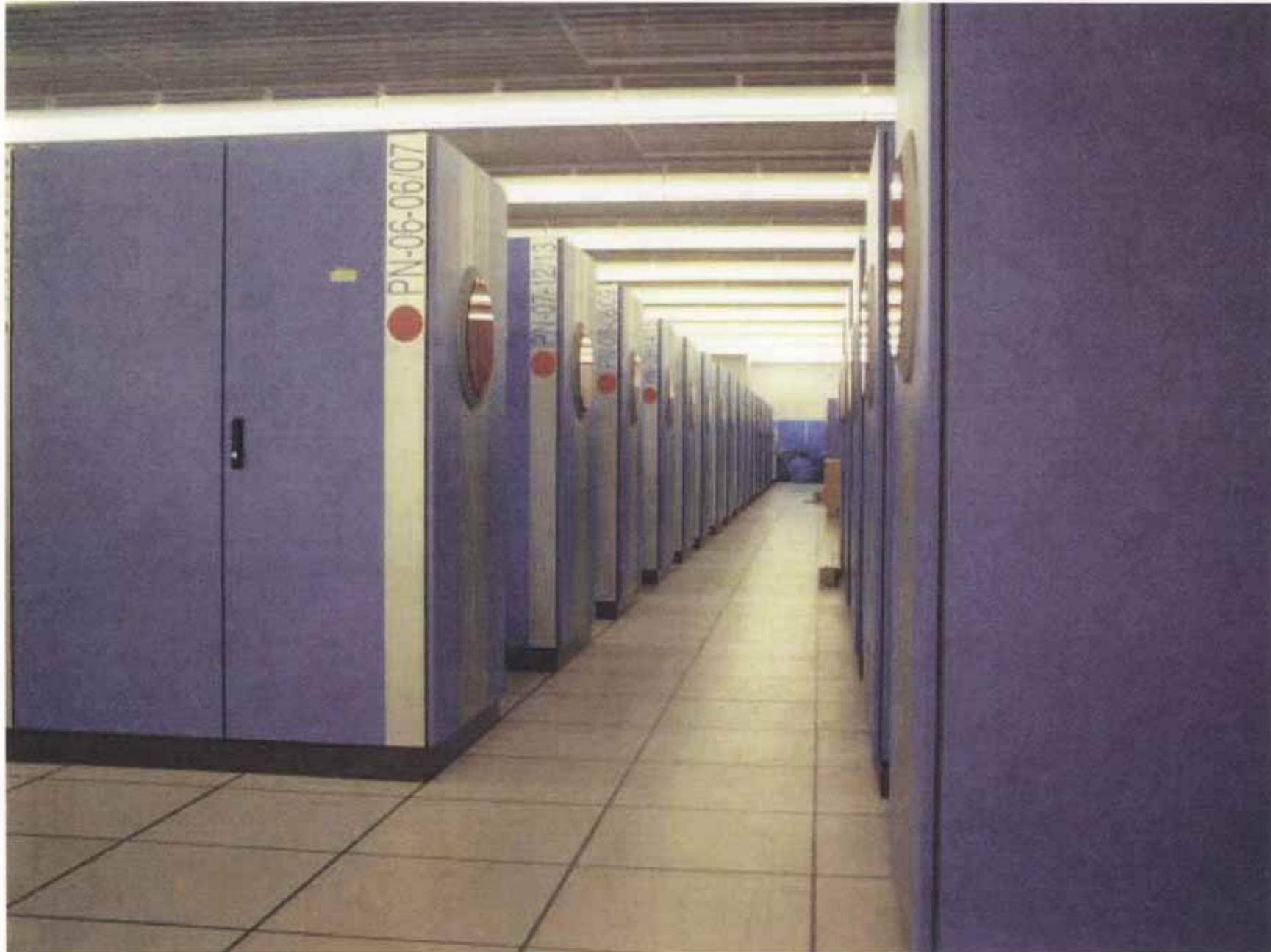

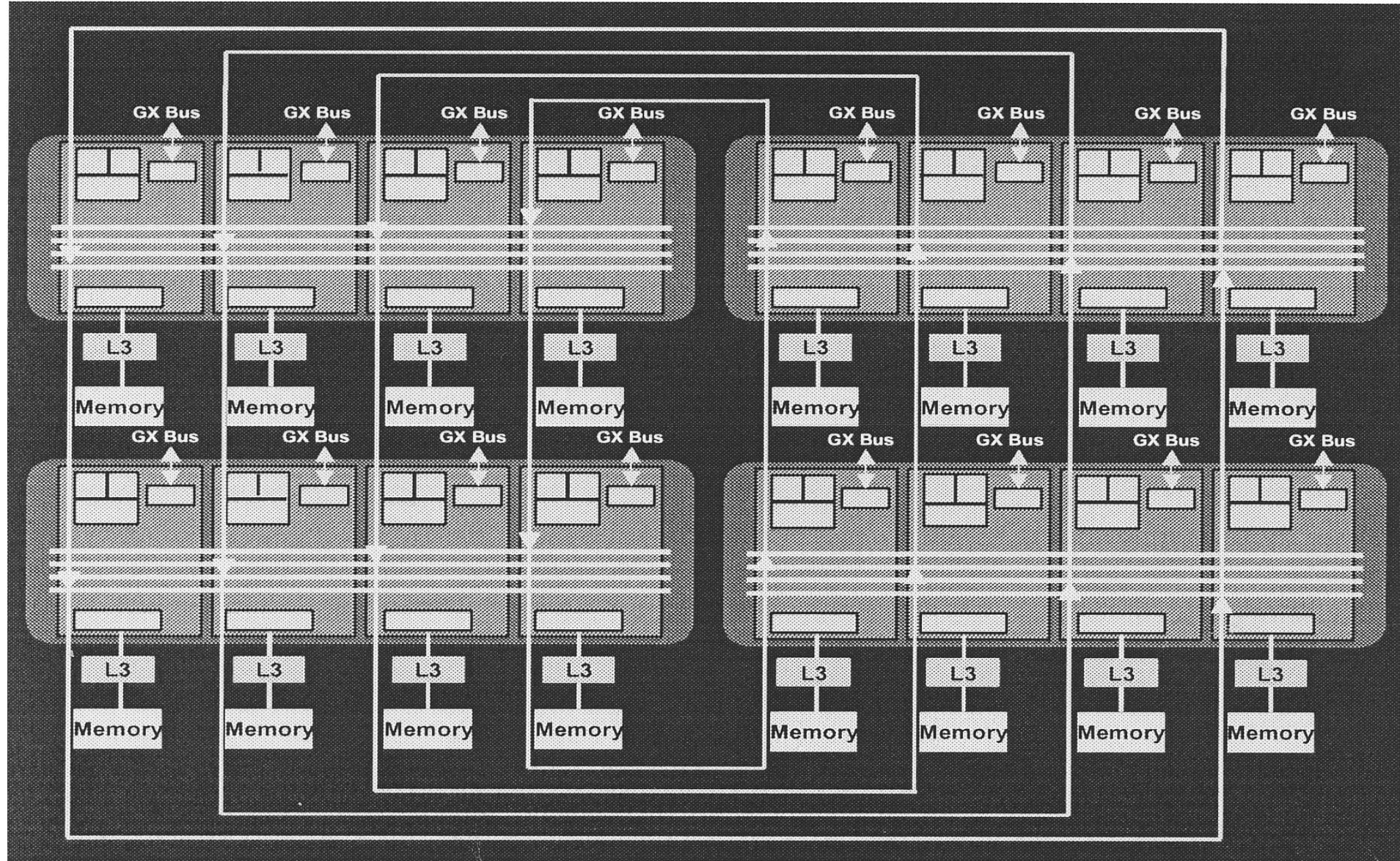

# 地球シミュレータの全体構成

- ・ 総計算ノード数: 640

- ・ ピーク性能: 40TFLOPS

- ・ 主記憶容量: 10TB

- ・ 総プロセッサ数 : 5120

- ・ 計算プロセッサのピーク性能: 8GFLOPS

- ・ 計算ノードのピーク性能: 64GFLOPS

- ・ 計算ノードの主記憶容量: 16GB

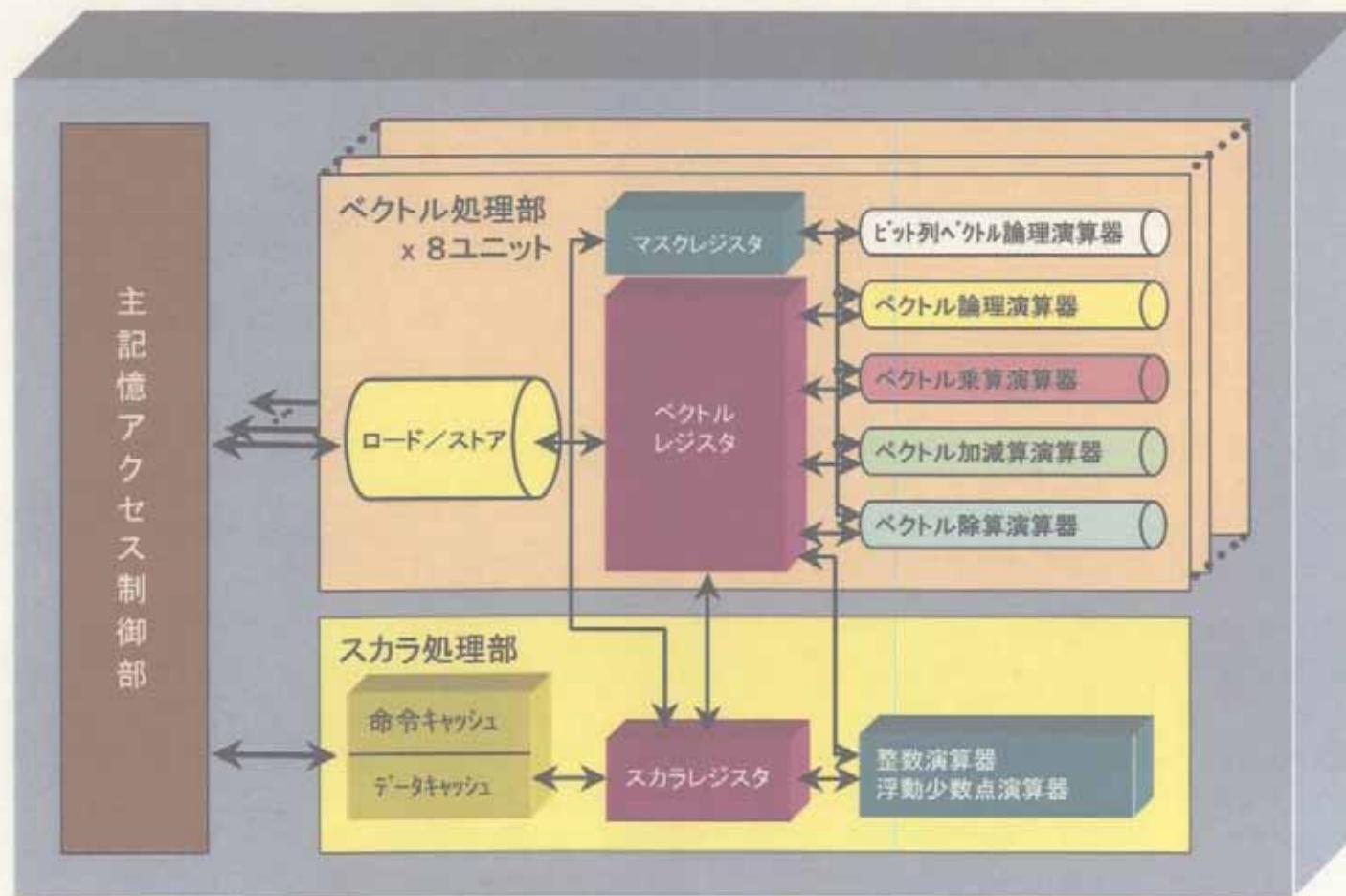

# 計算プロセッサ(AP)の構成

## ○ ベクトルユニット: 8セット

- ◆ 6種のベクトルパイプライン

- ◆ 256要素のベクトルレジスタ: 72個

- ◆ 256ビットのマスクレジスタ: 17個

## ○ 主記憶アクセス制御部

## ○ スカラユニット

- ◆ 4-ウェイ スーパースカラ

- ◆ 64KB 命令キャッシュ

- ◆ 64KB データキャッシュ

- ◆ 128個の汎用レジスタ

1チップLSI: 8Gflop

- ◆ 0.15μm CMOSテクノロジー + 銅配線

- ◆ 20.79mm × 20.79mm

- ◆ 5,700万トランジスタ

- ◆ 5185 ピン

- ◆ クロック周波数

500MHz(1GHz)

- ◆ 消費電力

135W(Typ.)

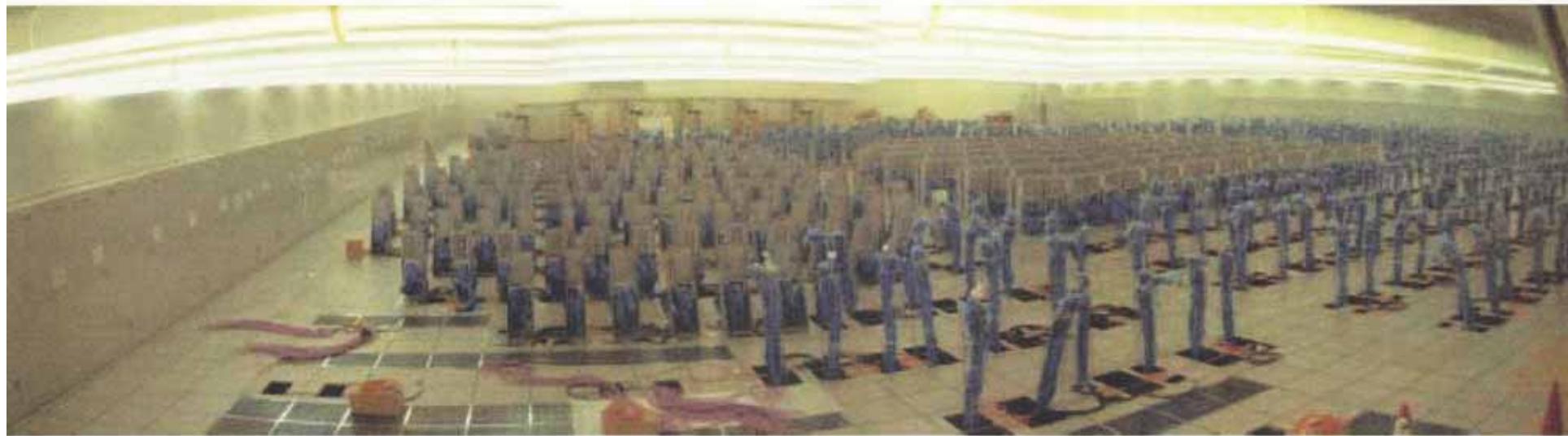

## 計算ノード(PN)の構成

ESRDC@JAERI

全体で 2048 バンク、24 nsec/バンク

## 「地球シミュレータ」とは、どんなコンピュータか

8台のスーパーコンピュータからなる計算ノードを、高速のネットワークで

640台つないだものです。

(総計5120個のスーパーコンピュータから構成)

完成時には世界最速のコンピュータになると予想されます。

平成14年3月からの利用開始を目指して開発中です。

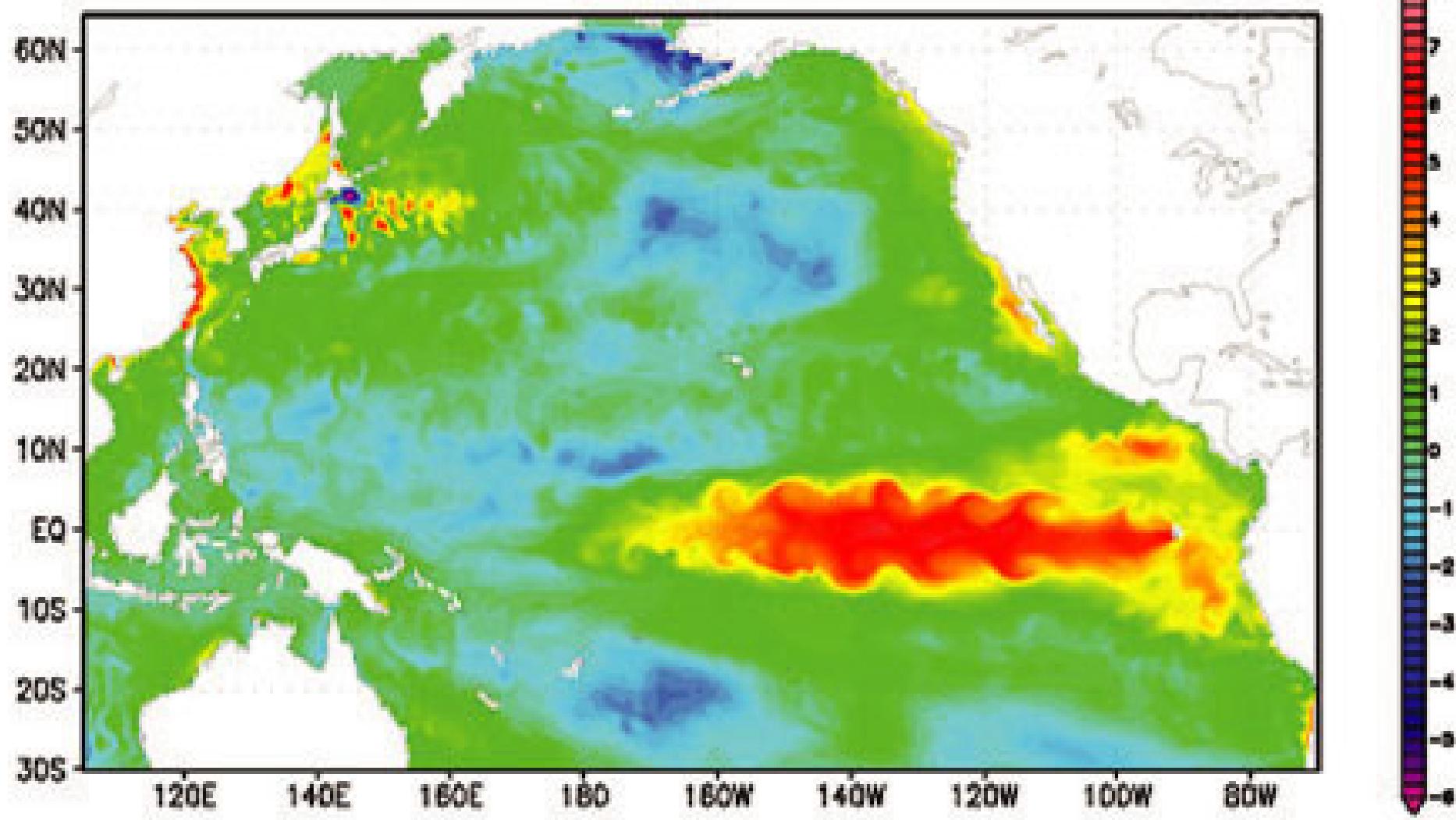

# 地球を10km四方に分割

SST diff. between Dec/27/1997 and Dec/30/1984

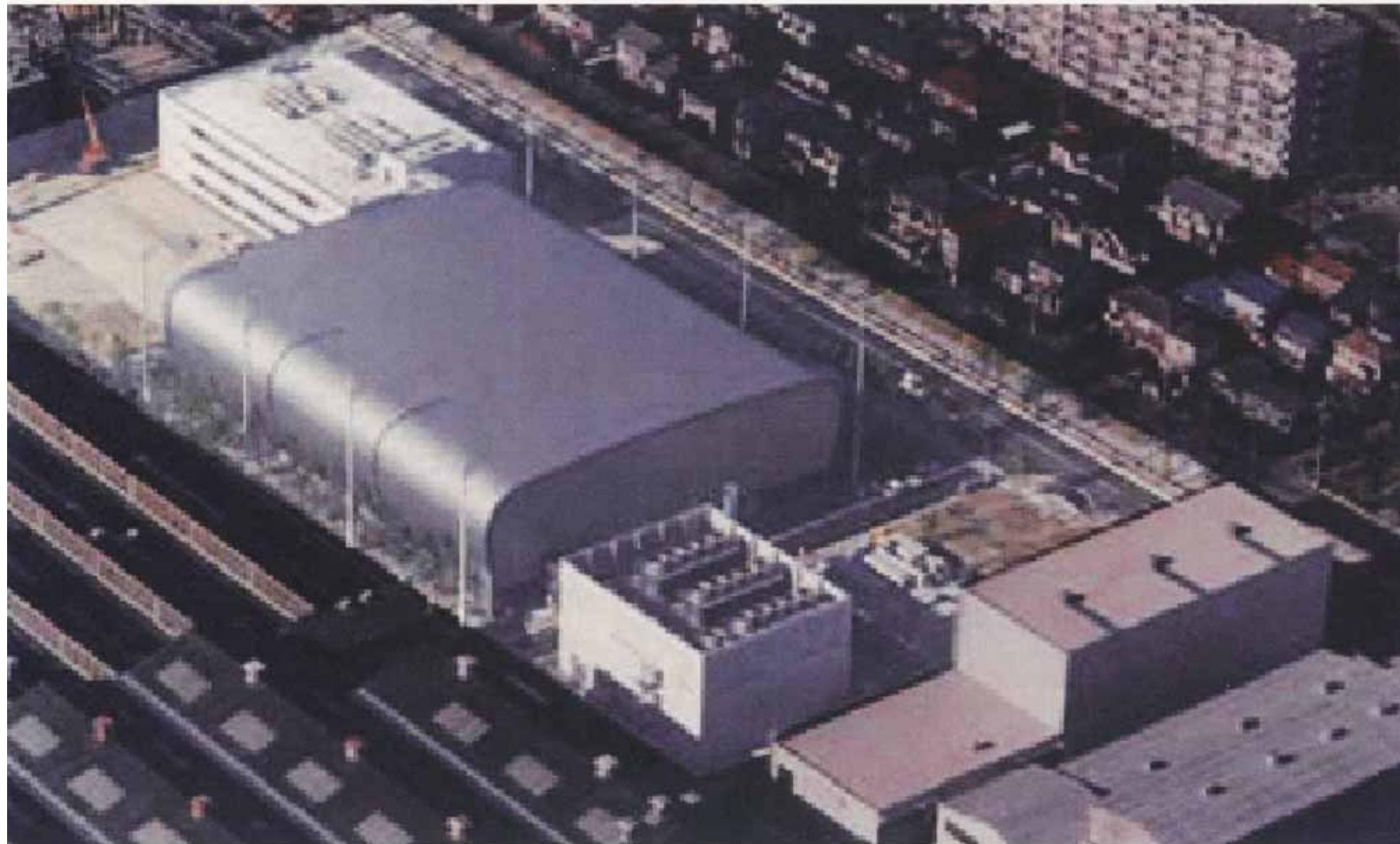

## 地球シミュレータ施設(航空写真)

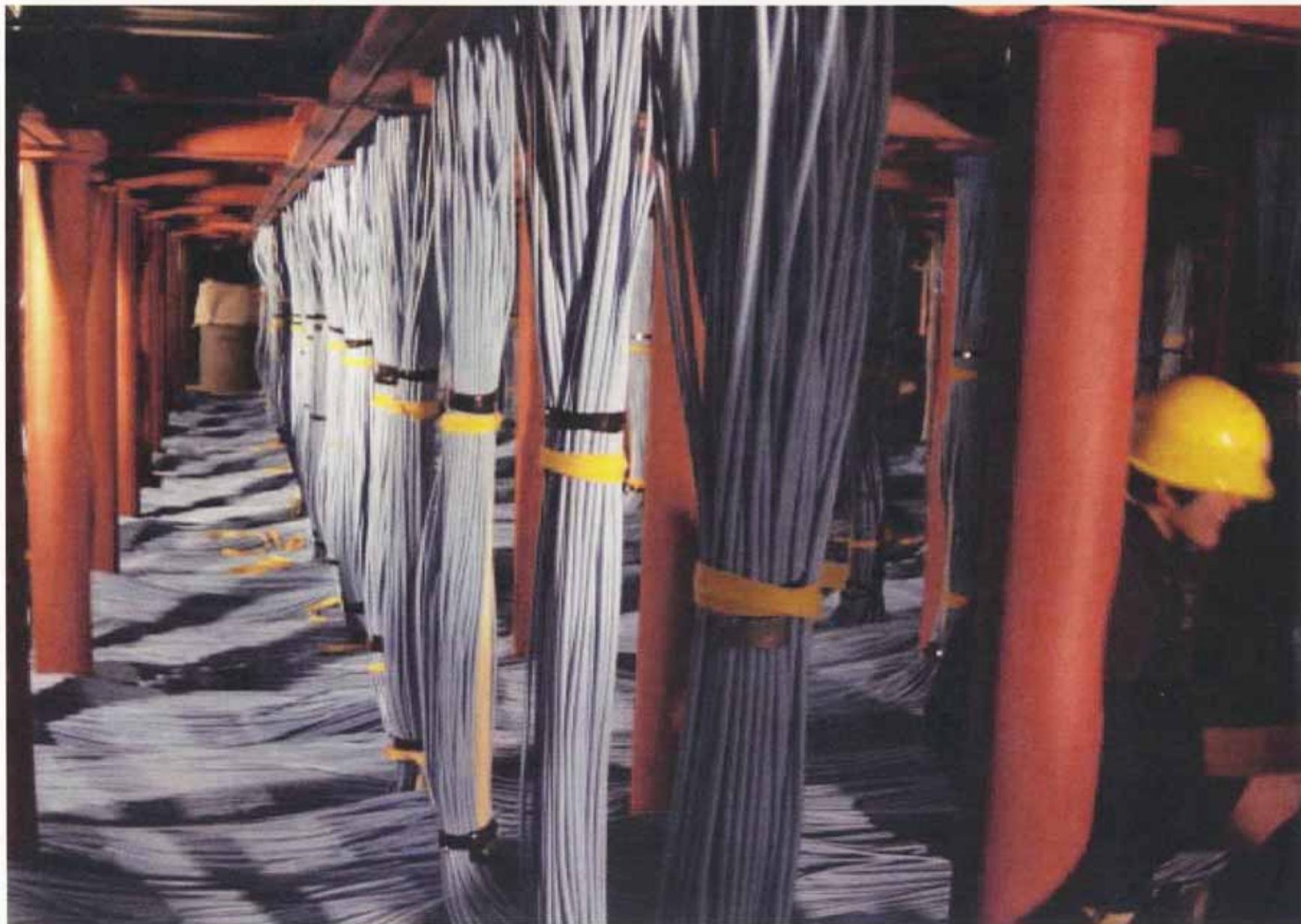

## 計算ノード・結合ネットワーク間ケーブル敷設作業 (平成13年2月～平成13年5月)

計算ノード・結合ネットワーク間ケーブル敷設完了

(平成13年5月)

## 地球シミュレータ 設置完了（平成14年1月）

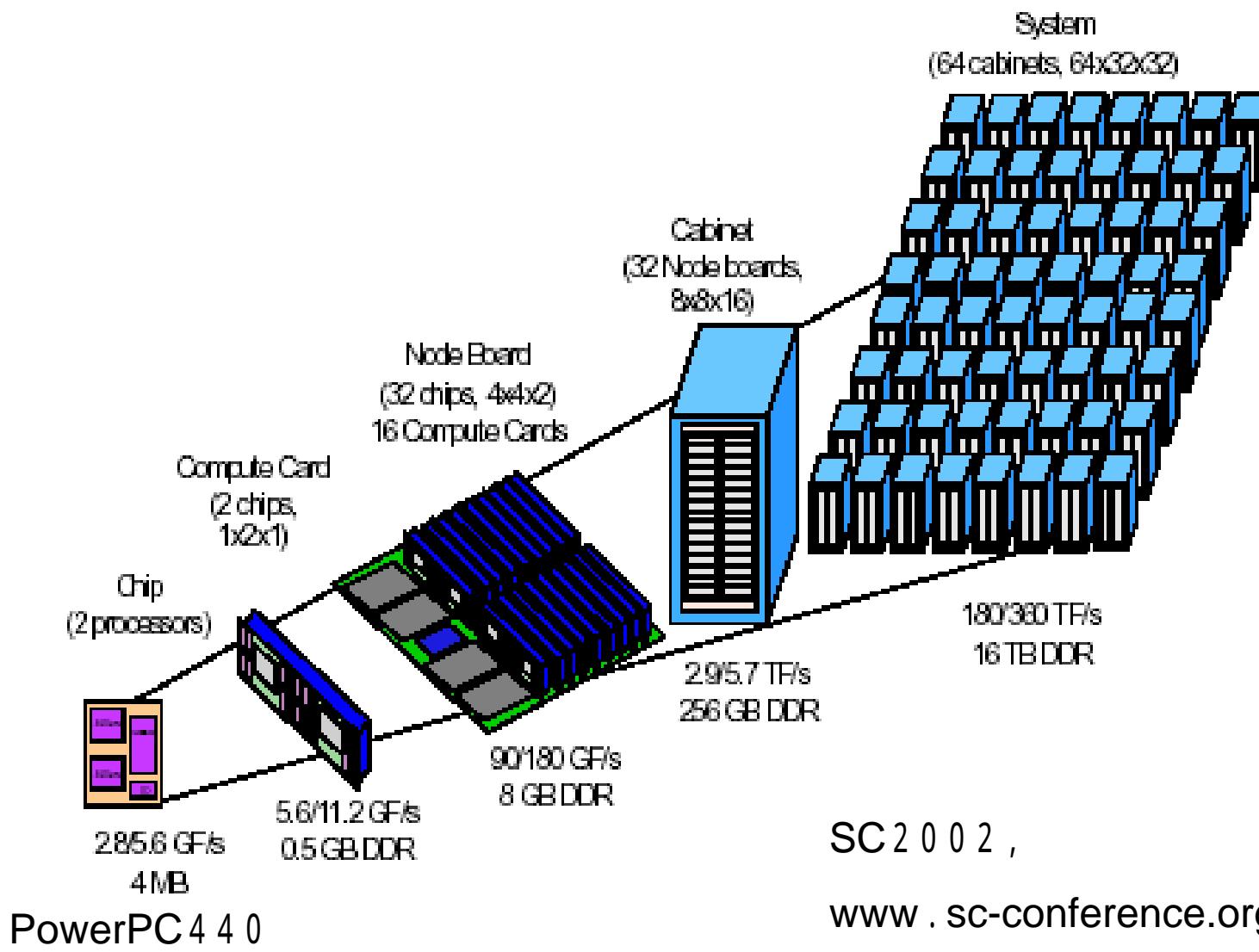

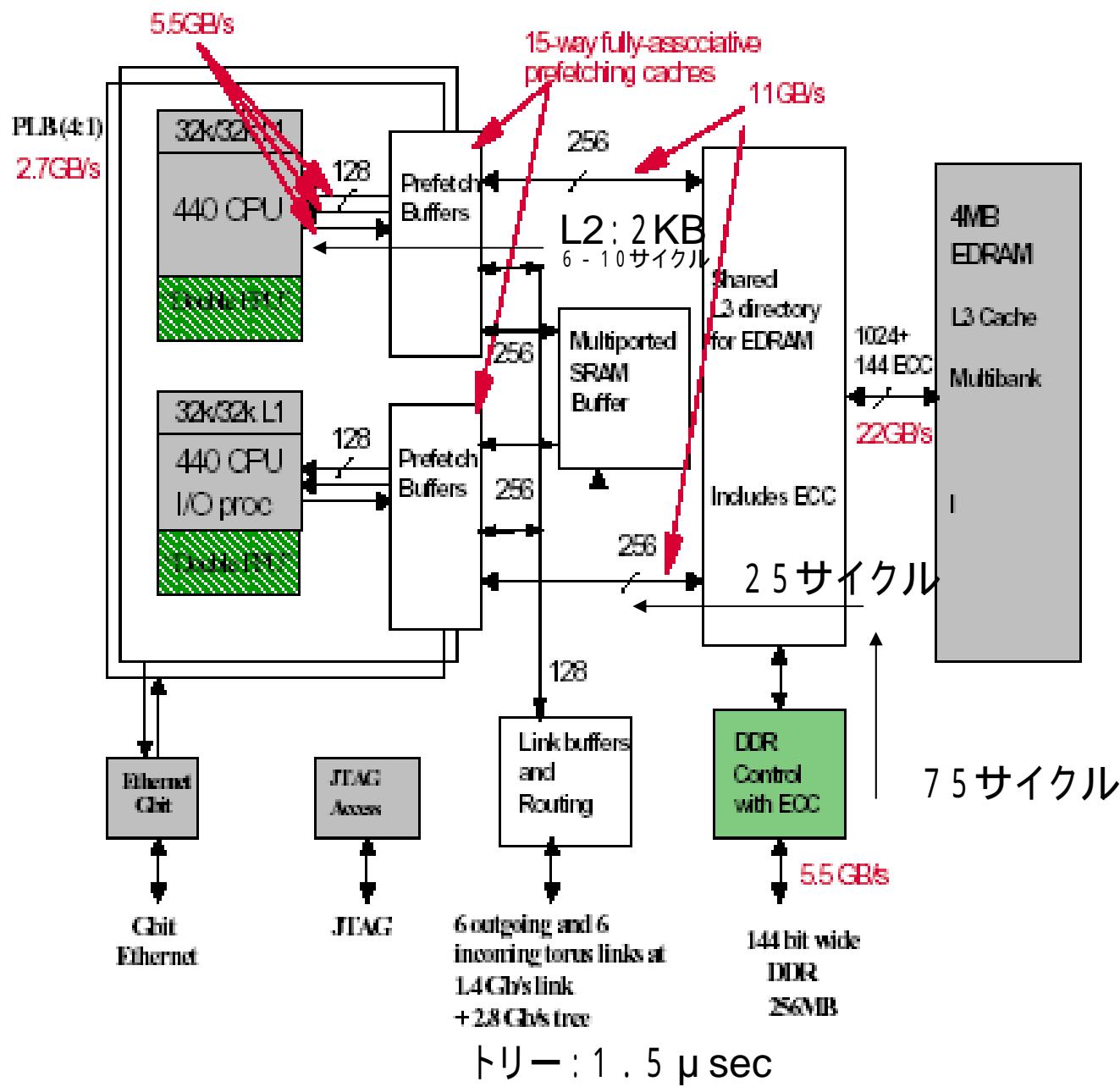

## 7.6.4 BlueGene/L : IBM

- ・2005年稼動予定

- ・65,536プロセッサ

- ・360 TFLOPS

- ・メッセージパッシング

- ・3D-トーラス:  $64 \times 32 \times 32$

適応ルーティング, 仮想チャネル4本

- ・ブロードキャスト, リダクション: トリー

表 2.5 ASCI プラットフォームの概要

| 名称     | Red                                    | Blue Pacific                           | Blue Mountain                          | White                                   | T30         |

|--------|----------------------------------------|----------------------------------------|----------------------------------------|-----------------------------------------|-------------|

| 設置研究所  | Sandia                                 | Lawrence Livermore                     | Los Alamos                             | Lawrence Livermore                      | Los Alamos  |

| メーカー   | Intel                                  | IBM                                    | SGI                                    | IBM                                     | 未定          |

| 使用 MPU | 9,536×Pentium II<br>Xeon               | 5,856×Power PC                         | Origin2000<br>MIPS R10000              | 8,192×Power 3-II                        | 未定          |

| 目標性能   | 1.8Tflops<br>メモリ 606GB<br>Disk 容量 40TB | 3.1Tflops<br>メモリ 2.6TB<br>Disk 容量 75TB | 3.1Tflops<br>メモリ 2.5TB<br>Disk 容量 75TB | 10.2Tflops<br>メモリ 2.5TB<br>Disk 容量 75TB | 30 + Tflops |

| 実績     | 3.2Tflops<br>('99/10月)                 | 3.9Tflops<br>('98/10月)                 | 3.1Tflops<br>('98年)                    | — — —                                   | — — —       |

(注意) 性能はピーク性能値である。

# 日米 スパコン計算 最速でしのぎ 用途拡大で躍起

**毎秒35兆回→360兆回…1000兆回へ**

科学技術計算に利用されるスーパーコンピューター（スパコン）で、日米間の世界最速争いに拍車が掛かっている。スパコンはヒトのゲノム（全遺伝情報）を活用した医薬研究などに用途が広がってきた上、国防上も重要な役割を果たすためだ。最速マシンを日本製に奪われた米国側がナンバーワン奪回へ躍起になっている。

「日本は科学技術計算で新時代を切り開いた」と称賛されるべきだが、米国が新時代に遅れてはならない」。エーブラハム米エネルギー長官は今月10日、ワシントンで講演で世界最速を誇る日本の「地球シミュレータ」（ES）を引き合いにし、最速の座を取り戻すと強調した。

IBM製マシンの毎秒七・三五六兆回だっただけに、「衝撃的な数字」（ニューヨーク・タイムズ紙）だ。米国の科学者らが今月中旬にまとめた最新のスループット上位五百機リストでも、ESは登場以来の首位を堅持、二位の米ヒューレット・パッカード製マシンの三倍近い能力となっている。ただ、IBMは遺伝子からつくられる、たんぱく質の構造解析などに利するため、毎秒一〇〇

兆回規模の計算能力を備えたスパコン開発計画を一九九九年から推進中。〇二年には計画の一環として、米エネルギー省と共同で「ブルー・ジーン青い遺伝子／L」と呼ぶスパコン開発打ち出している。目標とする力は毎秒三百六十兆回。

既に小型試作機が完成し、IBMは最新ランキン

グで試作機が七十三位に入つたとアピール。〇

五年の完成時にはトップ

になる」と首位奪還を予告している。

SC 2 0 0 2 ,

[www.sc-conference.org/sc2002/](http://www.sc-conference.org/sc2002/)

2コア、内1つは

通常通信に使用

Figure 1: BlueGene/L packaging.

Figure 3: BlueGene/L node diagram. The bandwidths listed are targets.

## 7.6.5 京(けい)速コンピュータ

地球シミュレータの250倍の性能: 10 PFLOPS

プロセッサはどうする

ネットワークはどうする

省電力はどうする

使いやすいソフトウェアはどうする

アプリケーションはどうする

## 「最先端・高性能汎用スーパーコンピュータの開発利用」 プロジェクトの実現に向けて（案）

文部科学省研究振興局2005年10月26日発表

開発主体：理化学研究所

平成18年度-平成22年度

1154億円(平成18年度40億円)

米国：2009年1PFLOPSコンピュータ開発予定

科学新聞2005年11月4日

平成17年8月10日

文部科学省研究振興局

文部科学省ホーム

ページより

# 最先端・高性能汎用スーパーコンピュータの開発利用(案)

**目的:** 世界最先端・最高性能のスーパーコンピュータ「汎用京速計算機」システムの開発・整備及び利用技術の開発・普及

**趣旨及び効果:** 理論、実験と並び、現代の科学技術の方法として確固たる地位を築きつつあるスーパーコンピューティング(シミュレーション(数値計算)やデータマイニング、解析等)について、今後とも我が国が世界をリードし続けるため、

- (1)スーパーコンピュータを最大限利活用するためのソフトウェア等の開発・普及

- (2)世界最先端・最高性能の汎用京速<sup>(注)</sup>計算機システムの開発・整備 (注)京速=10ペタFLOPS

- (3)上記(2)を中心とする世界最高水準のスーパーコンピューティング研究教育拠点(COE)「先端計算科学技術センター(仮称)」の形成により研究水準向上と世界をリードする創造的人材の育成を総合的に推進。

世界最高性能の科学技術計算環境を実現し、複雑で多様な現象の系全体のシミュレーションや高度なデータマイニング、解析等を、幅広い分野で行い、「知的ものつくり」や「科学的未来設計」を実問題で可能とし、先端的スーパーコンピューティングにおける国際的なリーダーシップを確立。科学技術・学術や産業の競争力強化、安全・安心な社会の構築に貢献。

また、世界の英知を結集し、世界水準の人材育成を行い、シミュレーションにおける我が国の国際的な地位を確立する。

**概要:** 平成18年度は、世界最先端・最高性能の汎用京速計算機システムの開発・整備の前提であるシステム全般の設計・研究開発等に着手する。

1. ソフトウェア(OS、ミドルウェア、アプリケーションソフトウェア)等の設計・研究開発

2. ハードウェア(計算機システム及び超高速インターフェクション)の設計・研究開発

3. 「先端計算科学技術センター(仮称)」の形成に関する調査研究

**体制:** 国の責任で設備の整備から運用まで一体的に推進する。また装置の開発・運用を行うに当り、产学研官の様々な組織から最も適したところを選択し、そのポテンシャルを活用する。

**事業期間:** 平成18年度～24年度

科学技術・学術の発展と産業競争力強化に貢献

(以下を例に、様々な科学技術・学術・産業分野を対象)

# 広汎な分野での利活用

- 次世代スパコンが拓く世界 -

ものづくり

自動車開発

提供: 日産自動車(株)

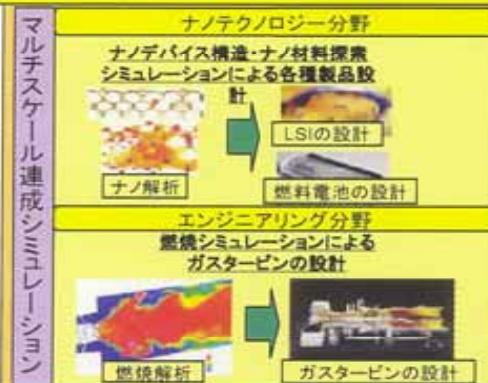

ナノテクノロジー

物質設計 触媒設計

防災

津波被害予測

雲の解析

提供: 気象研究所

原子力

原子炉

丸ごと解析

提供: 日本原子力研究所

提供: 日本原子力研究所

航空・宇宙

ロケット

エンジン設計

提供: (独)宇宙航空研究開発機構

航空機開発

提供: (独)宇宙航空研究開発機構

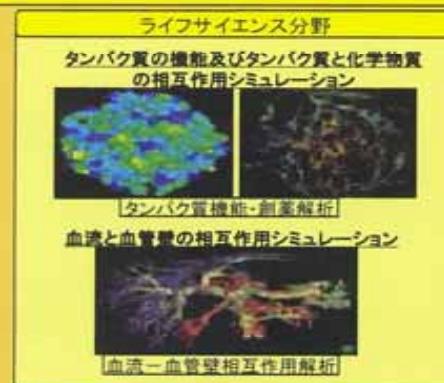

ライフサイエンス

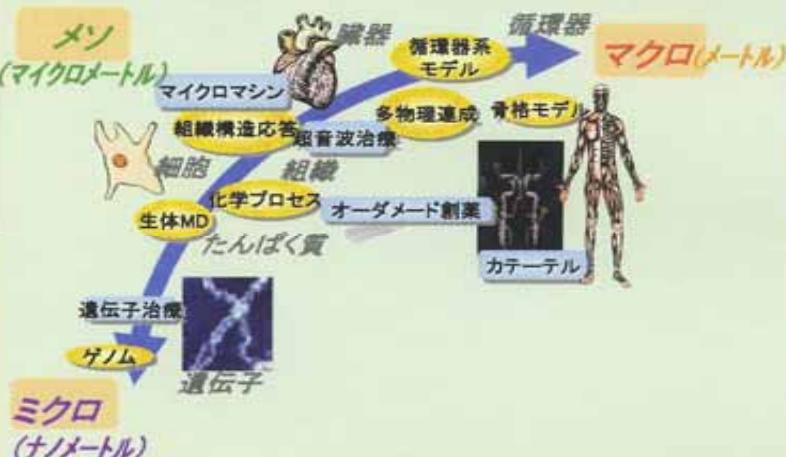

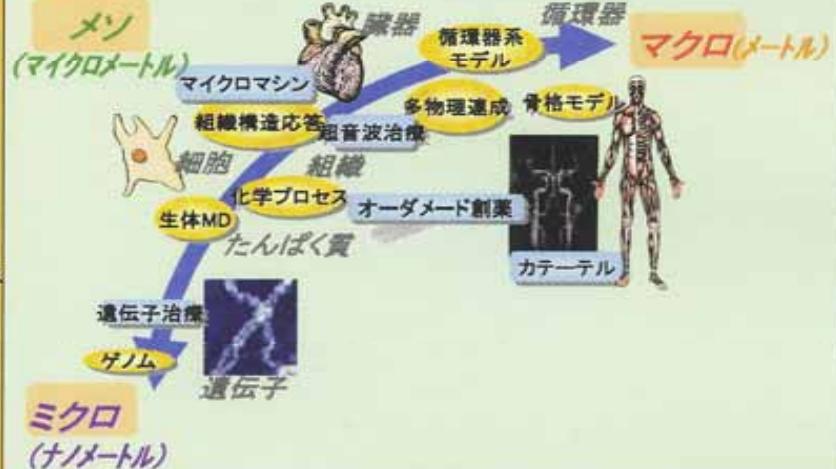

テラーメイド医療

が可能となる

マイクロマシン

細胞

細胞

化学プロセス

組織構造化

多物理連成

組織構造化

分子

蛋白質

生MDP

遺伝子治療

遺伝子

人間丸ごと解析

創薬解析

先端計算科学

技術センター

(仮称)

地球環境

エルニーニョ

現象の影響

予測

提供: (独)海洋研究開発機構

天文・宇宙物理

銀河形成解明 惑星形成解

提供: (独)理化学研究所

提供: 国立天文台

オーロラ

発生解明

提供: (独)海洋研究開発機構

# 汎用京速計算機が目指すグランドチャレンジ（例）

世界最高水準の科学技術創造立国を実現するため、国際競争力を支える新産業創造等の政策目標の実現をも視野に入れ、ナノテクノロジー／ライフサイエンス分野を革新する汎用京速計算機のグランドチャレンジを明示して戦略的に研究開発を進める。

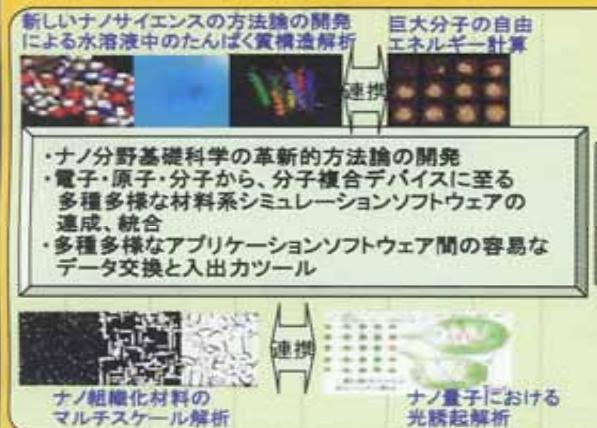

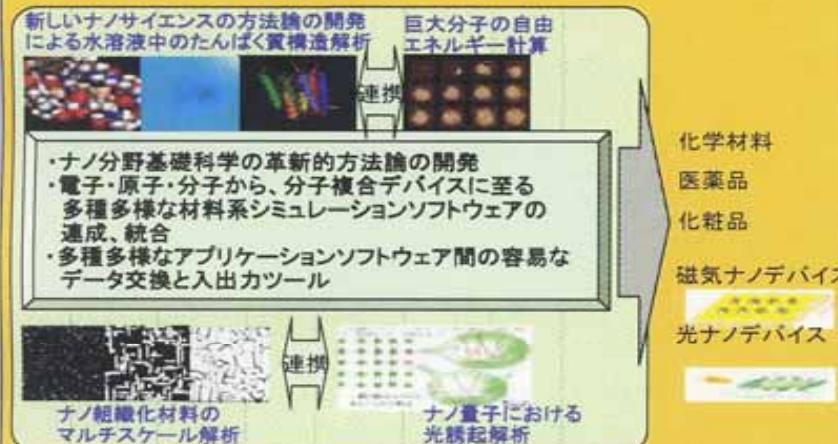

## <ナノテクノロジー分野アプリケーション>

### 次世代ナノ統合シミュレーション

電子・原子・分子から、ナノスケールの分子複合デバイスに至るまで、ナノ材料を丸ごと解析することにより、次世代ナノ材料（新半導体材料等）の創出などの実現を目指す。

## <ライフサイエンス分野アプリケーション>

### 次世代生命体統合シミュレーション

遺伝子から全身の血流まで、人体丸ごと解析することにより、

テーラーメード医療や創薬などの実現を目指す。

# 研究開発スケジュール（案）

| 年度     | 平成17年度                                        | 平成18年度                               | 平成19年度               | 平成20年度                | 平成21年度        | 平成22年度                    | 平成23年度 | 平成24年度                             |

|--------|-----------------------------------------------|--------------------------------------|----------------------|-----------------------|---------------|---------------------------|--------|------------------------------------|

| 開発項目   | 評価等<br>研究開発チーム発足                              | ★<br>(設計仕様、開発体制、立地・運用方針等)            |                      |                       |               | 研究開発状況評価★<br>(システム性能・機能等) |        | COE形成、運用評価★<br>(利用状況、研究成果、人材育成状況等) |

| ソフトウェア | システムソフトウェア                                    | NAREGI <sup>(※4)</sup><br>(平成15年度より) | 異機種統合ソフトウェア設計・製作     |                       | 異機種統合ソフトウェア評価 |                           |        |                                    |

|        |                                               |                                      | グリッドミドルウェア設計・製作      |                       | グリッドミドルウェア評価  |                           |        |                                    |

|        | グランドチャレンジアプリケーション                             | (※4)                                 | 次世代ナノ統合シミュレーション設計・製作 | 次世代ナノ統合シミュレーション評価     |               |                           |        |                                    |

|        |                                               |                                      |                      | 次世代生命体統合シミュレーション設計・製作 |               | 次世代生命体統合シミュレーション評価        |        |                                    |

| ハードウェア | 革新的シミュレーションソフトウェアの研究開発 <sup>(※1)</sup>        |                                      |                      |                       | 革新アプリケーション評価  |                           |        |                                    |

|        | 次世代高精度・高分解能シミュレーション技術の開発 <sup>(※2)</sup>      |                                      |                      |                       |               |                           |        |                                    |

|        | 将来のスーパーコンピューティングのための要素技術の研究開発 <sup>(※1)</sup> |                                      |                      |                       |               |                           |        |                                    |

|        | 通信・演算情報量の爆発的増大に備える超低消費電力技術の創出 <sup>(※2)</sup> |                                      |                      |                       |               |                           |        |                                    |

| その他    | 大規模処理計算機部                                     |                                      | 設計                   | 実装技術設計・評価             | 製作            | システム強化                    |        |                                    |

|        | 逐次処理計算機部                                      |                                      | 設計                   | 実装技術設計・評価             | 製作            | システム強化                    |        |                                    |

|        | 特定処理計算加速部                                     |                                      | 設計                   | 実装技術設計・評価             | 製作            |                           |        |                                    |

|        | 異機種間接続超高速インターフェクション                           |                                      | 設計                   | 実装技術設計・評価             | 製作            |                           |        |                                    |

|        | 遠隔可視化装置                                       |                                      |                      | 実装設計・評価               | 製作            |                           |        |                                    |

| その他    | ファイルシステム                                      |                                      |                      | 設計                    | 製作            | システム強化                    |        |                                    |

|        | 立地調査、建屋建設、付帯設備整備等                             |                                      | 検討                   | 設計                    | 建設            | 付帯設備整備                    |        |                                    |

■ 「最先端・高性能汎用スーパーコンピュータの開発利用」以外のプロジェクトを示す。 ■ プロジェクト部分に該当。

※1:「次世代IT基盤構築のための研究開発」の研究開発領域の一つ。

※2:科学技術振興機構「戦略的創造研究推進事業」の一戦略目標下の研究領域として、「情報システムの超低消費電力化を目指した技術革新と統合化技術」を設定。

※3:科学技術振興機構「戦略的創造研究推進事業」の一戦略目標下の研究領域として、「マルチスケール・マルチフィジックス現象の統合シミュレーション」を設定。

※4:「超高速コンピュータ網形成プロジェクト(National Research Grid Initiative)」。平成15年度よりグリッドミドルウェアとナノシミュレーションソフトウェアの開発を進めている。

# 汎用京速計算機のソフトウェア開発

## システムソフトウェア<sup>(※1)</sup>

各地に散在する実験装置、データベース、⇒膨大なデータの効率的利用のため、スパコンを自在にどこからでも利用可能。スパコンの性能を最大限活用。

グリッドミドルウェア<sup>(※2)</sup>

(遠隔利用と外部資源接続支援)

平成15~22年度

異機種統合ソフトウェア

平成18~22年度

超巨大データベース

## グランドチャレンジアプリケーション

次世代ナノ統合シミュレーション: 平成15~22年度

ナノ新材料・新機能(新半導体材料等)を創出するなど最先端の知的のづくりを実現するため、ナノ材料系全体統合シミュレーション基盤ソフトウェアの研究開発を行う。NAREGIの成果をベースに開発を行う。

化学材料

医薬品

化粧品

磁気ナノデバイス

光ナノデバイス

## 汎用京速計算機の研究開発体制

平成17年度後半に利用分野毎の専門家チームを発足予定

※1 ハードウェアを直接制御したり、システム使用者を支援するソフトウェア

※2:「超高速コンピュータ網形成プロジェクト(National Research Grid Initiative; NAREGI)」。平成15年度よりグリッドミドルウェアとナノシミュレーションソフトウェアの開発を進めています。

\*3:Nuclear Magnetic Resonance(核磁気共鳴)。物質の構造を同定するのに用いる装置。

\*4:兵庫県播磨科学公園都市にある第三世代の大型放射光施設

次世代生命体統合シミュレーション: 平成18~24年度

テラーメード医療・創薬などを実現するため、遺伝子レベルから細胞、循環器、人体スケールの個々の要素から全体に至るまで人間系を最適に解析可能な総合シミュレーション基盤ソフトウェアの研究開発を行う。

## グランドチャレンジアプリケーション

### 次世代ナノ統合シミュレーション: 平成15~22年度

ナノ新材料・新機能(新半導体材料等)を創出するなど最先端の知的ものづくりを実現するため、ナノ材料系全体統合シミュレーション基盤ソフトウェアの研究開発を行う。NAREGIの成果をベースに開発を行う。

### 次世代生命体統合シミュレーション: 平成18~24年度

テーラーメード医療・創薬などを実現するため、遺伝子レベルから細胞、循環器、人体スケールの個々の要素から全体に至るまで人間系を最適に解析可能な統合シミュレーション基盤ソフトウェアの研究開発を行う。

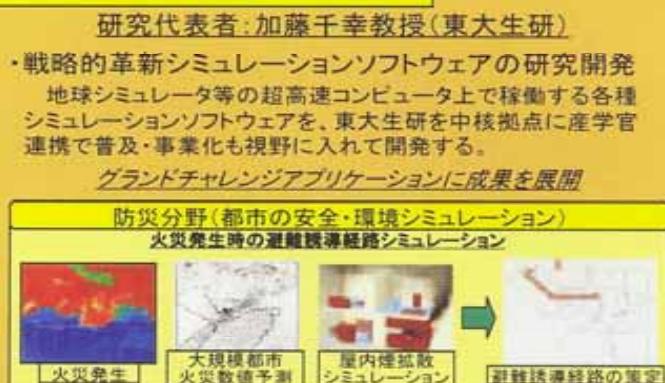

### 革新的シミュレーションソフトウェアの研究開発<sup>(※)</sup>: 平成17年度～平成19年度

※「次世代IT基盤構築のための研究開発」の研究開発領域の一つ。

### 次世代高精度・高分解能シミュレーション技術の開発<sup>(※)</sup>: 平成17年度～平成23年度

複数の現象が相互に影響しあうようなマルチスケール・マルチフィジックス現象のシミュレーションを実現する効率的な計算手順を確立し、複雑な工業製品の設計・試作などの先端シミュレーション技術を、我が国最先端のコンピューティング環境を駆使して開発することを目的とした研究。

現在、研究課題を選定中。(8月中旬に決定予定)

※科学技術振興機構「戦略的創造研究推進事業」の一戦略目標下に研究領域として、「マルチスケール・マルチフィジックス現象の統合シミュレーション」を設定。

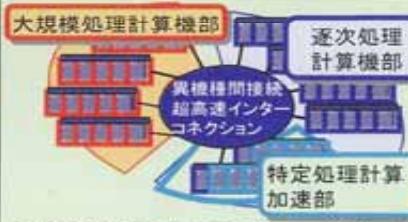

# 汎用京速計算機のハードウェア開発

## 要素技術開発

### 将来のスーパーコンピューティングのための要素技術の研究開発<sup>(※)</sup> : 平成17~19年度

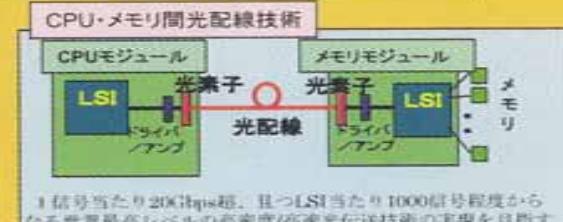

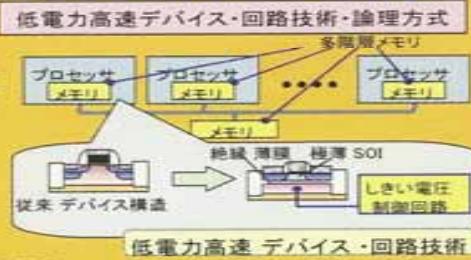

- ①システムインターネット技術

(九大、富士通)

- ②内部結合網IP化による実行効率最適化方式

(東大、慶大、アラクサラネットワークス)

- ③低電力高速デバイス・回路技術・論理方式

(日立製作所、東大、筑波大)

- ④CPU・メモリ間光配線技術

(日本電気、東工大)

※「次世代IT基盤構築のための研究開発」の研究開発領域の一つ。

### 通信・演算情報量の爆発的増大に備える超低消費電力技術の創出<sup>(※)</sup> : 平成17~23年度

消費電力あたりの処理性能を100倍から1000倍にする超低消費電力技術の確立を

目指すための基礎研究。現在、研究課題を選定中。(8月中旬に決定予定)

※:科学技術振興機構「戦略的創造研究推進事業」の一戦略目標下の研究領域として、「情報システムの超低消費電力化を目指した技術革新と統合化技術」を設定。

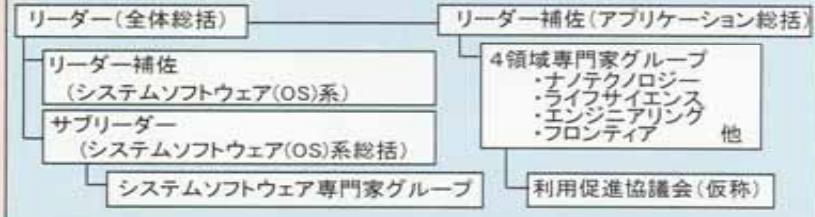

## 汎用京速計算機の研究開発体制

平成17年度後半にプロジェクトを推進するための専門家チームを発足予定

### リーダー(全体総括)

- リーダー補佐(ハードウェア・ネットワーク系)

- サブリーダー(ハードウェア・ネットワーク系総括)

- ハードウェア・ネットワーク専門家グループ

### 要素技術開発状況

### 要素技術開発成果

### 設計: 平成18~19年度

利用分野チームの要求調査

利用分野での性能要求を調査し

整理する。

ハードウェア仕様検討

利用分野からの性能要求調査、性能見

積もり、要素技術開発状況から見た実現

性等を検討し、高性能を実現するための

最適なハードウェア仕様を決定

性能見積もり

利用分野毎のプログラムの性能見積もり行う

## 汎用京速計算機の研究開発体制

平成17年度後半にプロジェクトを推進するための専門家チームを発足予定

リーダー(全体総括)

リーダー補佐(ハードウェア・ネットワーク系)

サブリーダー(ハードウェア・ネットワーク系総括)

ハードウェア・ネットワーク専門家グループ

要素技術

開発状況

要素技術

開発成果

### 設計: 平成18～19年度

利用分野チームの要求調査

利用分野での性能要求を調査し整理する。

#### ハードウェア仕様検討

利用分野からの性能要求調査、性能見積もり、要素技術開発状況から見た実現性等を検討し、高性能を実現するための最適なハードウェア仕様を決定

性能見積もり

利用分野毎のプログラムの性能見積もりを行う

#### ハードウェア仕様

### 実装技術: 平成20～21年度

約3億個の回路

をLSI、プリント

基板などに織り

込む

試作

LSI

プリント

基板

試作機

組立

試作機

評価

試作機を組み上げ、実際のプログラム等を走行させ、システムの安定性を確認

#### 製作開始

### 製作: 平成21～22年度

システム全体の製作

特定処理計算加速部の完成

#### 汎用京速計算機システム

### 性能評価: 平成22年度

Linpack(10ペタFLOPS目標)、

HPC CHALLENGEでの性能評価

### システム強化: 平成23～24年度

大規模処理計算機部と逐次処理計算機部の

システム強化

### 総合評価: 平成23～24年度

グランドチャレンジアプリケーション、「革新的

シミュレーションソフトウェアの研究開発」※等

での実問題を用いた総合評価

※: 研究開発プロジェクト「次世代IT基盤構築のための研究開発」の研究開発領域の一つ。

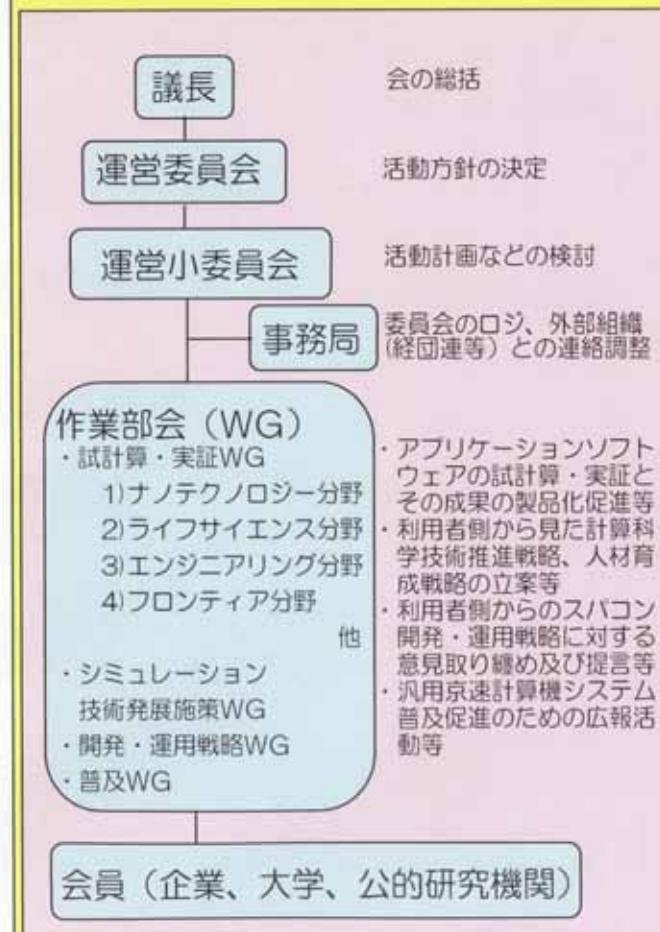

# 汎用京速計算機の利用促進

## 1. ユーザー会（利用促進協議会（仮称））の組織化

### 趣旨

汎用京速計算機を最大限有効に利用するためには、ユーザーにとって利用し易いシステムであることが必須。そのため、平成17年度中に発足予定の開発チームとユーザーの密な情報交換が必要。この双方向の情報交換のために利用促進協議会（仮称）を組織し、汎用京速計算機の利用に関する産業界・学会からの要望を取纏め、開発・運用側に意見具申等を行い、更に普及・利用促進も図る。

なお、本利用促進協議会（仮称）は、既に同様の目的で活動中の計算科学技術関連のユーザー会組織等を統合し、活動を強化する。

利用想定ユーザーとしては、次の3つの目的に当てはまる機関（企業、大学、公的研究機関）である。

### （1）21世紀の基幹産業を支える最先端の知的ものづくりと社会基盤の整備

ナノテクノロジーを駆使した新材料創出、バイオテクノロジーと医用工学の融合による個人差に応じた合理的な医薬品・医療の実現、設計から製品化までの開発期間・開発コストの大幅な縮小や生産性を飛躍的に向上させる製造プロセス－貴シミュレーション、あるいは、電力、ガス等の安定した社会基盤の整備のためのシミュレーションの応用。

### （2）先進的なシミュレーションを駆使した安心・安全な社会の実現

台風や豪雨、地震・津波などの自然災害の正確な予測や都市・地域スケールの災害影響評価を踏まえた、きめ細かな防災対策での施策の立案。

### （3）人類未踏のフロンティア科学技術を探求

ナノサイエンス、ライフサイエンス、環境、原子力、航空・宇宙等の幅広い科学技術のフロンティアを開拓。

参考) 既存のユーザー会組織等

- ・戦略的基盤ソフトウェア産業応用推進協議会（共同議長：小林敏雄自動車技術研究所長、柘植綾夫総合科学技術会議議員）

- ・NAREG I<sup>(※1)</sup>研究グリッド産業応用協議会（会長：中村道治日立製作所副社長）

- ・ITBL<sup>(※2)</sup>共同実施者・共同研究者等

※1：「超高速コンピュータ網形成プロジェクト(National Research Grid Initiative)」。平成15年度よりグリッドミドルウェアとナノシミュレーションソフトウェアの開発を進めている。

※2：IT-Based Laboratory。日本原子力研究所等6つの国内研究機関により平成12年度より開始された、計算資源、データベース等の情報資源を共有することにより仮想研究環境の構築を目指す。

## 2. 利用促進協議会(仮称)の詳細について

### (1) 活動内容

汎用京速計算機システムに対する産業界・学会などの利用者側（企業、大学、公的研究機関）の窓口として、開発・運用側への意見具申、普及・利用推進、情報の共有を図る。

平成17年度中に組織化

### (2) 構成と機能

### (3) 利用促進協議会（仮称）参加予定機関

(平成17年8月時点での想定メンバー125社、33大学、21研究機関)

#### ナノテクノロジー、バイオテクノロジー（食品、化学、医薬品など）分野 35社

旭化成、旭硝子、味の素、出光石油化学、エーザイ、キッセイ薬品工業、キリンビール、杏林製薬、昭和電工、住友化学、住友製薬、ソイジーン、大正製薬、大鵬薬品工業、東レ、日本たばこ産業、日立金属、富士写真フィルム、マンダム、三菱化学 他

#### ものづくり（自動車、電機・情報、ソフトウェアなど）分野 81社

石川島播磨重工業、宇部興産、NEC、川崎重工、原子燃料工業、国際電気通信基礎技術研究所、三洋電機、島津製作所、新日本製鉄、住友重機械工業、住友電装、セイコーエプソン、デンソー、東芝、トヨタ自動車、日揮、日産自動車、日立製作所、富士通、古河電工、本田技研、松下電器産業、松下电工、マツダ、三井造船、三菱重工業、三菱電機、村田製作所、リコー、横河電機 他

#### 社会基盤の整備（建設、電力、ガス、鉄道、電話、金融など）分野 9社

関西電力、清水建設、大成建設、竹中工務店、東京ガス、東京電力、日本電信電話 他

#### 安全、安心な社会の実現とフロンティア科学技術の探求分野

33大学 21公的研究機関

<大学>大阪大、九大、京大、東工大、東大、東北大、名古屋大、北大 他

<公的研究機関など>宇宙航空研究開発機構、海洋研究開発機構、国立医薬品食品衛生研究所、国立環境研究所、国立情報学研究所、産業技術総合研究所、鉄道総合技術研究所、電力中央研究所、日本原子力研究所、物質・材料研究機構、分子科学研究所、防災科学技術研究所、理化学研究所 他

(五十音順)

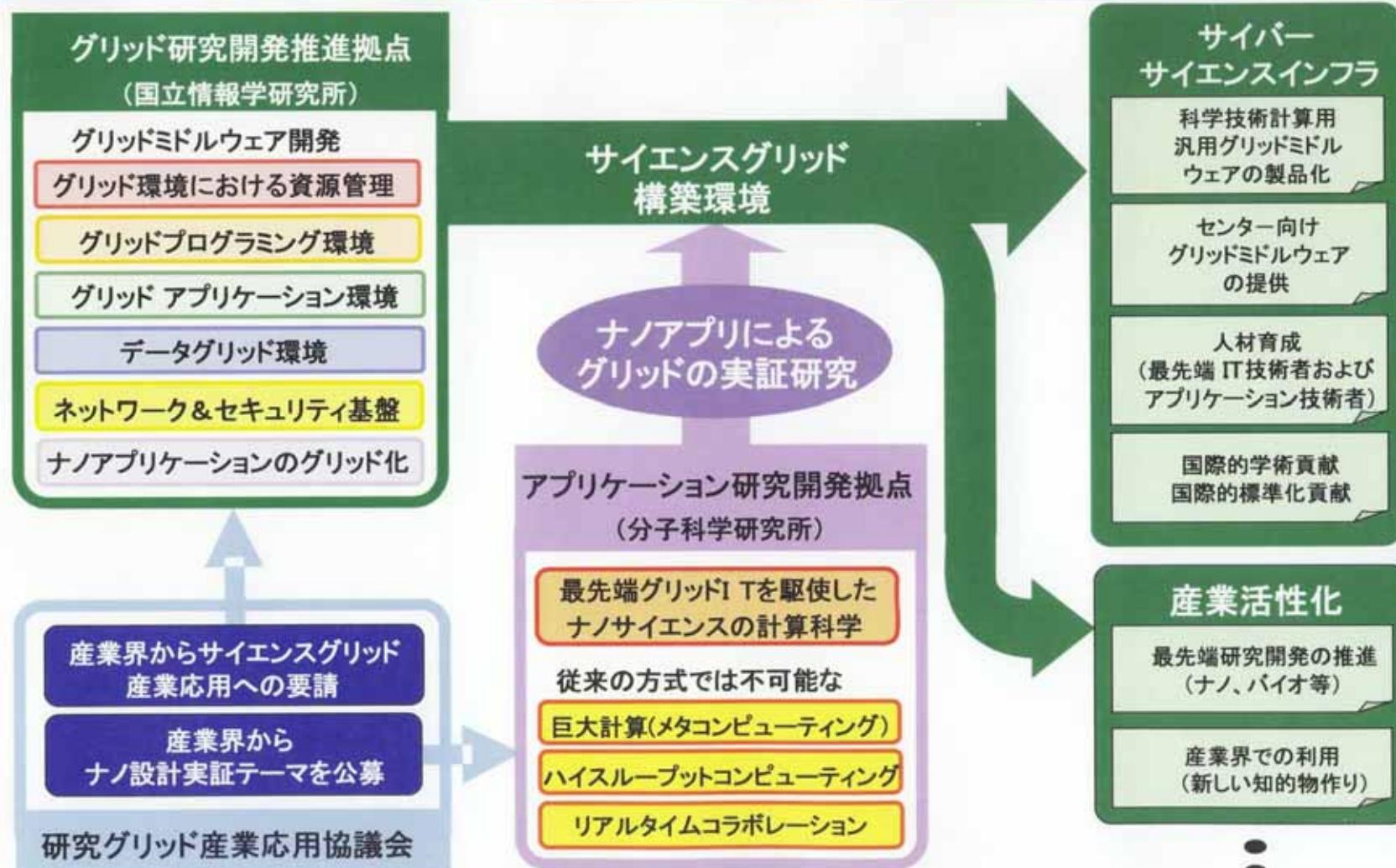

# 7.6.6グリッドコンピューティング

高速グリッドコンピューティング環境を構築する

『超高速コンピュータ網形成プロジェクト(NAR

EGI)』

中間成果報告会

主催：文部科学省

2005年7月11日(月) 9:30~15:00

国立情報学研究所 学術総合センター

# 背景

ナノ材料

高分子

半導体

精密電子機器

…

「知的ものづくり」

複合的なシミュレーションによる次世代の設計手法の確立

多様性を持った一つの高性能・大容量計算資源に見える

分散した異機種計算資源を有機的につなぐ

グリッド

専用シミュレータ

センター A

センター Z

バラバラ

専用機

National Research Grid Initiative

## 達成すべき目標

- ① 学術研究、産業界における研究開発を対象に計算機資源をグリッドで接続し、大規模なシミュレーション、ハイスループット処理、マルチスケール・マルチフィジックスの連成解析が可能な、100Tflops級のサイエンスグリッドを実現するグリッド基盤ソフトウェアを開発。

- ② 開発したグリッド基盤ソフトウェアが実用的に有効であることをナノサイエンス分野での実証研究で確認。

# 研究開発の取り組み方と成果の利用

## 研究開発体制図

# プロジェクト全体の進め方

| 年度                                                                                            | 2003                                                                                    | 2004                                                                                                                 | 2005                                                                                                      | 2006                                                              | 2007                                                                                         | 2008~    |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------|

| フェーズ                                                                                          | 研究開発                                                                                    |                                                                                                                      | 評価                                                                                                        |                                                                   | 高度化・強化                                                                                       |          |

| グリッド研究拠点<br>(国情研究拠点)                                                                          | 統合α版 → 統合β版 → 統合1.0版に向けた高度化 → 統合1.0版配布                                                  |                                                                                                                      |                                                                                                           |                                                                   |                                                                                              |          |

|                                                                                               | <ul style="list-style-type: none"> <li>・仕様決定</li> <li>・要素技術のプロトタイピング</li> </ul>         | 統合α版                                                                                                                 | 統合β版                                                                                                      | 配布                                                                | 統合1.0版に向けた高度化                                                                                | 統合1.0版配布 |

| <b>UNICORE-Globus ベース</b> → <b>OGSA化</b>                                                      |                                                                                         |                                                                                                                      |                                                                                                           |                                                                   |                                                                                              |          |

| システムの実証研究<br>(分子研究拠点)                                                                         | <ul style="list-style-type: none"> <li>・グリッドRPC早期提供</li> </ul>                          | <ul style="list-style-type: none"> <li>・グリッドRPC、グリッドMPI早期公開と分子研への提供</li> </ul>                                       | <ul style="list-style-type: none"> <li>・グリッドRPC、グリッドMPIの導入</li> </ul>                                     | <ul style="list-style-type: none"> <li>・データグリッド(追加テーマ)</li> </ul> | <ul style="list-style-type: none"> <li>・ミドルウェアのOGSA化促進</li> <li>・β版の展開によるグリッド環境強化</li> </ul> | 実証計算     |

|                                                                                               | ナノアプリケーションのグリッド化対応・連成向けツール研究開発                                                          |                                                                                                                      |                                                                                                           |                                                                   |                                                                                              |          |

| インフラ                                                                                          | <ul style="list-style-type: none"> <li>・ソフトウェア/方法論開発</li> </ul>                         | <ul style="list-style-type: none"> <li>・アプリケーションソフトウェアの開発</li> </ul>                                                 | →                                                                                                         |                                                                   | 実証研究                                                                                         |          |

|                                                                                               | <ul style="list-style-type: none"> <li>・産業界公募</li> <li>・α版統合ナノシミュレーションシステム開発</li> </ul> | <ul style="list-style-type: none"> <li>・グリッドRPC、グリッドMPIの導入</li> <li>・大規模実証の分子研システムで実施</li> <li>・産業界公募研究開始</li> </ul> | <ul style="list-style-type: none"> <li>・アプリのグリッド化</li> <li>・産業界公募研究拡大</li> <li>・グリッドナノシミュレータ開発</li> </ul> | <ul style="list-style-type: none"> <li>・β版環境での評価/実証準備</li> </ul>  | <ul style="list-style-type: none"> <li>・V1.0版に向けた環境での評価/実証準備</li> </ul>                      |          |

| 大学・国公立研究機関の技術をスムーズに民間移転できる実用的な仕組み                                                             |                                                                                         |                                                                                                                      |                                                                                                           |                                                                   |                                                                                              |          |

| 両拠点でのシステム導入 → 拠点毎のグリッド環境構築 → α版による拠点間グリッド連携 → β版による拠点間グリッド連携 → 実証計算のための100Tflops級に向けた環境の拡大/整備 |                                                                                         |                                                                                                                      |                                                                                                           |                                                                   |                                                                                              |          |

| 共同研究機関へのグリッド連携規模拡大 → 認証局運用開始(7月)                                                              |                                                                                         |                                                                                                                      |                                                                                                           |                                                                   |                                                                                              |          |

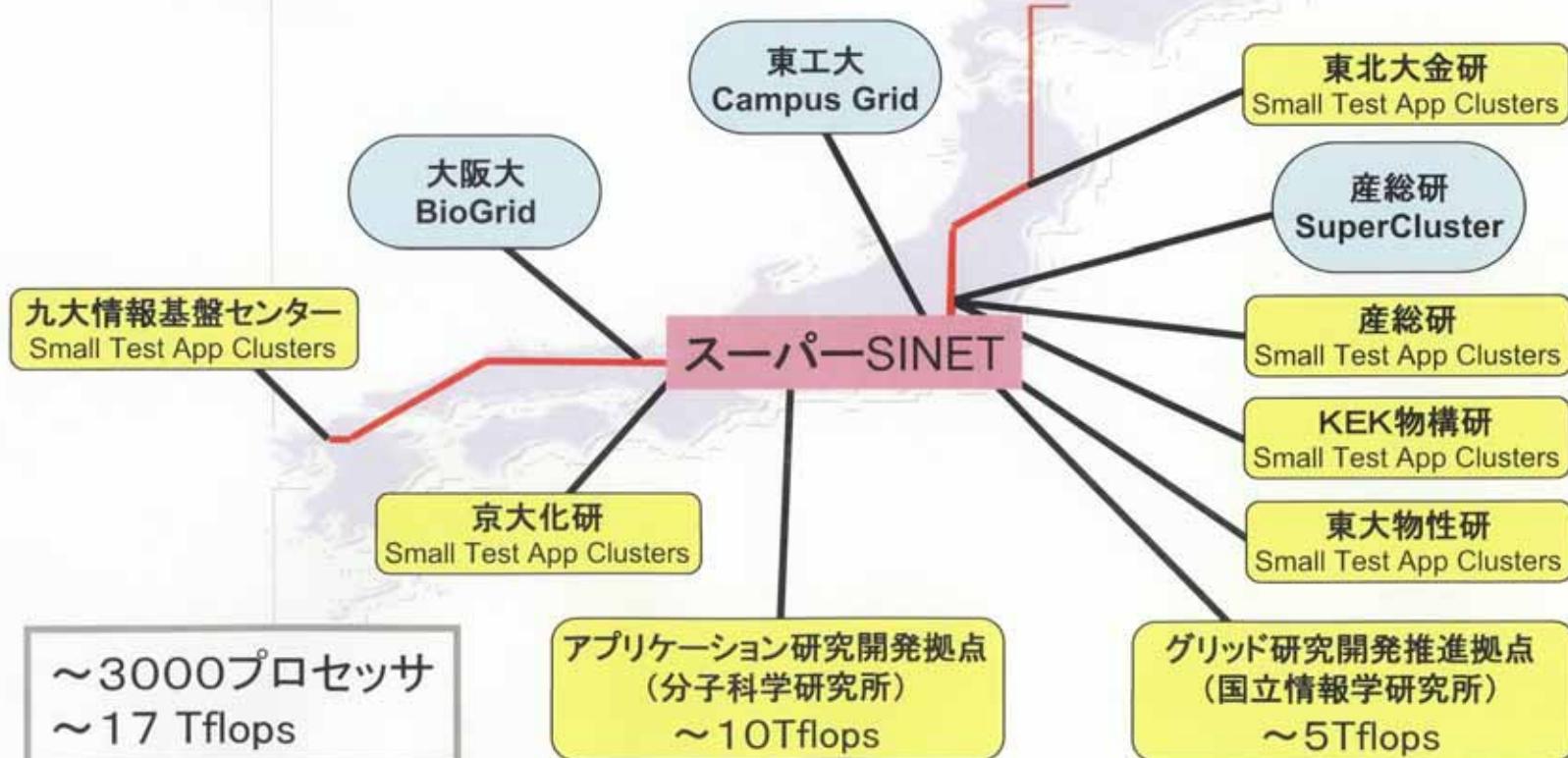

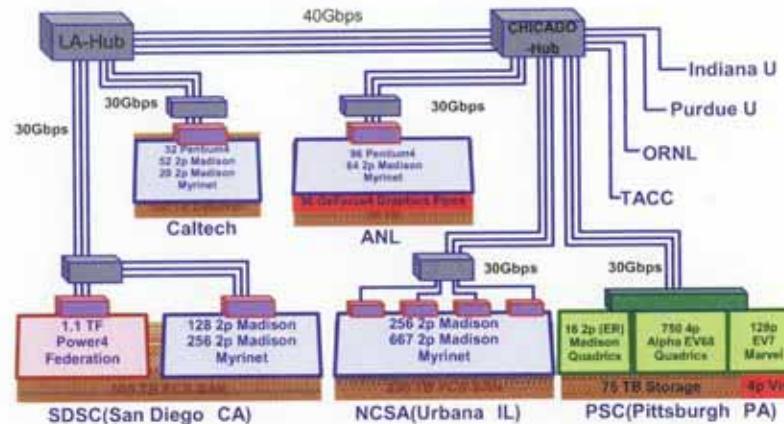

# NAREGI 広域分散テストベッドインフラの構築

グリッドミドルウェア開発、ナノ分野のグリッド実証研究を考慮したヘテロ、広域分散環境のテストベッドを構築

# 国際グリッドプロジェクトとの比較

## 欧州連合(EU)のEGEEプロジェクト

予算規模: 70 M Euro(2004-2007) 【93億円】

参加機関: >70

計算機資源: 8768 CPUs(Mid 2005)

アプリ分野: 高エネルギー物理学向けデータグリッド

バイオ他

ネットワーク: GEANT-NRENs(10Gbps)

基盤ミドルウェア: g-Lite (Globus ベース)

プロジェクト開始時期: 2004年4月

中心的機関: CERN(ジュネーブ)

•運用主体のプロジェクトである

EGEE: Enabling Grids for E-SciencE

CERN: European Organization for Nuclear Research

## 米国テラグリッド(Extensible Tera-scale Facility)

予算規模: 98M\$(2001-2003総計) 【109億円】

参加機関: >9

計算機資源: 40Tflops

•Teragrid固有: 20Tflops

•NSFセンター等接続分: 20Tflops

アプリ分野: サイエンス一般

ネットワーク: 専用線 (40Gbps)

基盤ミドルウェア: NMIパッケージ (Globus ベース)

プロジェクト開始時期: 2002年4月

運用開始時期: 2004年10月

中心的機関: National Science Foundation(NSF)

•運用主体のプロジェクトである

NMI: National Middleware Initiative

National Research Grid Initiative

# 7.7メモリ共有型マルチプロセッサ

## 重要問題

キャッシュコヒーレンス問題

メモリコンシステム問題

キャッシュ

コピーレンス問題

書き込み

種々のマルチ

プロセッサ

## 7.7.1 キャッシュコヒーレンスの分類

(1) ハードウェアによる方式

スヌープキャッシュ方式

ディレクトリ方式

(2) ソフトウェアによる方式

### 7.4.1 スヌープキャッシュ法

(1) 単純な方式の場合

スヌープコントローラ

(2) 各ブロックにタグを持たす方式

ライト時に無効化または更新

キャッシュ間転送時の主記憶に書き戻し

(3) バスの特徴

放送能力: 分散制御

排他制御: 逐次コンシンシ

## スヌープ方式

P<sub>a</sub>

P<sub>b</sub>

スヌープ

コントローラ

書込み情報の放送

共有バス

キャッシュ間転送

実記憶に書戻す/

戻さない

共有実記憶装置

図 4.24 スヌープキャッシュの基本方式

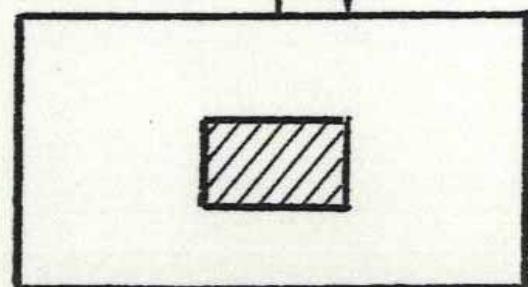

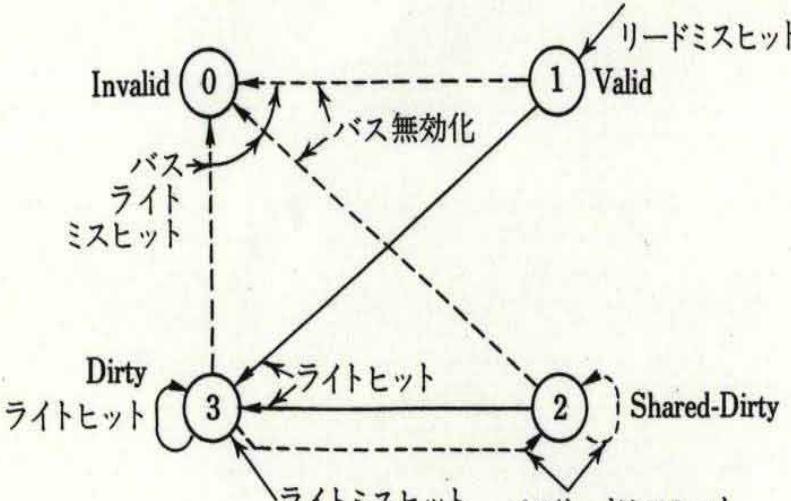

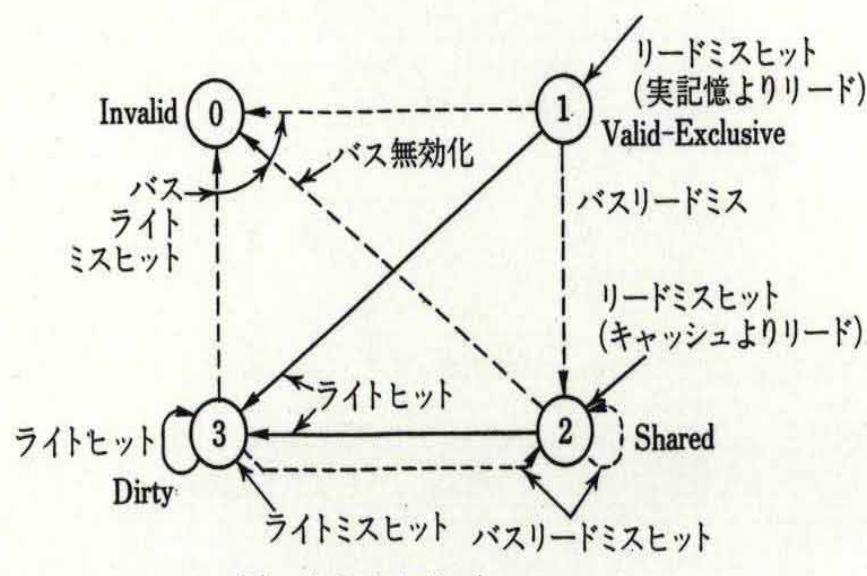

表 4.3 スヌーフキャッシュ方式

| 共有ブロックへの書込み時処理<br>キャッシュ間転送時の主記憶更新 | プロードキャスト無効化                                                                                                                                                                                       | プロードキャスト更新                                                                                                                                                                                             |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

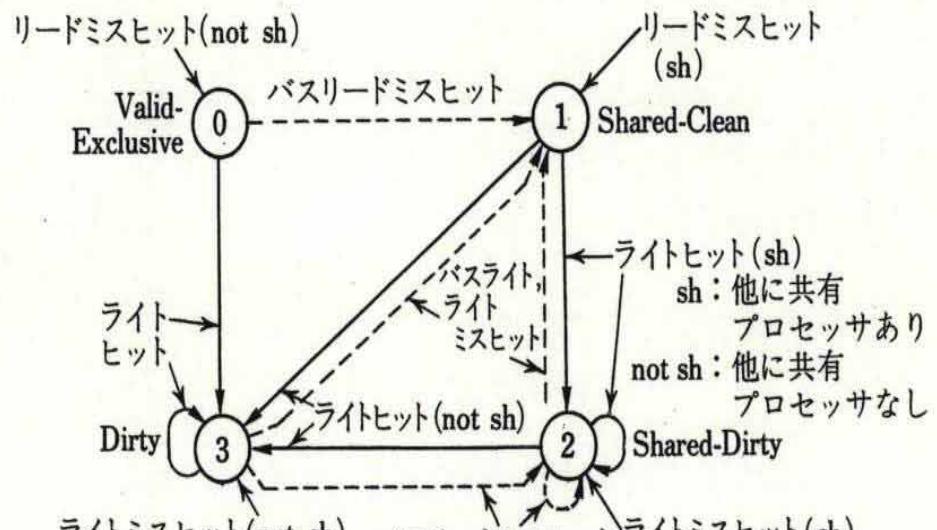

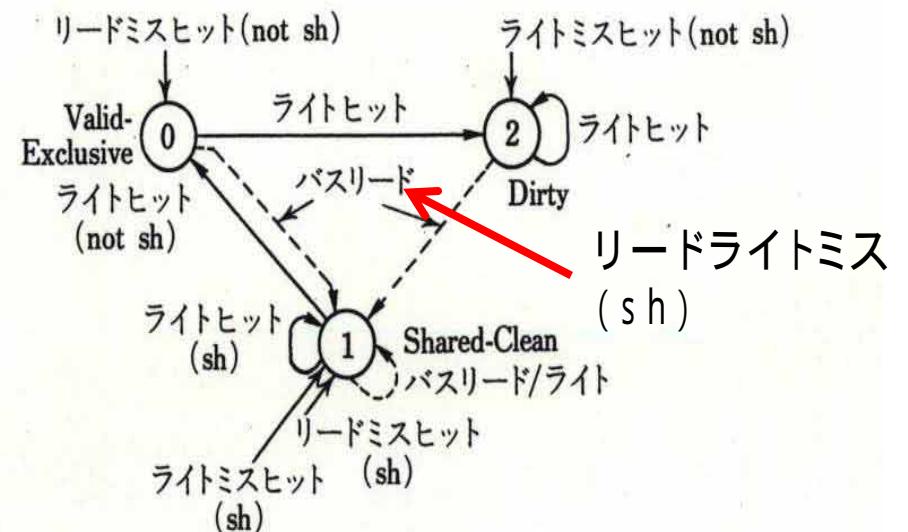

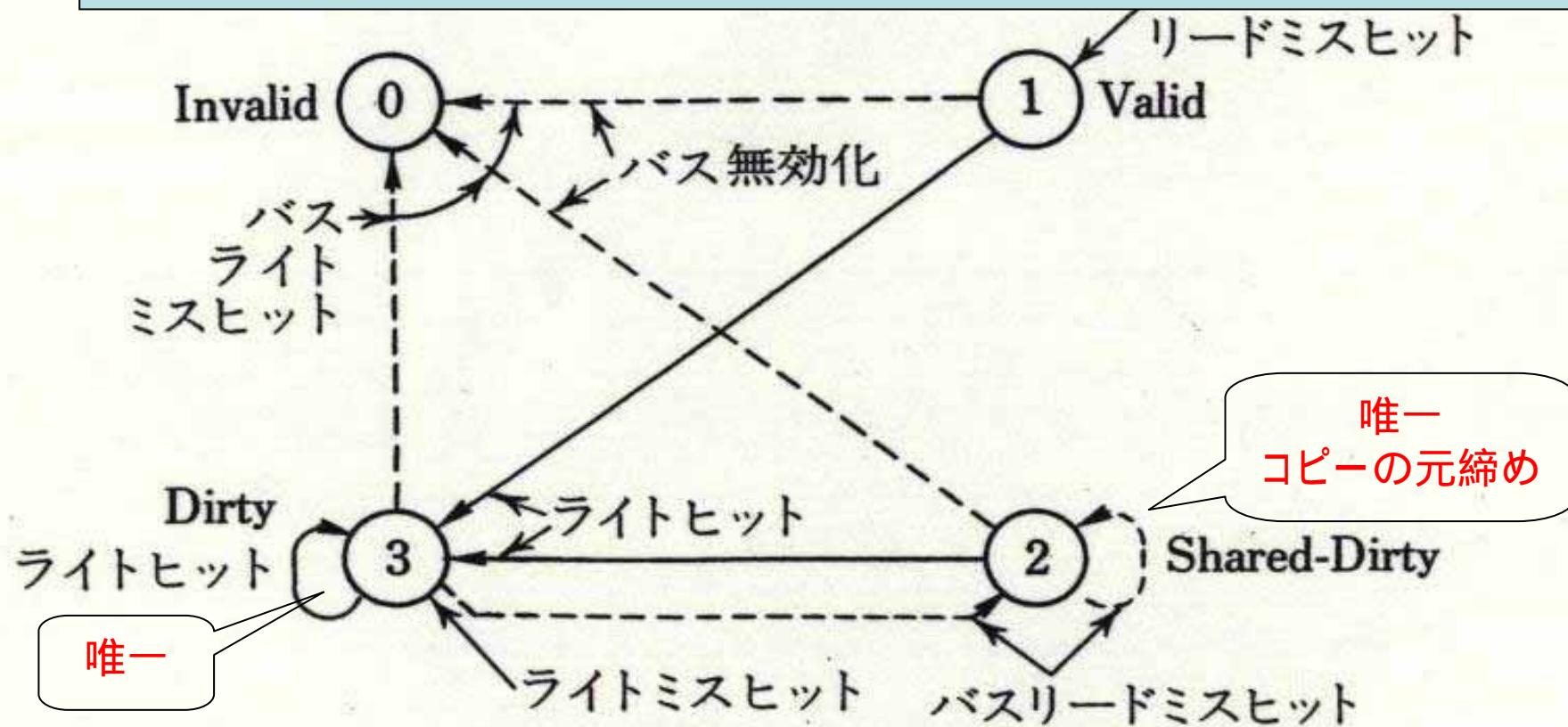

| 変更のあるブロックのキャッシュ間転送時に主記憶へは書き戻さない   | Berkeley<br>State 0: Invalid<br>State 1: Valid (clean, potentially shared, unowned)<br>State 2: Shared-Dirty (modified, potentially shared, owned)<br>State 3: Dirty (modified, only copy, owned) | Dragon<br>State 0: Valid-Exclusive (clean, only copy)<br>State 1: Shared-Clean (clean, one or more copy)<br>State 2: Shared-Dirty (modified, one or more copy)<br>State 3: Dirty (modified, only copy) |

| 変更のあるブロックのキャッシュ間転送時に主記憶へも書き戻す     | Illinois<br>State 0: Invalid<br>State 1: Valid-Exclusive (clean, only copy)<br>State 2: Shared (clean, possibly other copies)<br>State 3: Dirty (modified, only copy)                             | Firefly<br>State 0: Valid-Exclusive (clean, only copy)<br>State 1: Shared (clean)<br>State 2: Dirty (dirty, only copy)                                                                                 |

(a) パークレイプロトコル

(b) イリノイプロトコル

MESI Pentiumで採用

(c) ドラゴンプロトコル

(d) ファイアフライプロトコル

DEC Firefly

Multiprocessor

図 4.25 種々のプロトコル<sup>13)</sup>

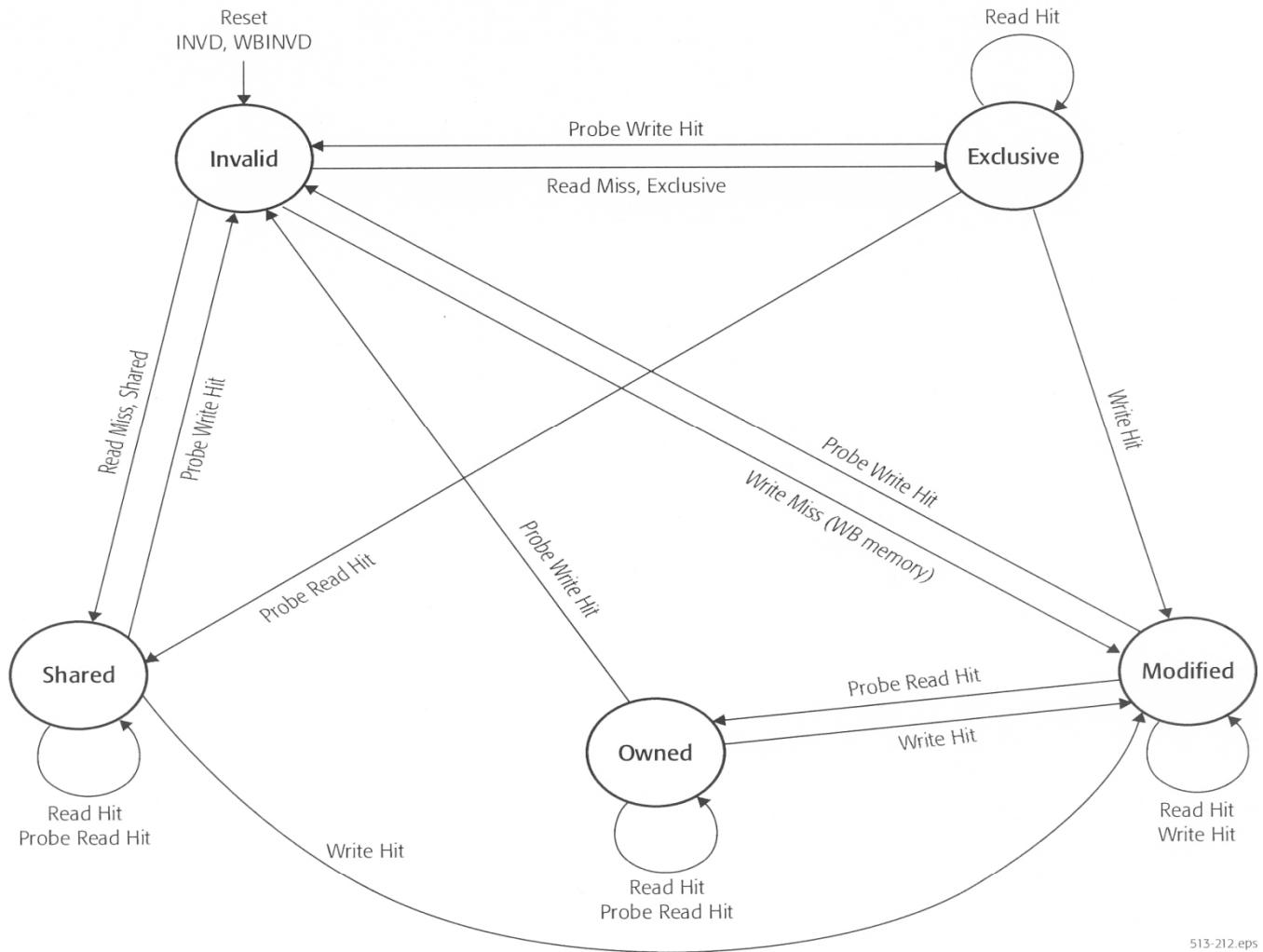

## MOESI ADM 6 4で採用

- Modified Dirty 唯一、メモリ内容と不一致

- Owned 唯一、メモリ内容と不一致、コピーを持つのは Shared

- Exclusive, Clean, 唯一

- Shared 他にOwnedがあればメモリ内容と不一致、なければメモリ内容と一致

- Invalid 無効

| プロセッサA 状態 |              | プロセッサB 状態 |       | プロセッサC 状態 |         |

|-----------|--------------|-----------|-------|-----------|---------|

| LOAD      | Valid        |           |       |           |         |

| STORE     | Dirty        |           |       |           |         |

|           | Shared Dirty | LOAD      | Valid |           |         |

|           | InValid      | STORE     | Dirty | LOAD      | Valid   |

|           |              |           |       |           | InValid |

(a) バークレイプロトコル

**Figure 7-2. MOESI State Transitions**

To maintain memory coherency, external bus masters (typically other processors with their own internal caches) need to acquire the most recent copy of data before caching it internally. That copy can be in main memory or in the internal caches of other bus-mastering devices. When an external master has a cache read-miss or write-miss, it *probes* the other mastering devices to determine whether the most recent copy of data is held in any of their caches. If one of the other mastering devices holds the most recent copy, it provides it to the requesting device. Otherwise, the most recent copy is provided by main memory.

表1:キャッシュラインの状態遷移の例

|   | 事象                                                   | P0        | P1       | P2      |

|---|------------------------------------------------------|-----------|----------|---------|

| 0 | 初期状態                                                 | Invalid   | Invalid  | Invalid |

| 1 | P0 Read                                              | Exclusive | Invalid  | Invalid |

| 2 | P1 Read;P0応答データ供給                                    | Shared    | Shared   | Invalid |

| 3 | P2 Read;P0応答データ供給                                    | Shared    | Shared   | Shared  |

| 4 | P0 Write;Invalidate応答を待ってWrite                       | Modified  | Invalid  | Invalid |

| 5 | P2 Read;P0応答データ供給                                    | Owned     | Invalid  | Shared  |

| 6 | P1 Write;Invalidate、P0(Owner)応答データ供給、P2 Invalidate応答 | Invalid   | Modified | Invalid |

| 7 | P2 Read;P1応答データ供給                                    | Invalid   | Owned    | Shared  |

| 8 | P1 Writeback                                         | Invalid   | ---      | Shared  |

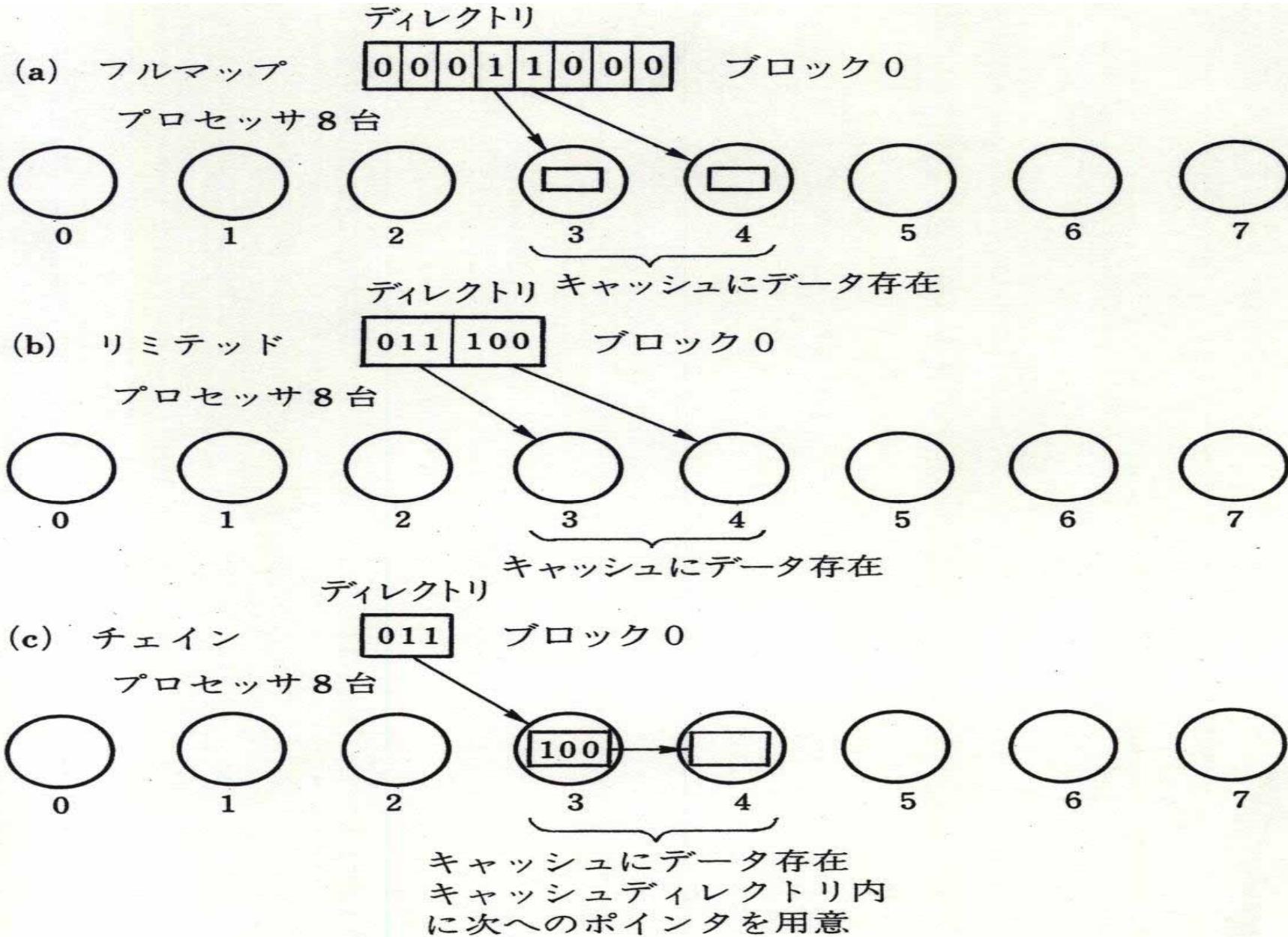

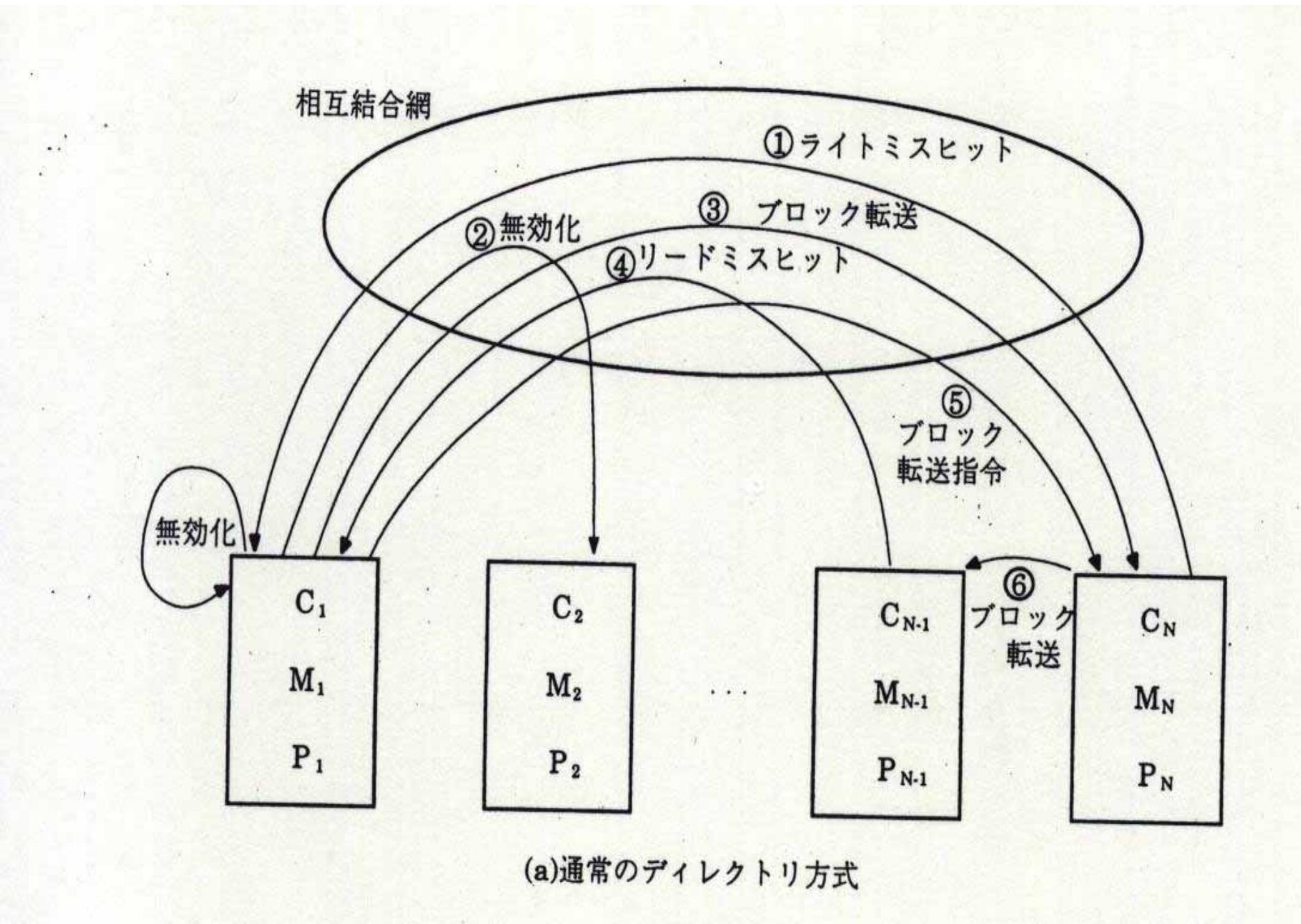

## ディレクトリ方式

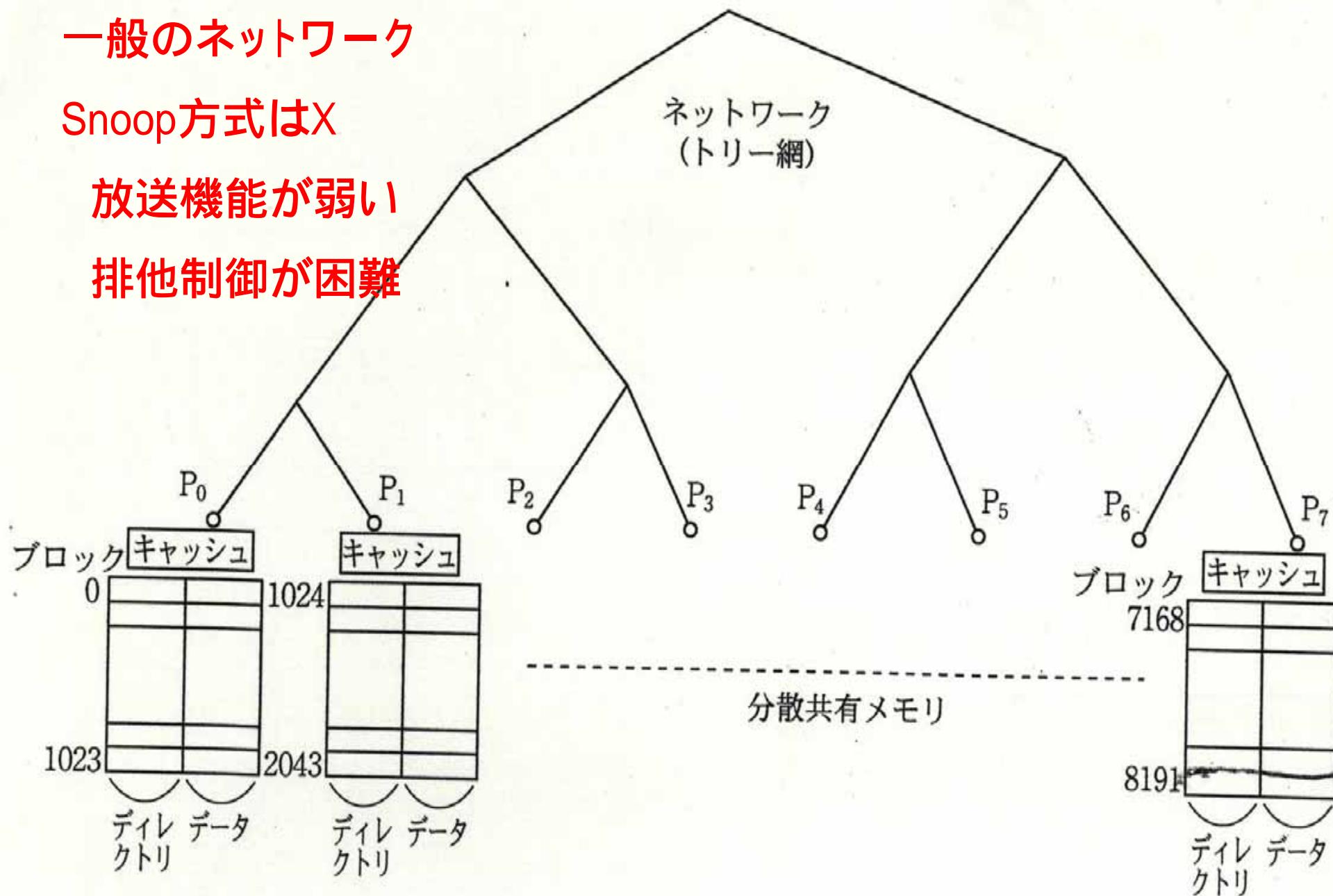

一般のネットワーク利用

メモリ側で集中管理

フルマップ

リミテッド

チェイン

一般のネットワーク

Snoop方式はX

放送機能が弱い

排他制御が困難

図 4.26 ディレクトリ方式

図 4.27 ディレクトリ方式

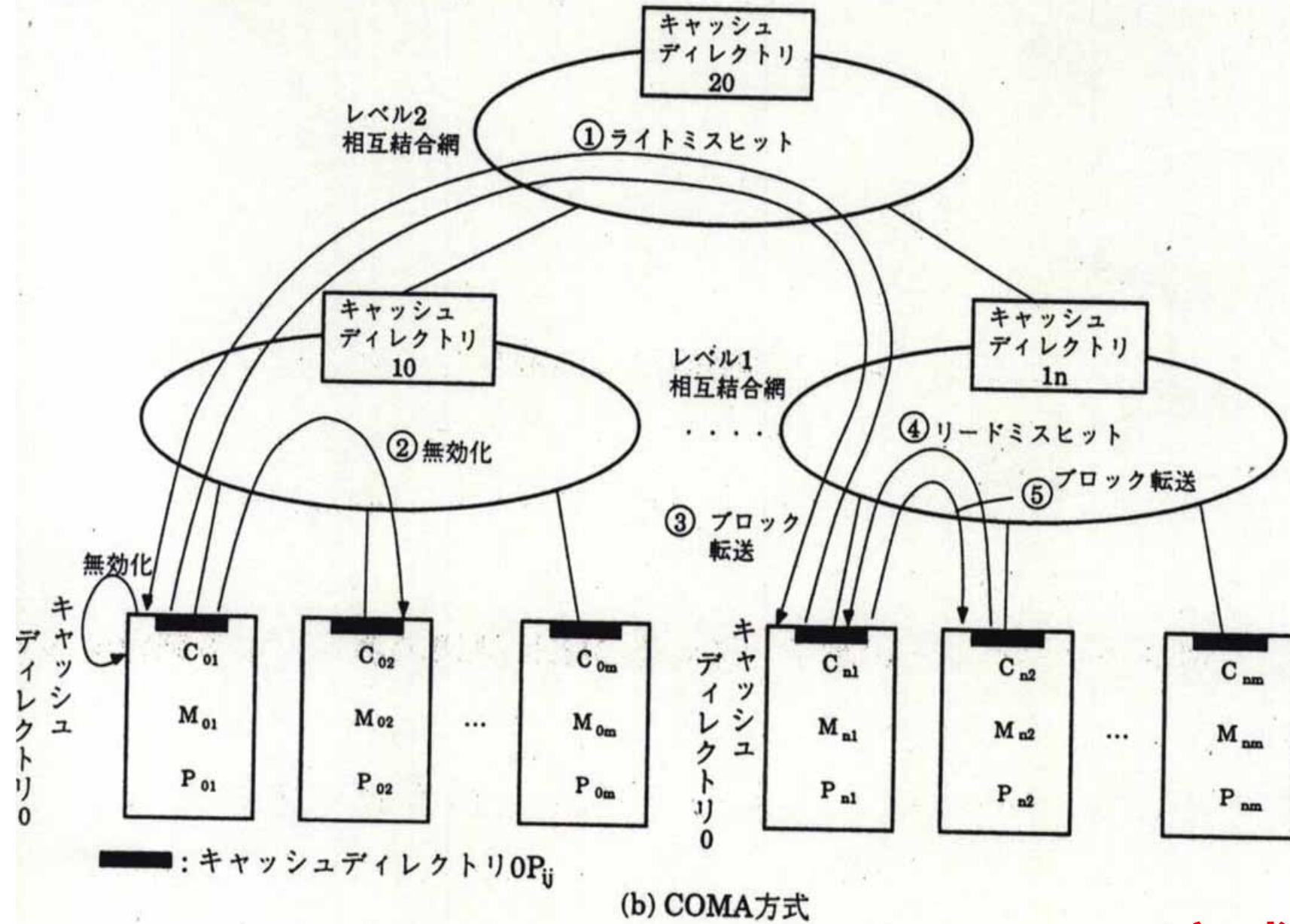

図 5.11 キャッシュオンリメモリ方式

# COMA方式

## 具体例

コピーレンスの動作を応用例で見ると

線形1次方程式の反復解法

$$AX = a \quad X = b + BX$$

$$X = D^{-1}((D-A)X + a) : ヤコビ法$$

直接法：ガウス消去法、LU分解法

スヌープキャッシュの2つのプロセッサで並列実行

同期命令が必要：先走り禁止

新しい値 / 古い値を使ってしまう

無効化 / 更新どちらがよいか

この場合は更新

コピーレンス制御が必要のないものがある

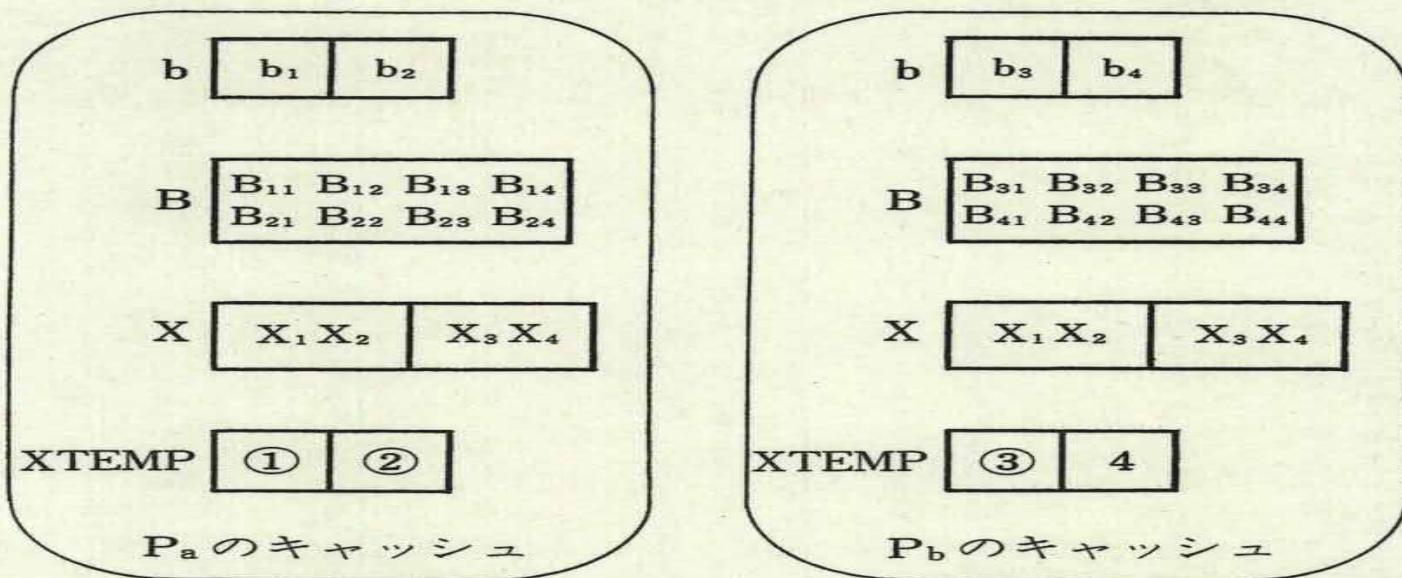

```

DO 30 I=1, M

DO 20 J=1, 4

XTEMP (J)=b (J)

DO 20 K=1, 4

XTEMP (J)=XTEMP (J)+B (J, K) * X (K)

同期操作      20 CONTINUE

DO 10 J=1, 4

X (J)=XTEMP (J)

同期操作      10 CONTINUE

30 CONTINUE

```

エポック1

エポック2

$J=1,2 : P_a \text{ で分担}$

$J = 3,4 : P_b \text{ で分担}$

(a) 線形方程式の反復解法

$$\begin{pmatrix} X \\ \begin{pmatrix} X_1 \\ X_2 \\ X_3 \\ X_4 \end{pmatrix} \end{pmatrix} = \begin{pmatrix} b \\ \begin{pmatrix} b_1 \\ b_2 \\ b_3 \\ b_4 \end{pmatrix} \end{pmatrix} + \begin{pmatrix} B \\ \begin{pmatrix} B_{11} B_{12} B_{13} B_{14} \\ B_{21} B_{22} B_{23} B_{24} \\ \hline B_{31} B_{32} B_{33} B_{34} \\ B_{41} B_{42} B_{43} B_{44} \end{pmatrix} \end{pmatrix} \begin{pmatrix} X \\ \begin{pmatrix} X_1 \\ X_2 \\ X_3 \\ X_4 \end{pmatrix} \end{pmatrix}$$

(b) キャッシュの状態

図 4.28 ソフトウェアによるキャッシュコヒーレンス制御方式

# ソフトウェアによる方式

コンパイラで共有データを検出

リードオンリ、排他的専有利用データ: 対象外

ストアスルーを前提: 最新データはメモリに存在、ハード簡単

ソフト的な選択的無効化

マーキング法: 共有データにマークを付け、キャッシュしない

キャッシュ無効化命令: 共有データブロックをひとつ

ひとつ命令で無効化

ハードウェアによるキャッシュ全面的無効化

同期命令でキャッシュ全面無効化

リードオンリデータはCache Read命令で復活、有効化

共有データはMemory Readでミスヒット、

メモリからキャッシュへ転送、その後ヒット

ハードウェアによる選択的無効化機構の設置

キャッシュブロックごとに無効化ビットを持たせ、一斉に選択

的に無効化

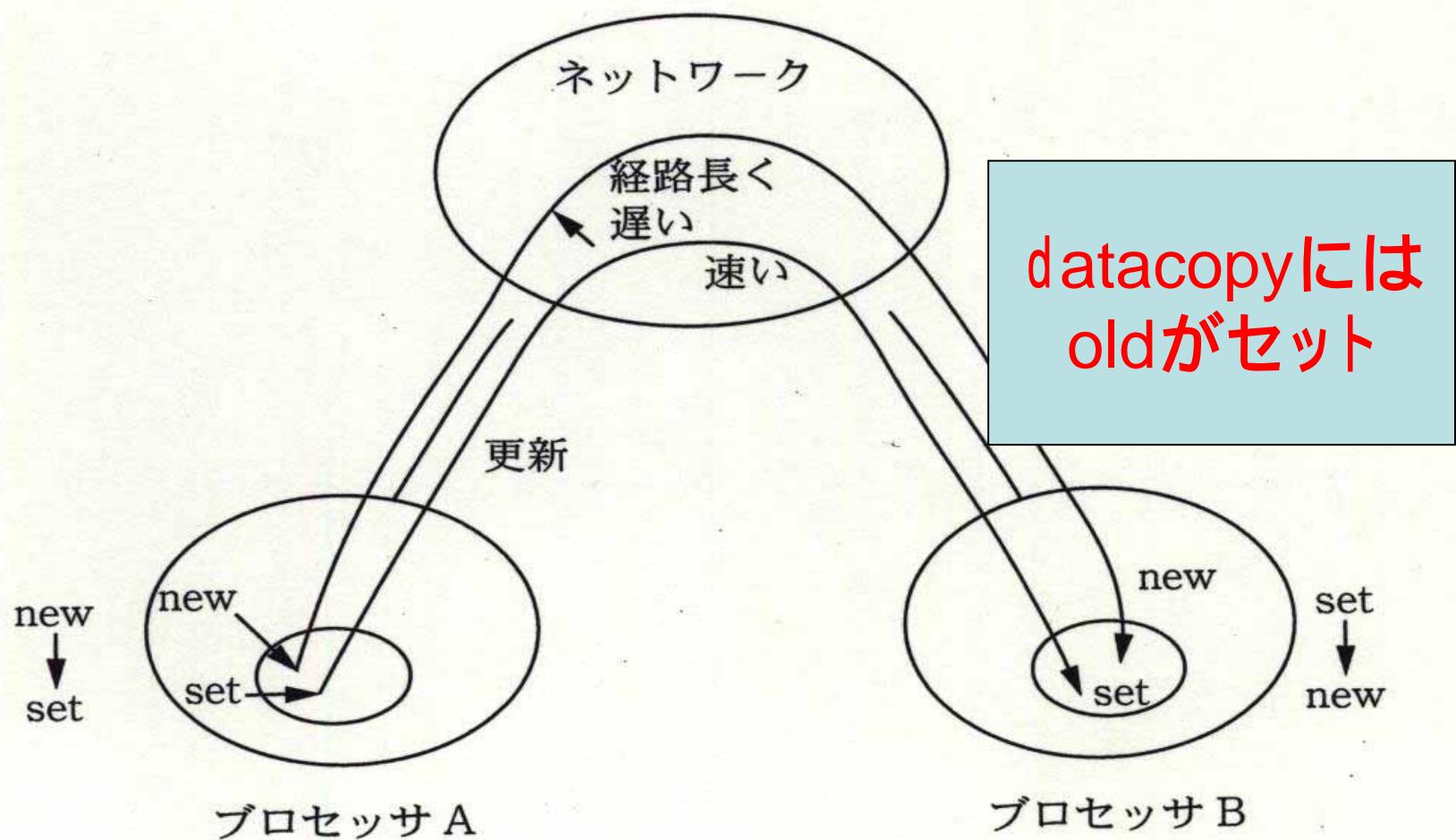

## 7.8メモリコンシステムシモデル

書き込みの順序づけ(ordering)

プロセッサA,Bが書き込み

プロセッサC: Aの後Bが到着

これでよいのか?

プロセッサD: Bの後Aが到着

### 7.8.1プロセッサコンシステムシモデル

プロセッサA

プロセッサB

data = new;

while (flag != set) {}

flag = set;

datacopy = data;

同一のプロセッサからのライト:

その順で反映

2つ以上のプロセッサで発せられた書き込み:

順序については何も制約なし

プロセッサ A

- ① data=new ;

- ② flag=set ;

プロセッサ B

- ③ while (flag != set) {}

- ④ datacopy=data ;

(a) プロセッサコンセンスシステムモデル違反

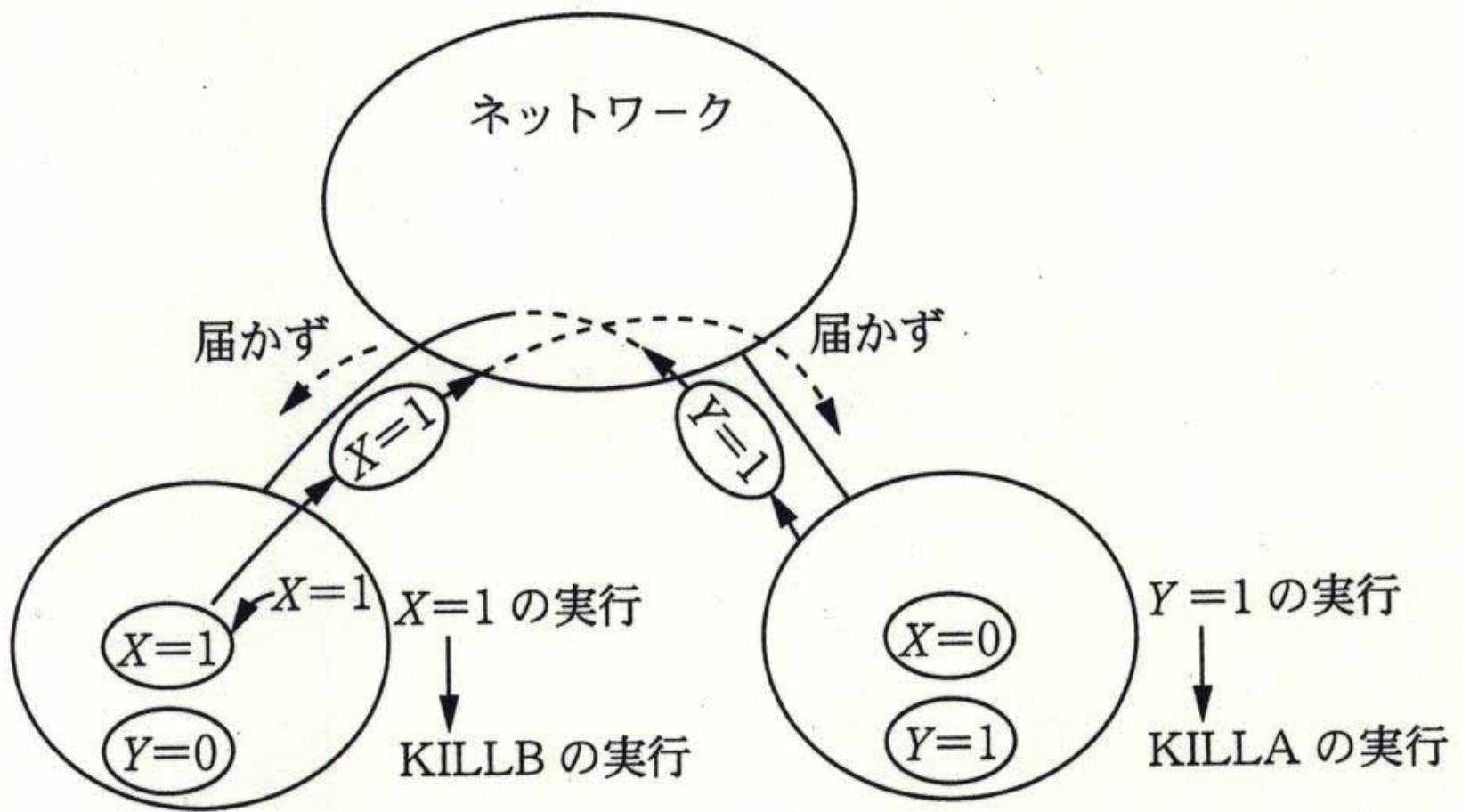

## 7.8.2 逐次(sequential)コンセンス

$$X = Y = 0$$

プロセッサA

$$X = 1$$

IF  $Y = 0$  KILL B

プロセッサB

$$Y = 1$$

IF  $X = 0$  KILL A

A,Bともに相打ちは

起こるか？

(1) Lamportの逐次コンセンス定義

マルチプロセッサ上での

並列プログラムの実行結果 =

並列プログラムを単一のプロセッサで

時分割で実行したときと同一

(b) 逐次コンセンティシモデル違反

図 4.29 メモリコンセンティシ問題

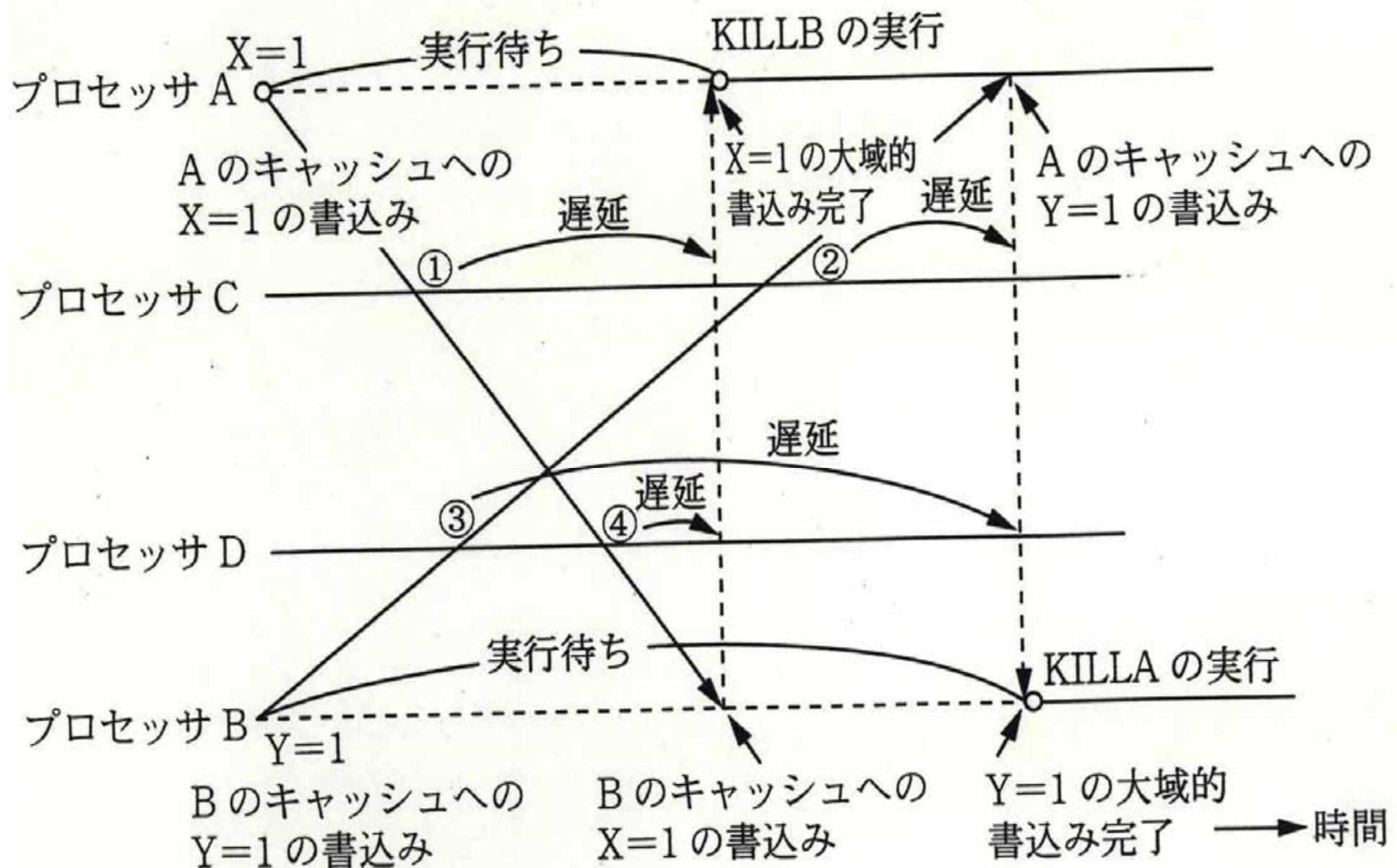

## (2)十分条件

並べられた命令順に実行

メモリ操作の大域的完了後，後続メモリ操作

発行

大域的書込み完了：

書込み操作がすべてのプロセッサに反映

大域的読み込み完了：

リードデータが大域的に書き込み完了

図 4.30 逐次コンシスティンシの実現

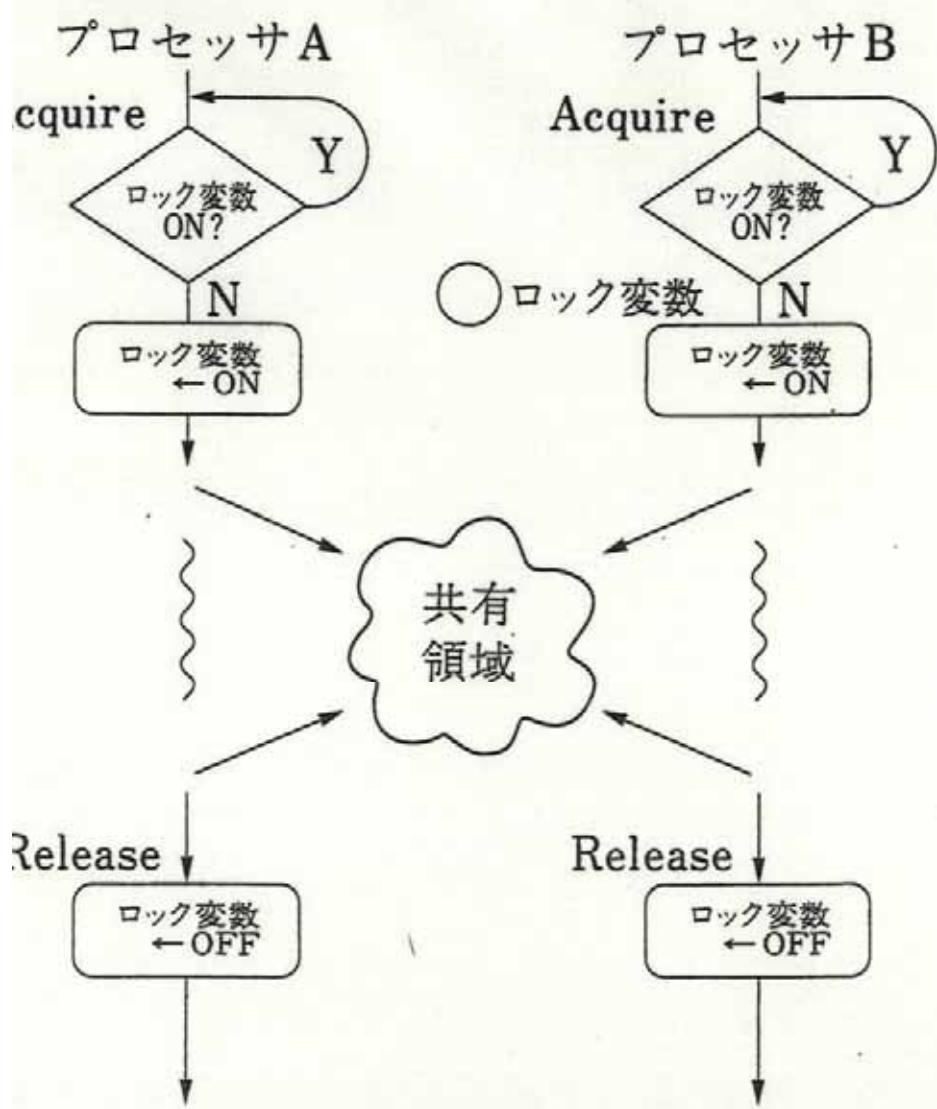

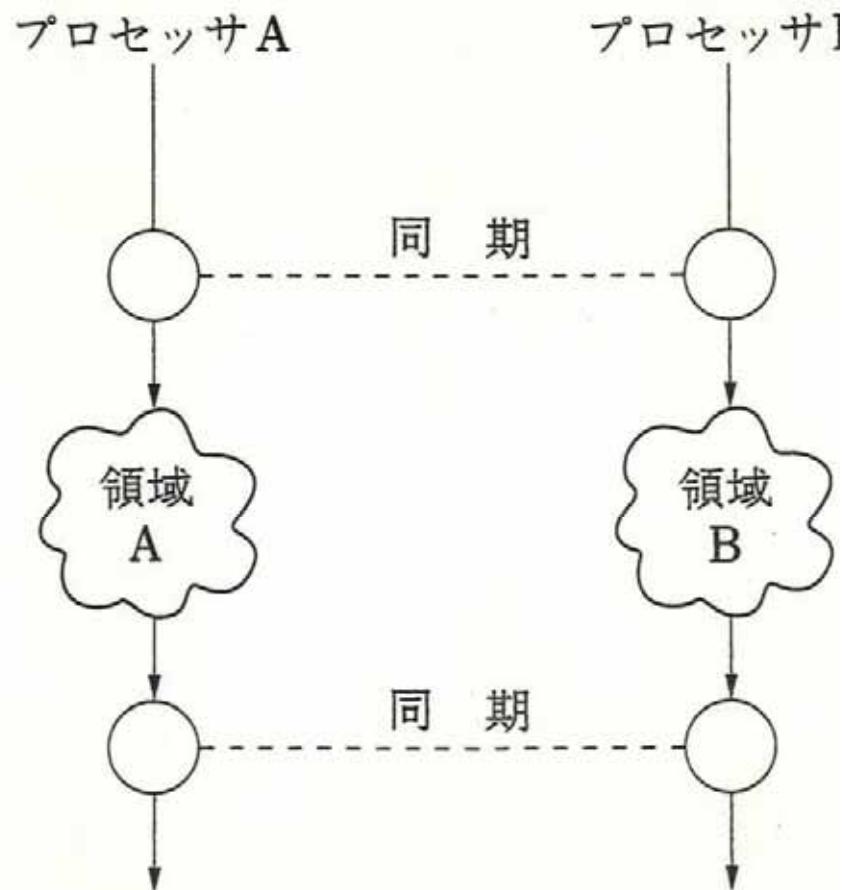

### (3)逐次コンシスティンシの緩和

臨界領域へのアクセス

異なる領域へのアクセス

Weakコンシスティンシ

同期命令

先行命令の大域的完了後発行

後続命令は同期命令の大域的完了後発行

Releaseコンシスティンシ

Acquire同期命令

後続命令はAcquireの大域的完了後発行

Release同期命令

先行命令の大域的完了後発行

後続命令は発行可

(a) 臨界領域へのアクセス

(b) 異なる領域へのアクセス

図 4.31 共有データへのアクセス

## 7.9 メッセージパッシング型 マルチプロセッサ

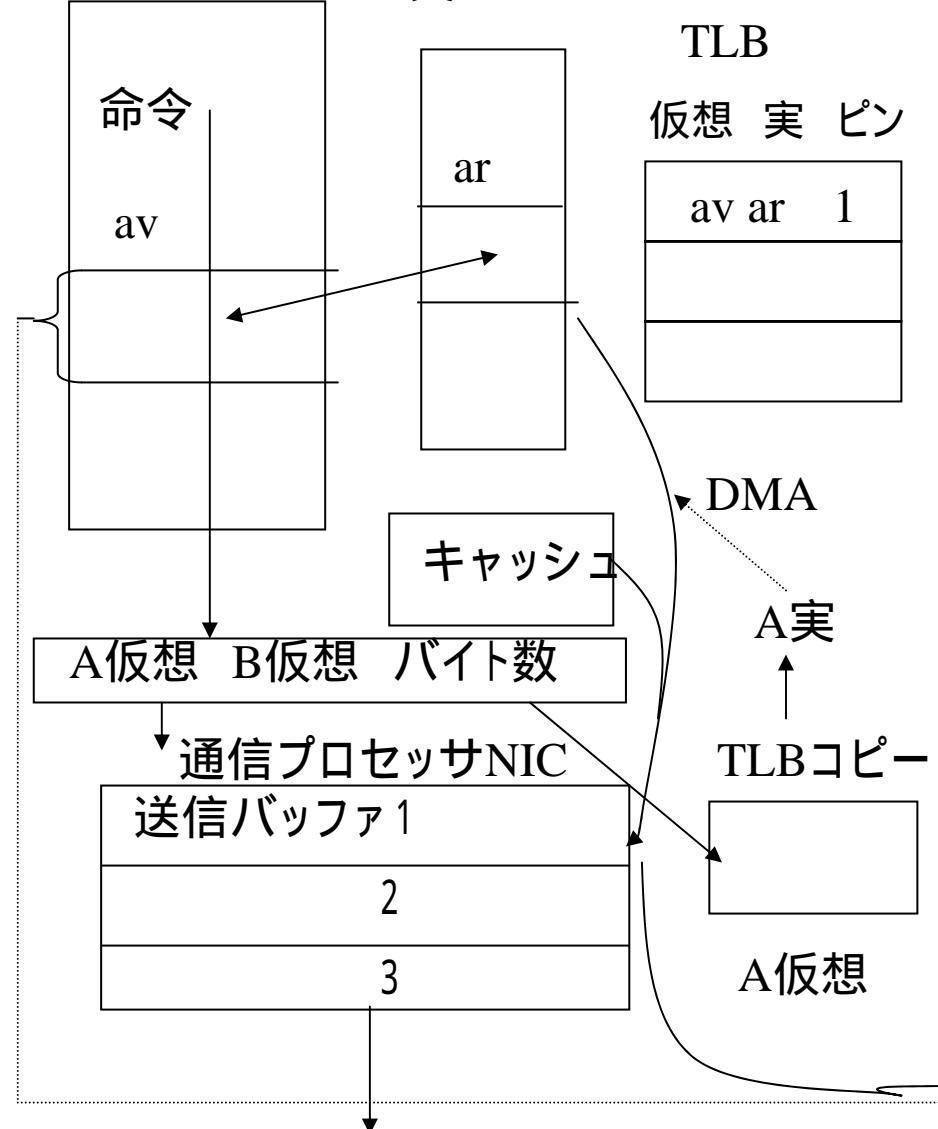

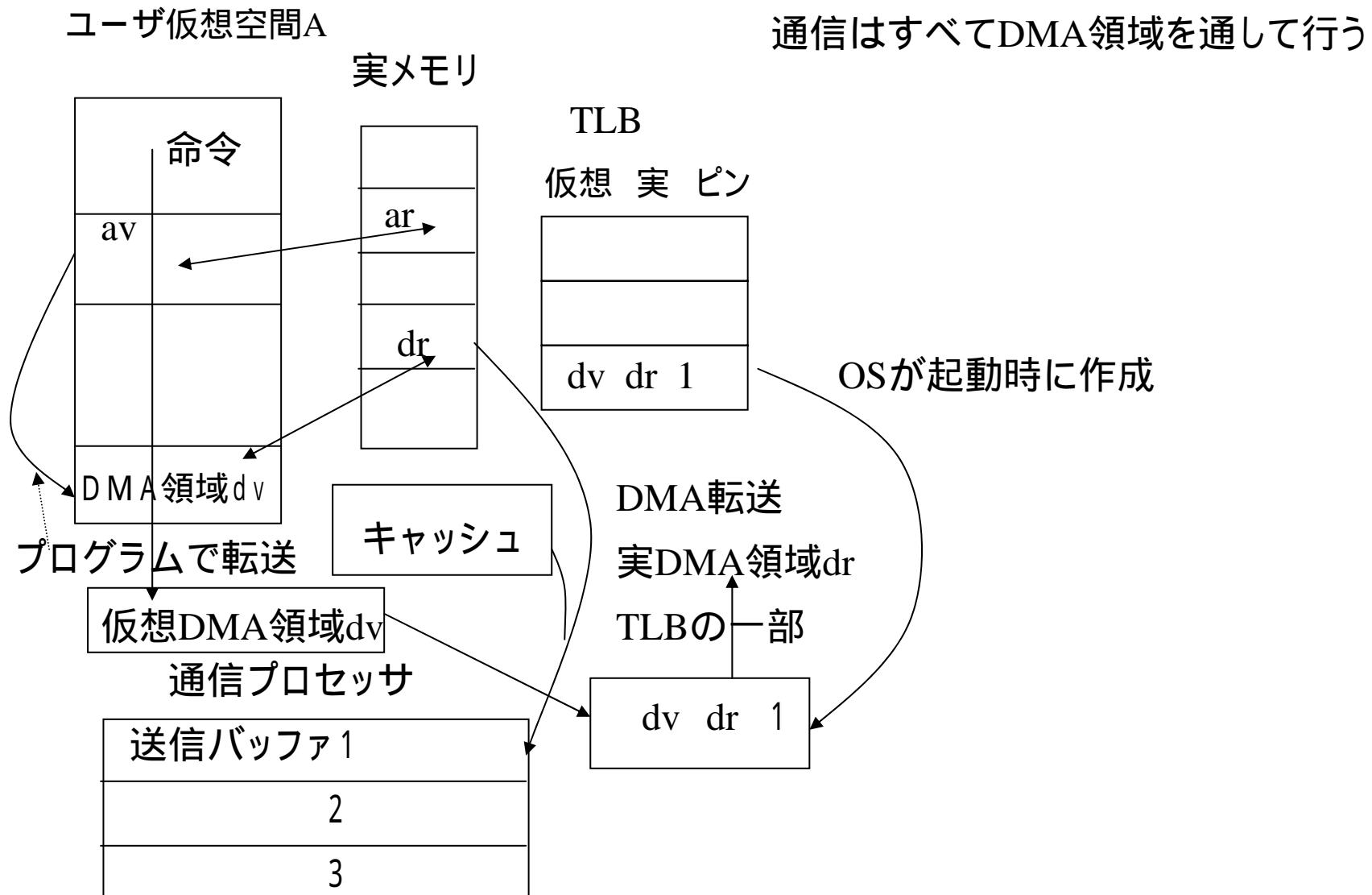

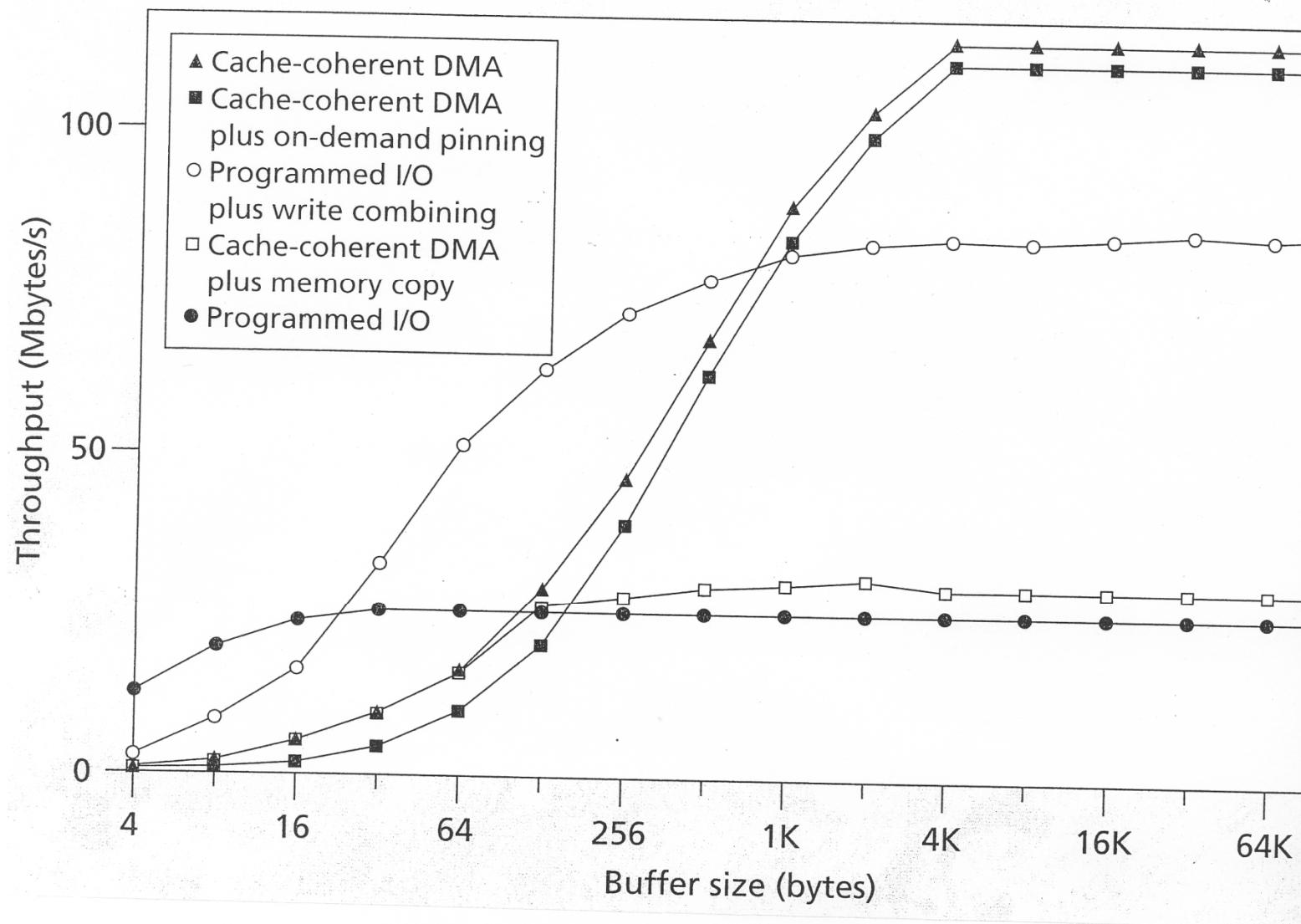

# ユーザレベル通信

## OSの介在の少ない方式

### Zero - Copy

## 仮想記憶によるセキュリティ確保

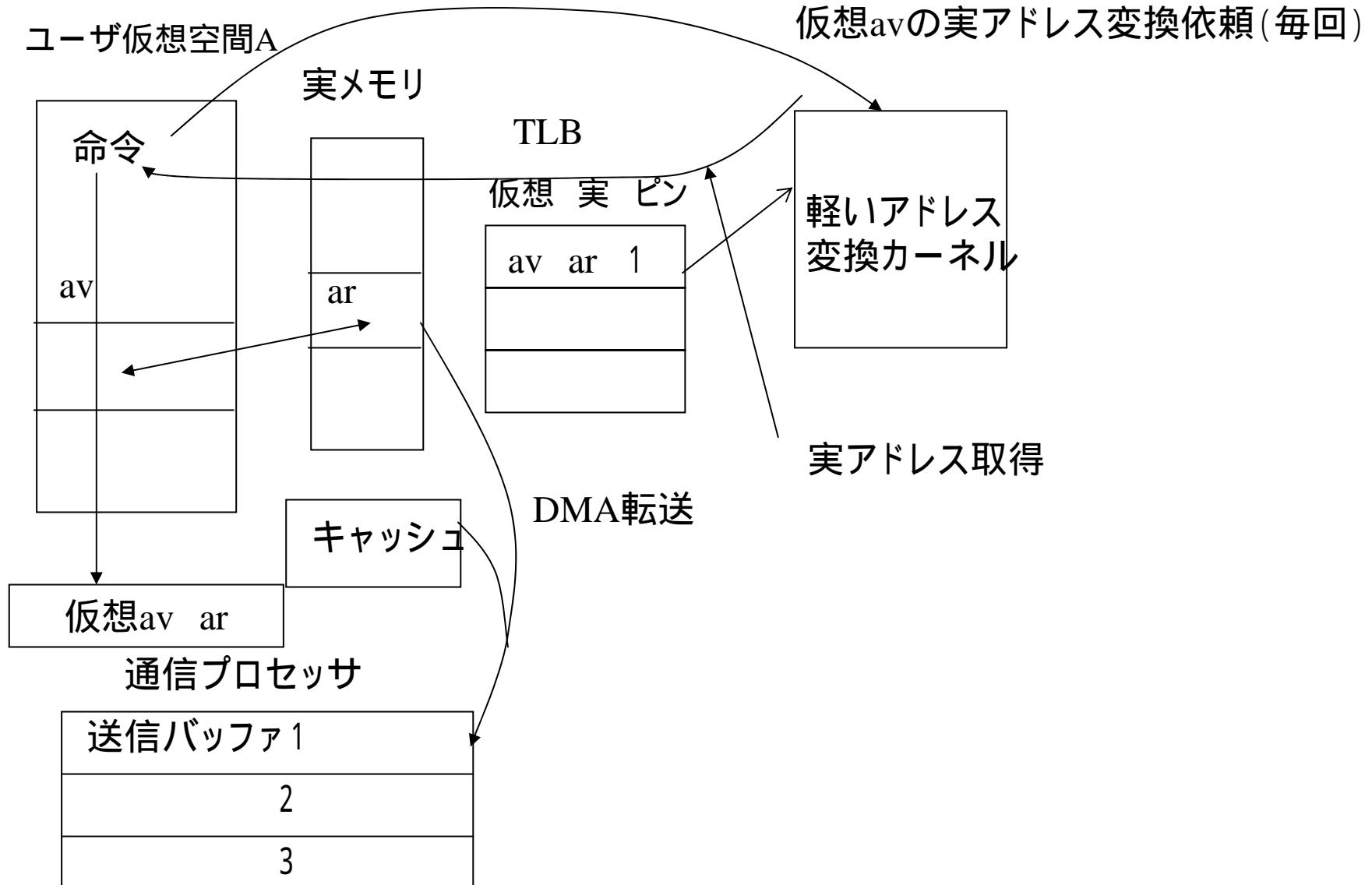

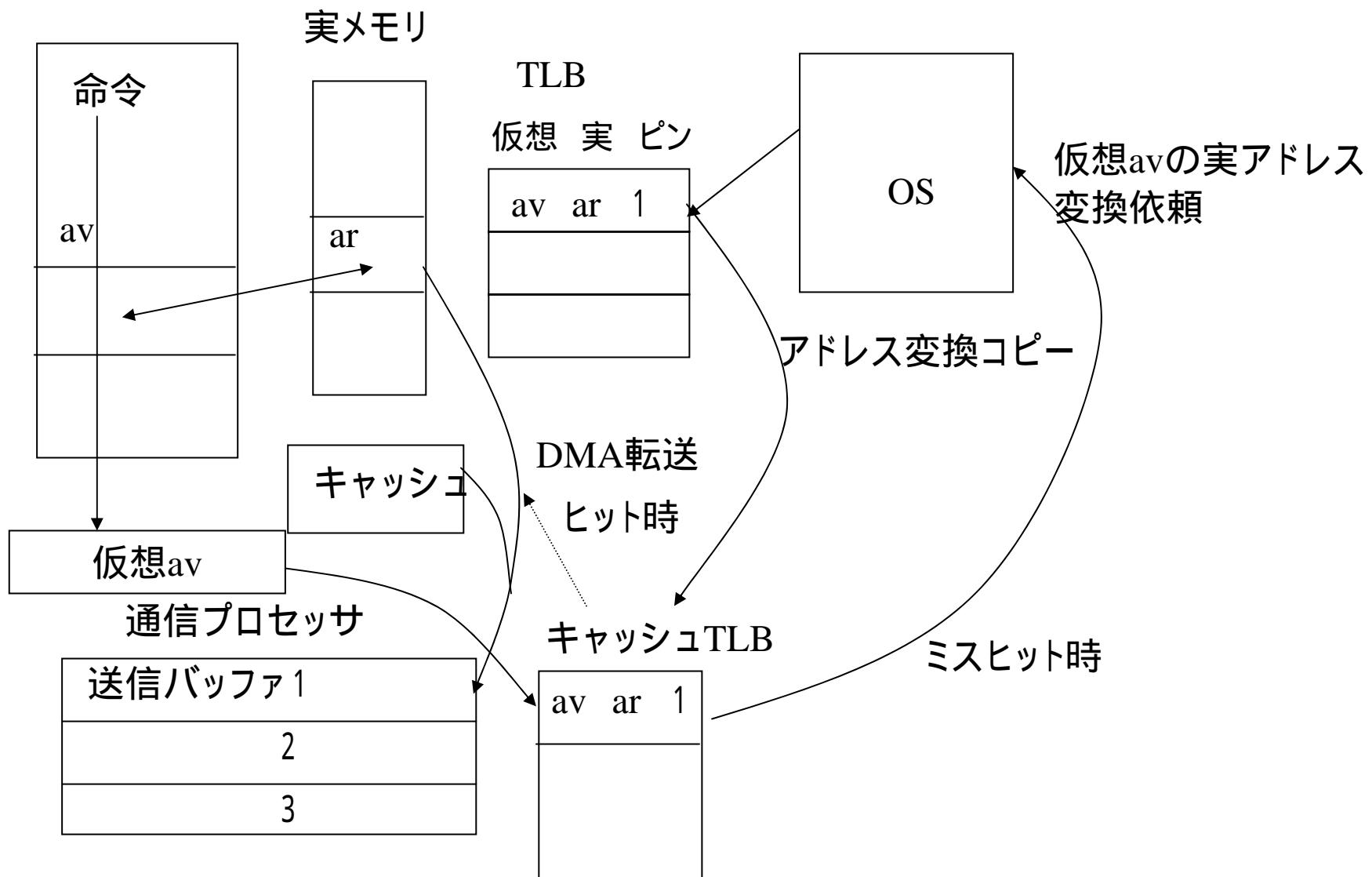

### (1)DMAを用いた方式

固定DMA領域にコピー : AM-II, Hamlyn

軽いアドレス変換カーネルを毎回起動、 BIP, LFC

TLBキャッシュ : VMMC-2, U-NET

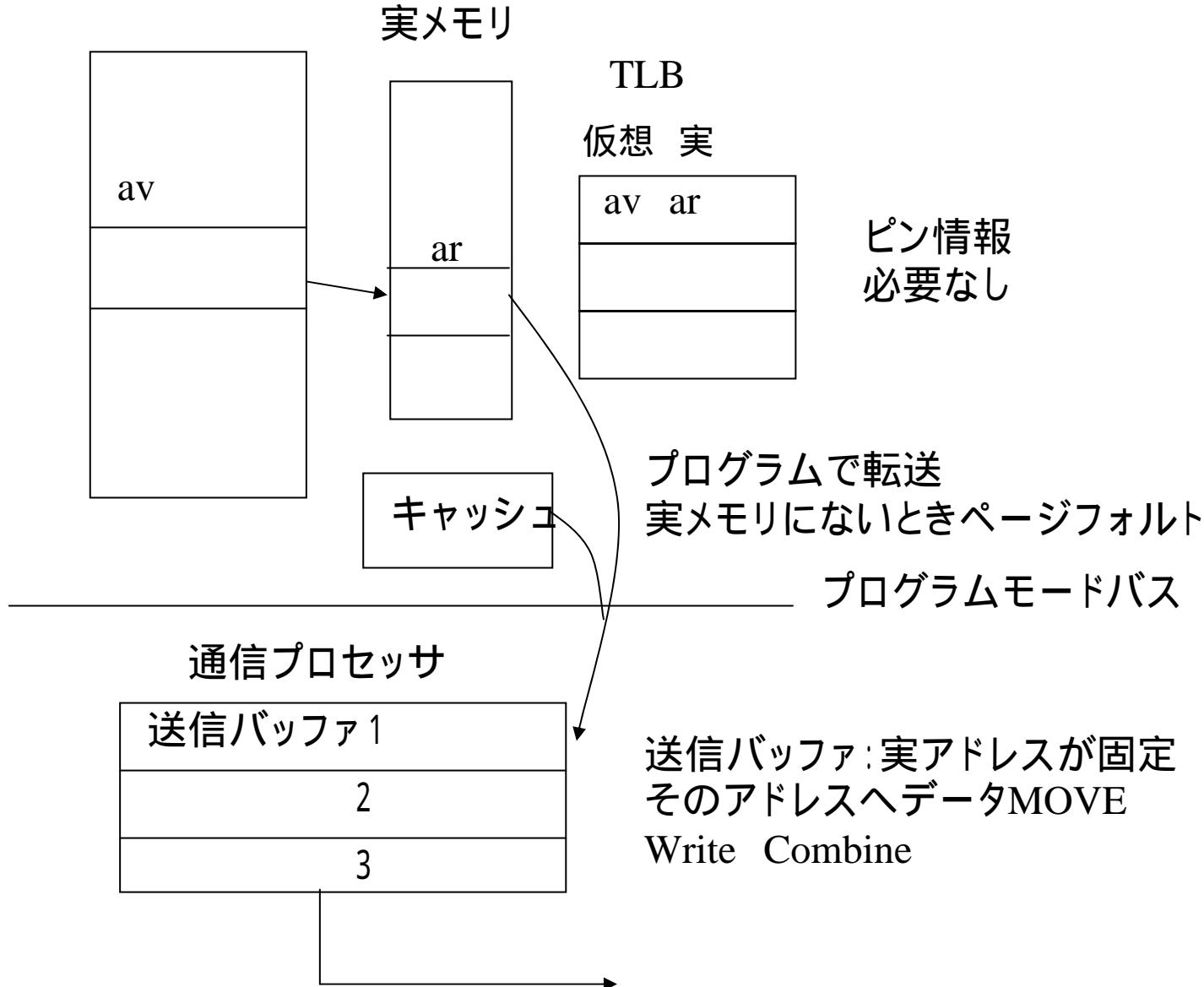

### (2)プログラムモードバス方式

Write Combining あり : FM, LFC, AM-II, Hamlyn, BIP

同上なし

**Table 1. Characteristics of 11 communication systems built for Myrinet.**

| System               | Data transfer<br>(host-MM) | Translation                                        | Protection                  | Control<br>transfer                | Reliability                                                                                           | Multicast<br>support             |

|----------------------|----------------------------|----------------------------------------------------|-----------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------|

| AM-II <sup>1</sup>   | PIO & DMA*                 | DMA areas                                          | Yes                         | Polling + interrupts               | Reliable, network interface:<br>alternating bit,<br>host: sliding window                              | No                               |

| FM <sup>2</sup>      | PIO                        | DMA area (recv)                                    | No                          | Polling                            | Reliable, host-level credits                                                                          | No                               |

| FM/MC <sup>3</sup>   | PIO                        | DMA area (recv)                                    | No                          | Polling + interrupts               | Reliable, unicast: host-level<br>credits, multicast: network-<br>interface-level credits              | Yes<br>(on network<br>interface) |

| PM <sup>4</sup>      | DMA                        | Software TLB* on<br>network interface              | Yes<br>(gang<br>scheduling) | Polling                            | Reliable, ACK/NACK<br>protocol on network interface                                                   | Yes<br>(multiple sends)          |

| VMMC <sup>5</sup>    | DMA                        | Software TLB on<br>network interface               | Yes                         | Polling + interrupts               | Reliable, exploits<br>hardware backpressure                                                           | No                               |

| VMMC-2 <sup>6</sup>  | DMA                        | UTLB* in kernel,<br>cached on network<br>interface | Yes                         | Polling + interrupts               | Reliable                                                                                              | No                               |

| LFC <sup>7</sup>     | PIO                        | User translates                                    | No                          | Polling + interrupts<br>+ watchdog | Reliable, unicast: network-interface-<br>level credits, multicast:<br>network-interface-level credits | Yes<br>(on network interface)    |

| Hamlyn <sup>8</sup>  | PIO & DMA                  | DMA areas                                          | Yes                         | Polling + interrupts               | Reliable, exploits hardware<br>backpressure                                                           | No                               |

| Trapeze <sup>9</sup> | DMA                        | DMA to page frames                                 | No                          | Polling + interrupts               | Unreliable                                                                                            | No                               |

| BIP <sup>10</sup>    | PIO & DMA                  | User translates                                    | No                          | Polling                            | Reliable, rendezvous<br>and backpressure                                                              | No                               |

| U-Net <sup>11</sup>  | DMA                        | TLB on network<br>interface<br>(U-Net/MM)          | Yes                         | Polling + interrupts               | Unreliable                                                                                            | No                               |

## DMA基本方式 転送実領域:貼付け(ピン)、通信プロセッサ TLBアクセスの必要

ユーザ仮想空間A

実メモリ

ユーザ仮想空間B

実メモリ

メッセージ到着通知

割込み、ポーリング

TLB

仮想 実 ピン

TLB

仮想 実 ピン

方式 : 仮想空間AのDMA領域をOSに依頼して貼付け(起動時一度だけ)

## 方式 : 軽いアドレス変換カーネル

方式 : TLBキャッシュ

ユーザ仮想空間A

方式 、 プログラムモードバス

DMAを使わない方式

ユーザ仮想空間A

| MPI Benchmark                   | MX/Myrinet<br>Myricom<br>10G Myrinet<br>switch | MX/Ethernet<br>Fulcrum<br>10G Ethernet<br>switch | MX/Ethernet<br>Fujitsu<br>10G Ethernet<br>switch | OpenIB with<br>Intel MPI<br>Mellanox<br>InfiniBand |

|---------------------------------|------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------------------------|

| PingPong latency                | 2.4μs                                          | 2.4μs                                            | 2.8μs                                            | 4.0μs                                              |

| One-way data rate<br>(PingPong) | 1204 MByte/s                                   | 1201 MByte/s                                     | 1002 MByte/s                                     | 964 MByte/s                                        |

| Two-way data rate<br>(SendRecv) | 2397 MByte/s                                   | 2162 MByte/s                                     | 1762 MByte/s                                     | 1902 MByte/s                                       |

MX: Myrinet Express: メッセージパッシングソフト

Myri-10G: 10 Gigabit/s, dual protocol NIC

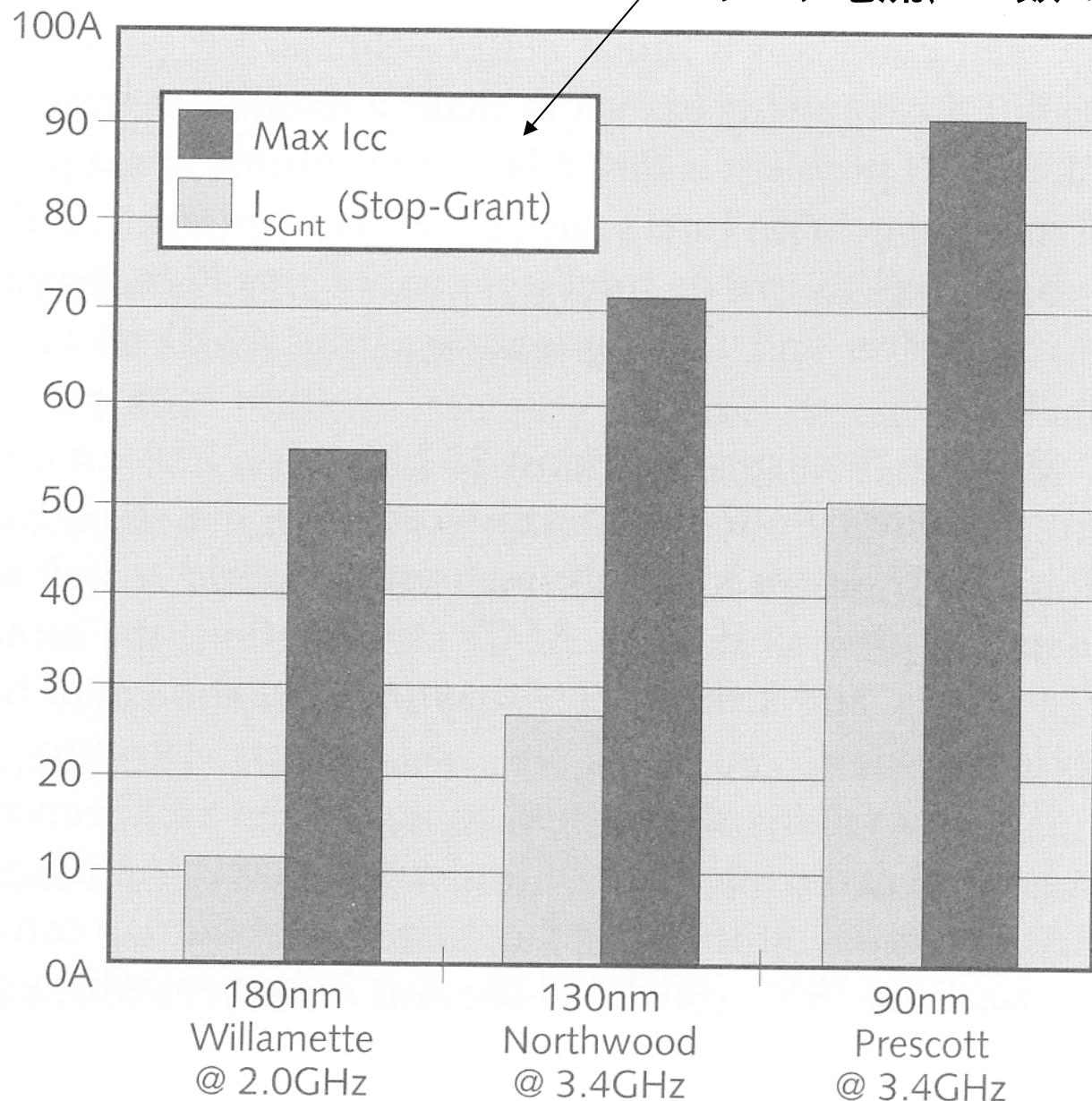

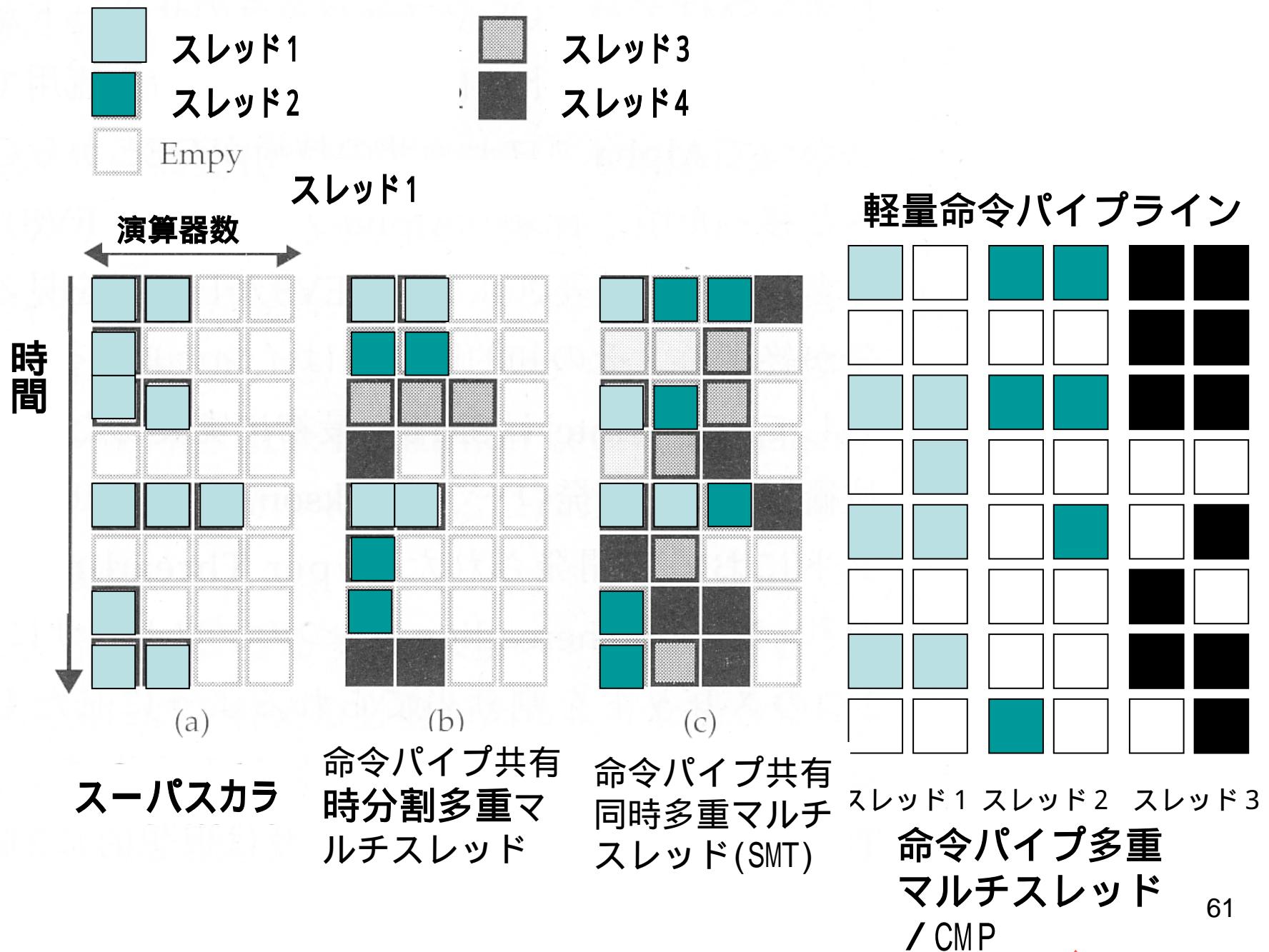

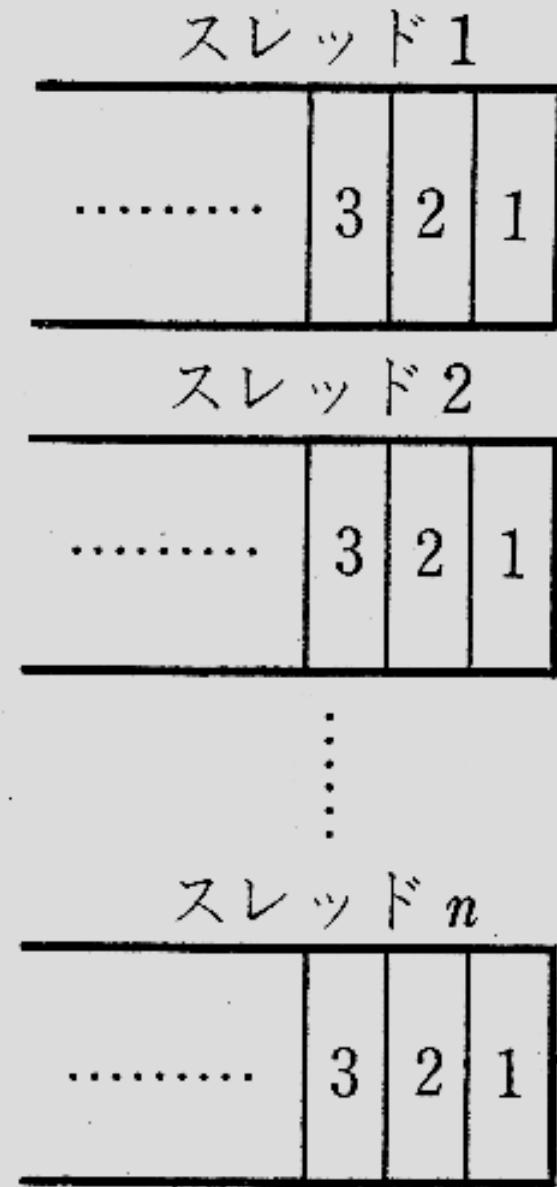

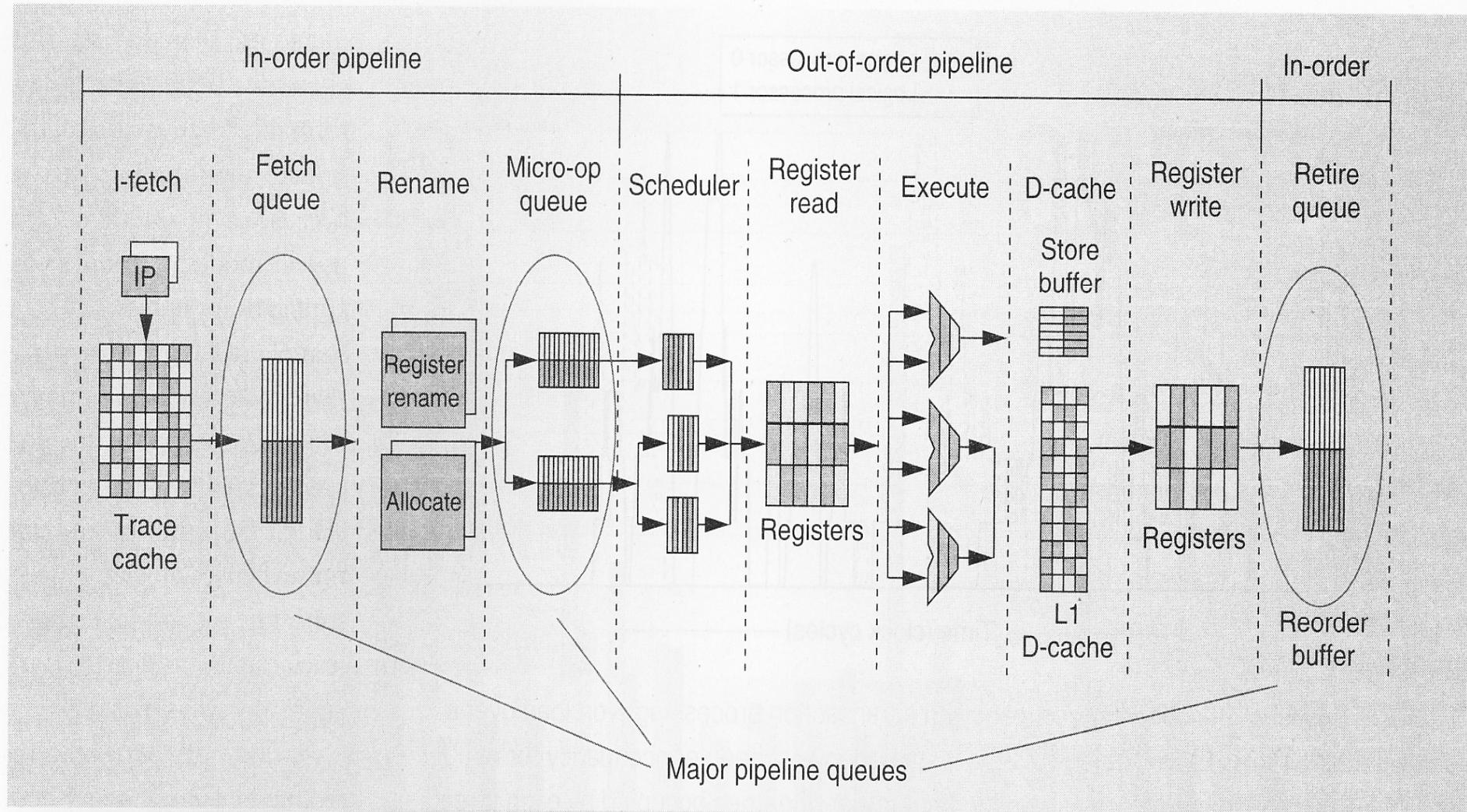

## 7.10 マルチコア型プロセッサ

### 7.10.1 大域並列の利用

- ・パイプライン: 時間並列

- ・乱実行、投機実行による時間並列の高速化

- ・局所並列: スーパスカラ、VLIW

- ・非常に複雑な構造

プログラムカウンタの

近傍にある命令の

並列実行

- ・大域並列: マルチコア型プロセッサ

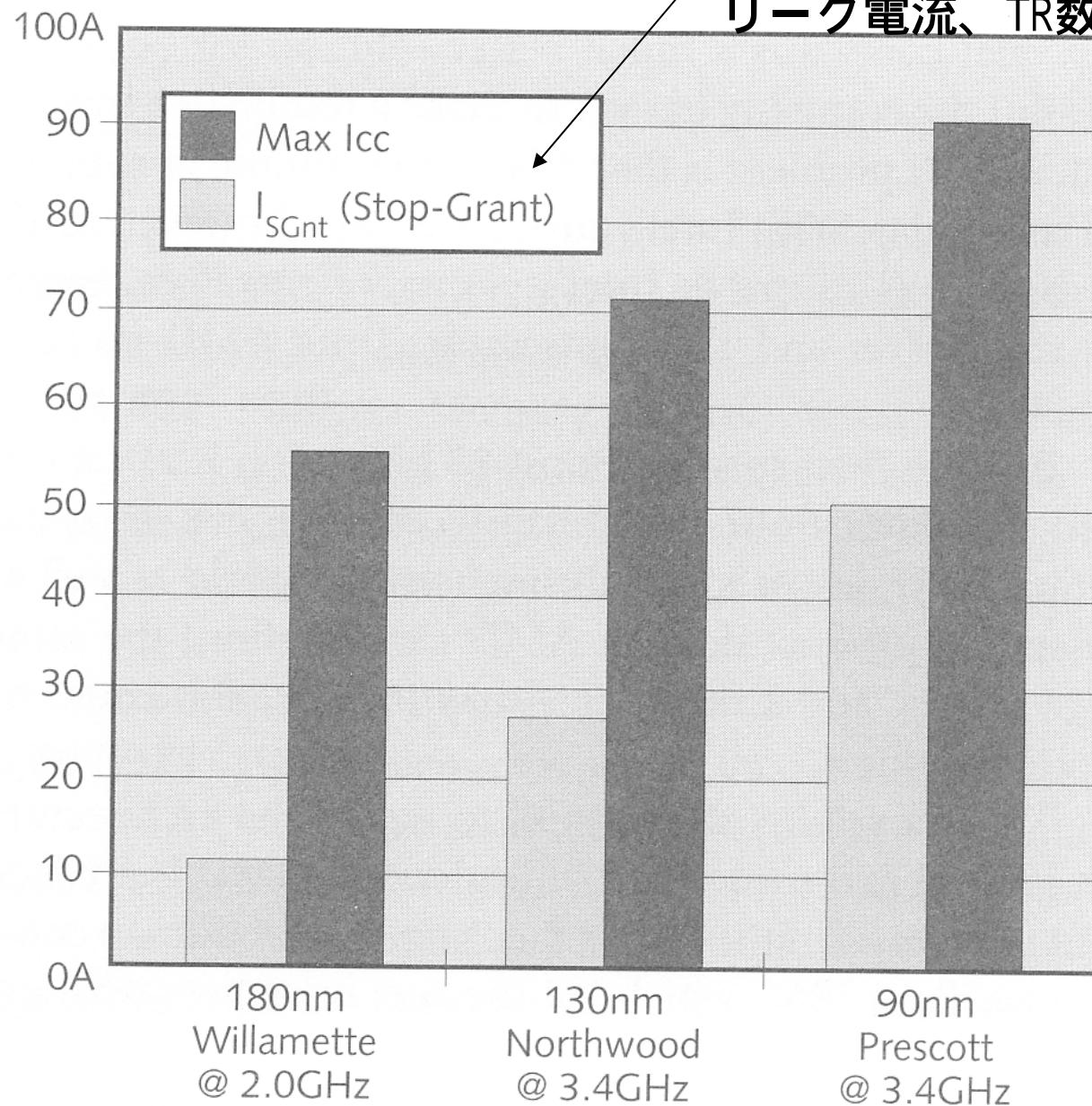

- ・周波数向上が困難

- 深いパイプラインで性能向上: 小さくなった電力の問題: 消費電力  $f^3$

- リーク電流の増大

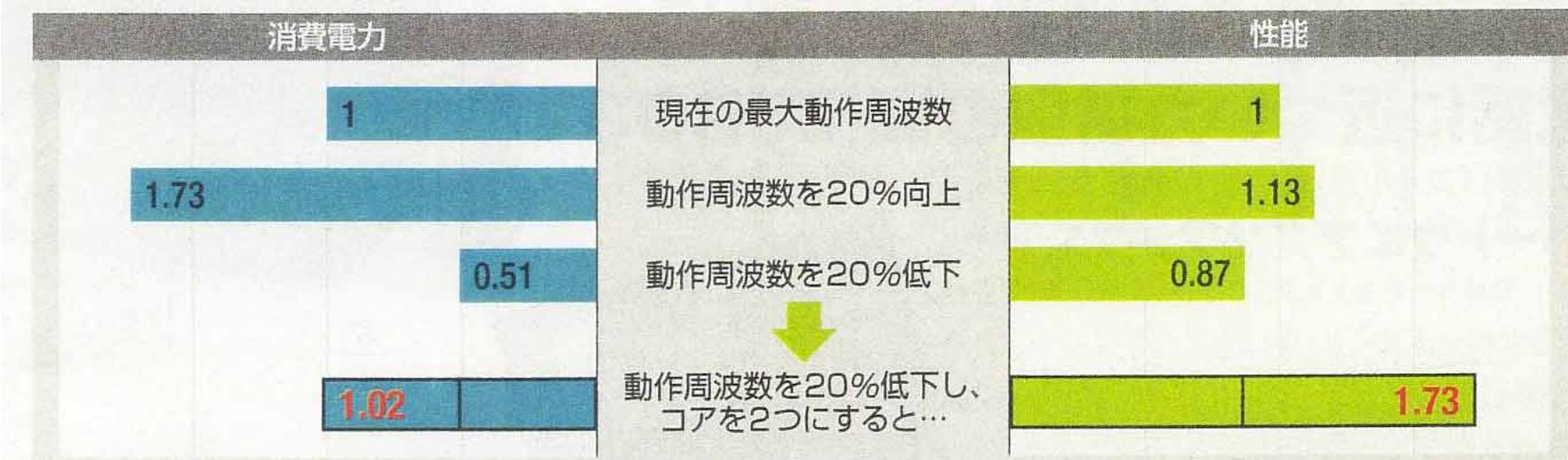

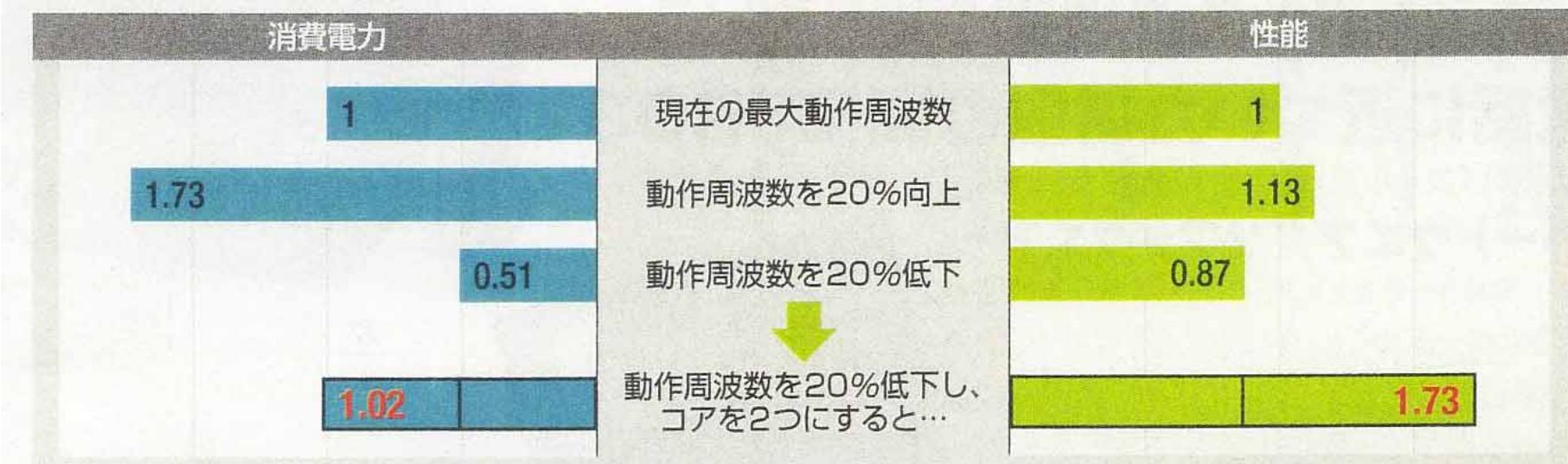

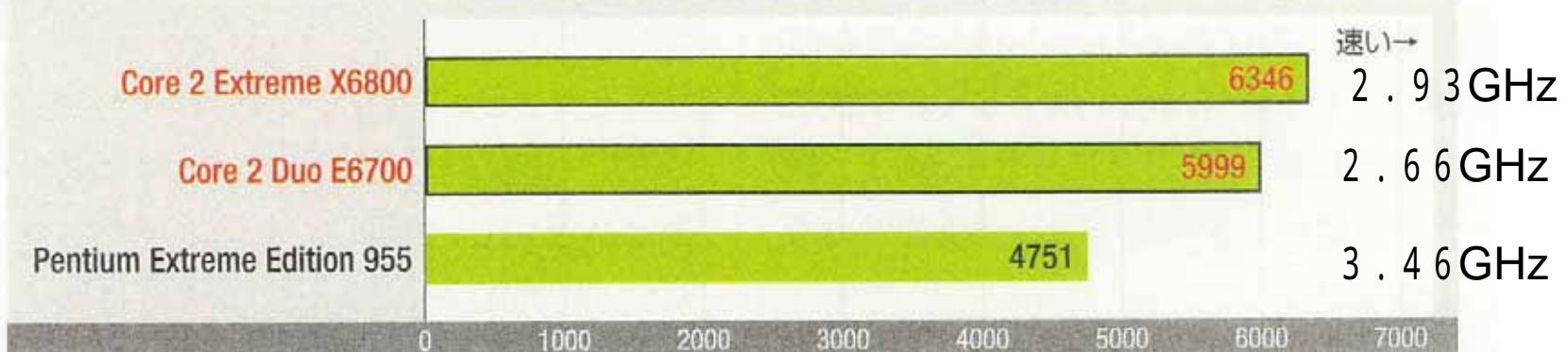

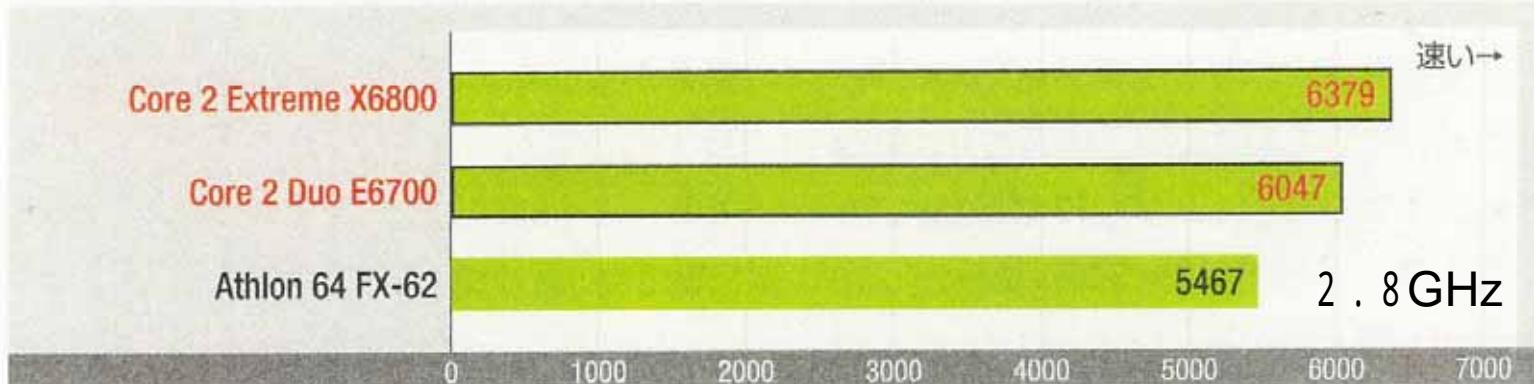

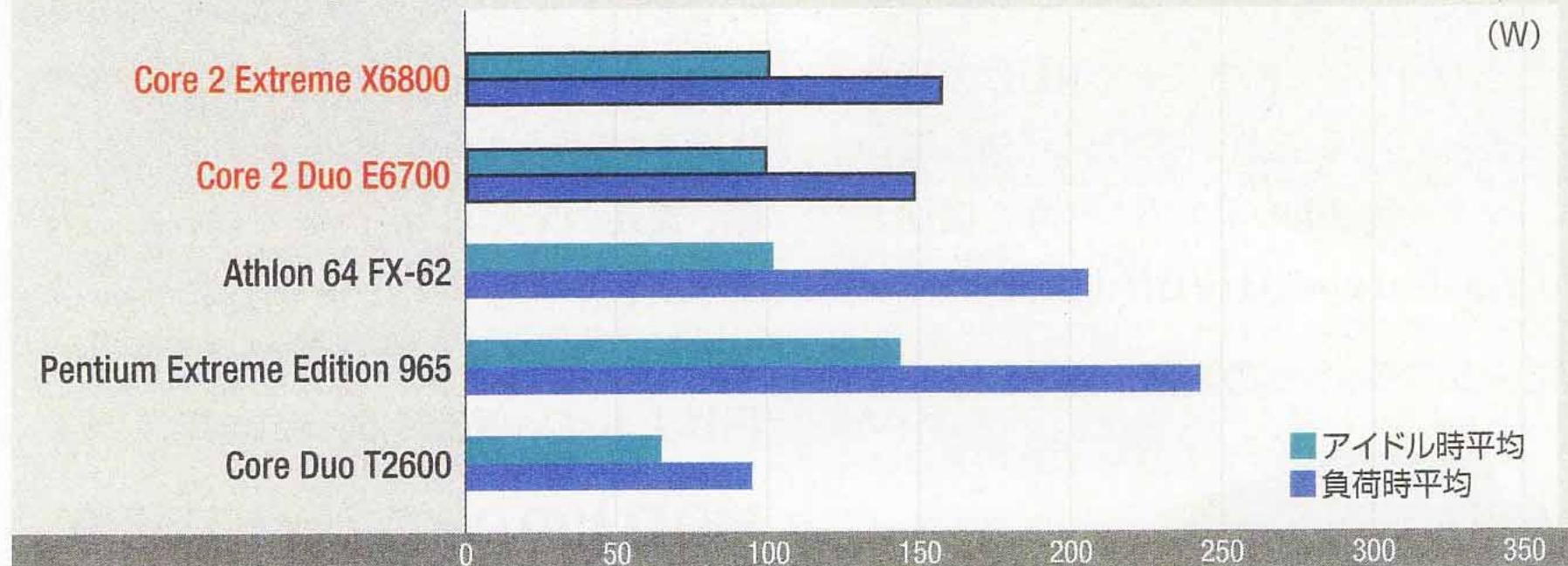

## ●Core 2 Duoの設計思想

現在の動作周波数での性能と消費電力を1としたときの相対値で表示

インテルが開発者会議で発表した値。現在の動作周波数からさらに20%周波数を上げても、性能は1.13倍にしかならないが、消費電力は1.73倍と大幅に増えてしまう。逆に20%周波数を下げると、性能は0.87倍になるが、消費電力は0.51倍とほぼ半減する。それならば、動作周波数を落としてコアを複数にすることで消費電力と性能のバランスをとろうというのがCore 2 Duoの設計思想だ

日経PC 2006.8.14

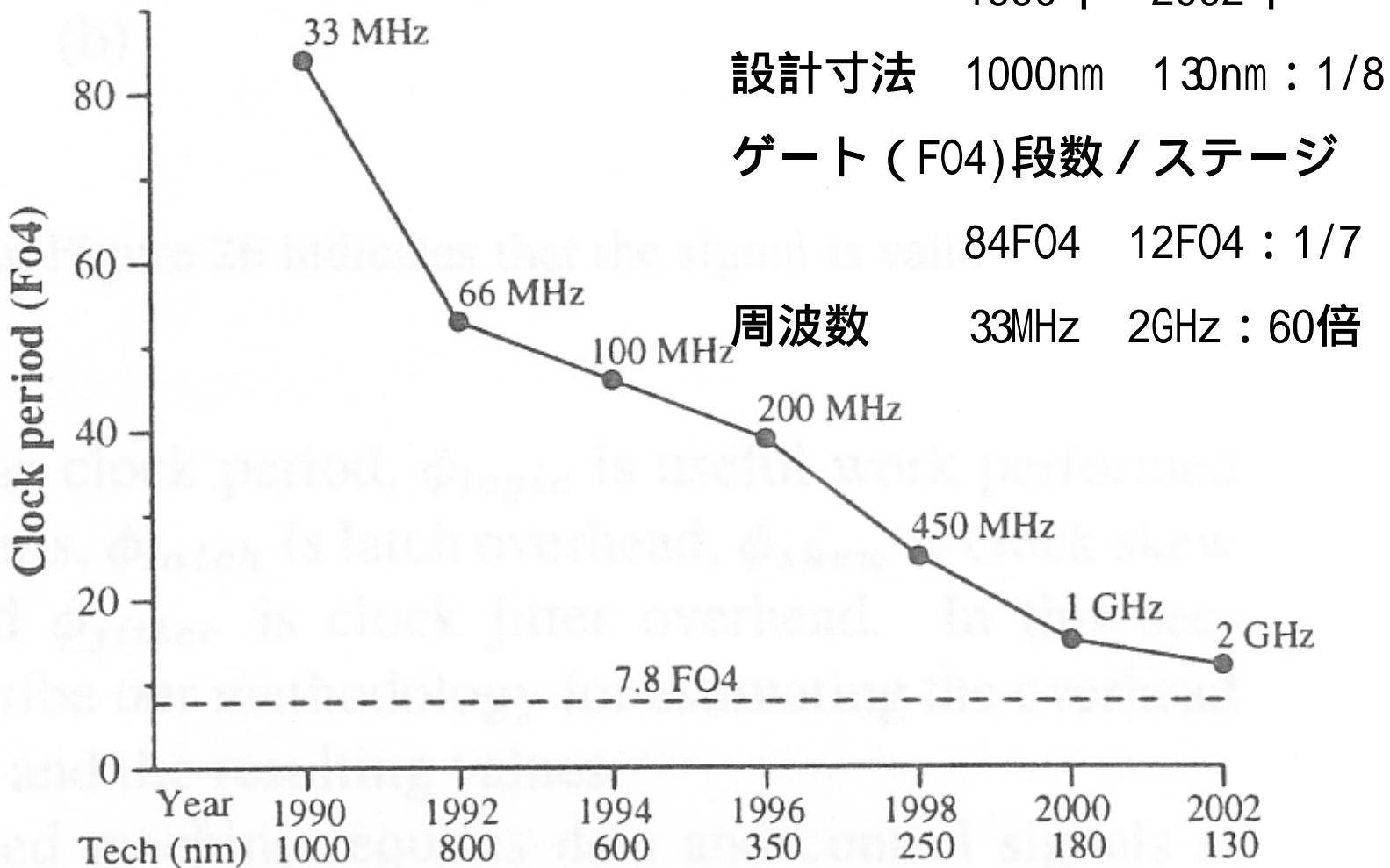

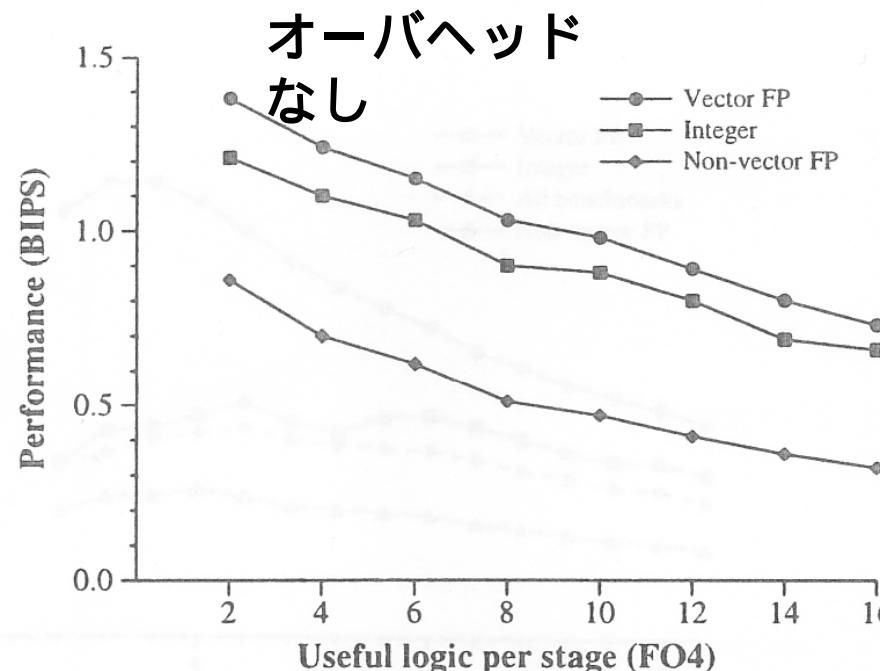

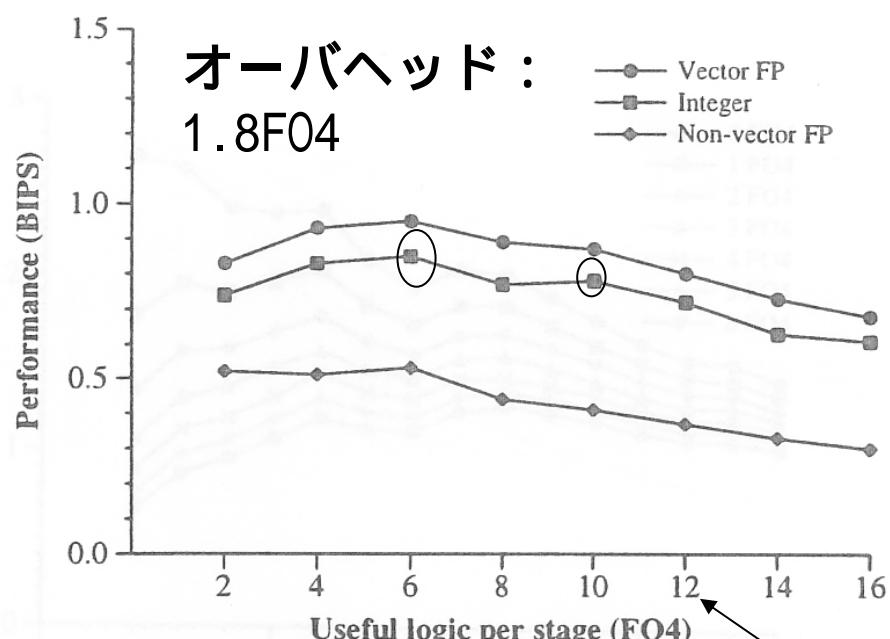

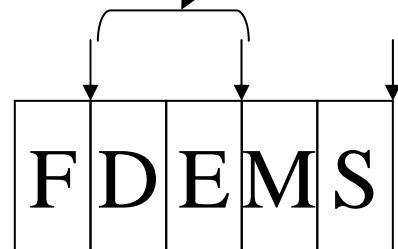

# 深いパイプラインの限界

周波数向上: 40%/年

1990年 2002年

設計寸法 1000nm 130nm : 1/8

ゲート (F04) 段数 / ステージ

84F04 12F04 : 1/7

周波数 33MHz 2GHz : 60倍

N.Joppi et.al., ISCA, 2002

(b) 1ステージの中の

有効ゲート数

オーバヘッド

2FO4

有効ゲート数

D

E

M

S

12FO4

ステージ数 2倍、周波数

1.75倍

F1

F2

D1

D2

E1

E2

M1

M2

S1

S2

6FO4

144

分岐予測ミス :

28FO4 32FO4

10FO4 6FO4 : 9 %性能向上

11.8FO4 7.8FO4 : 周波数1.5倍

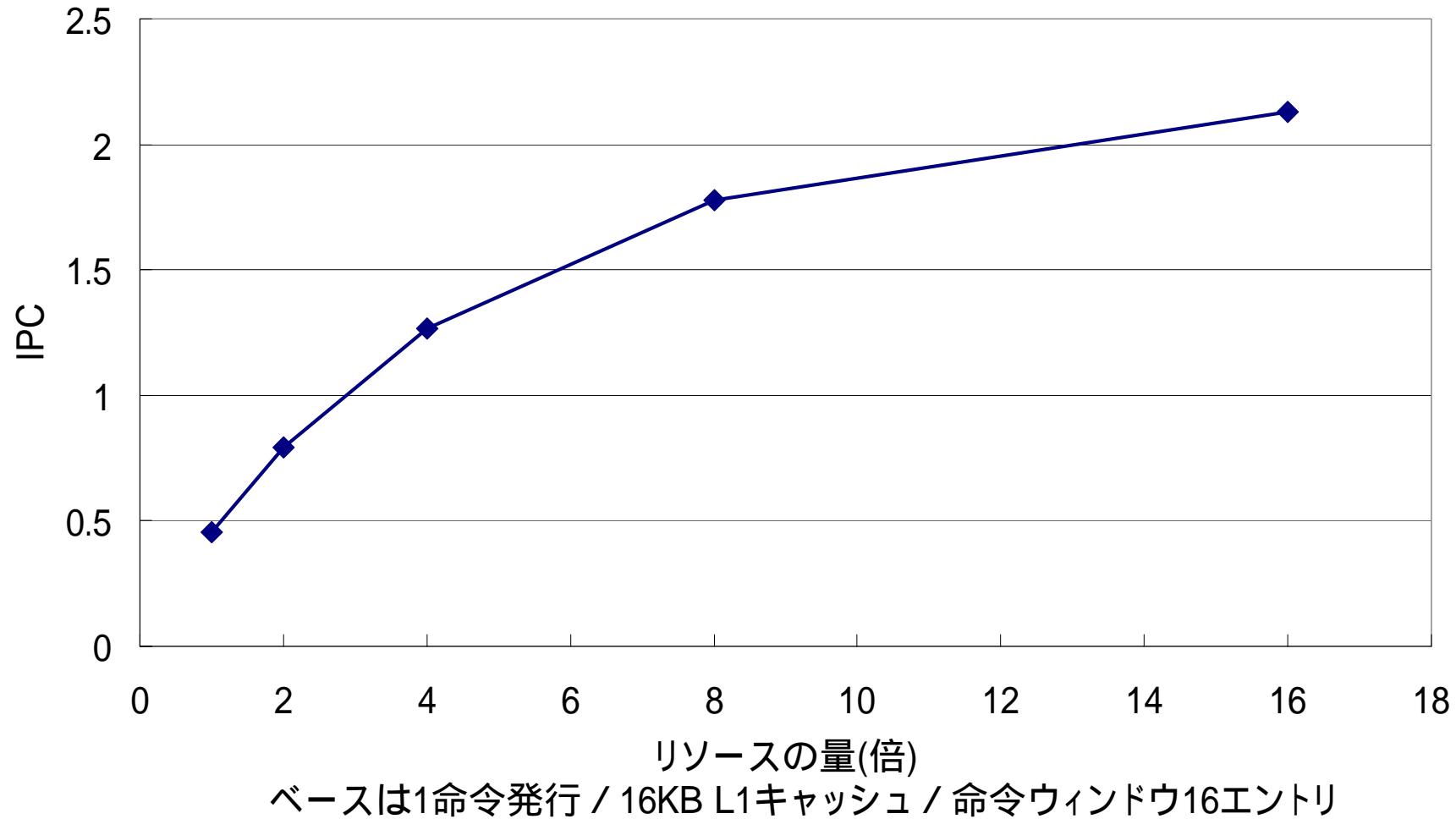

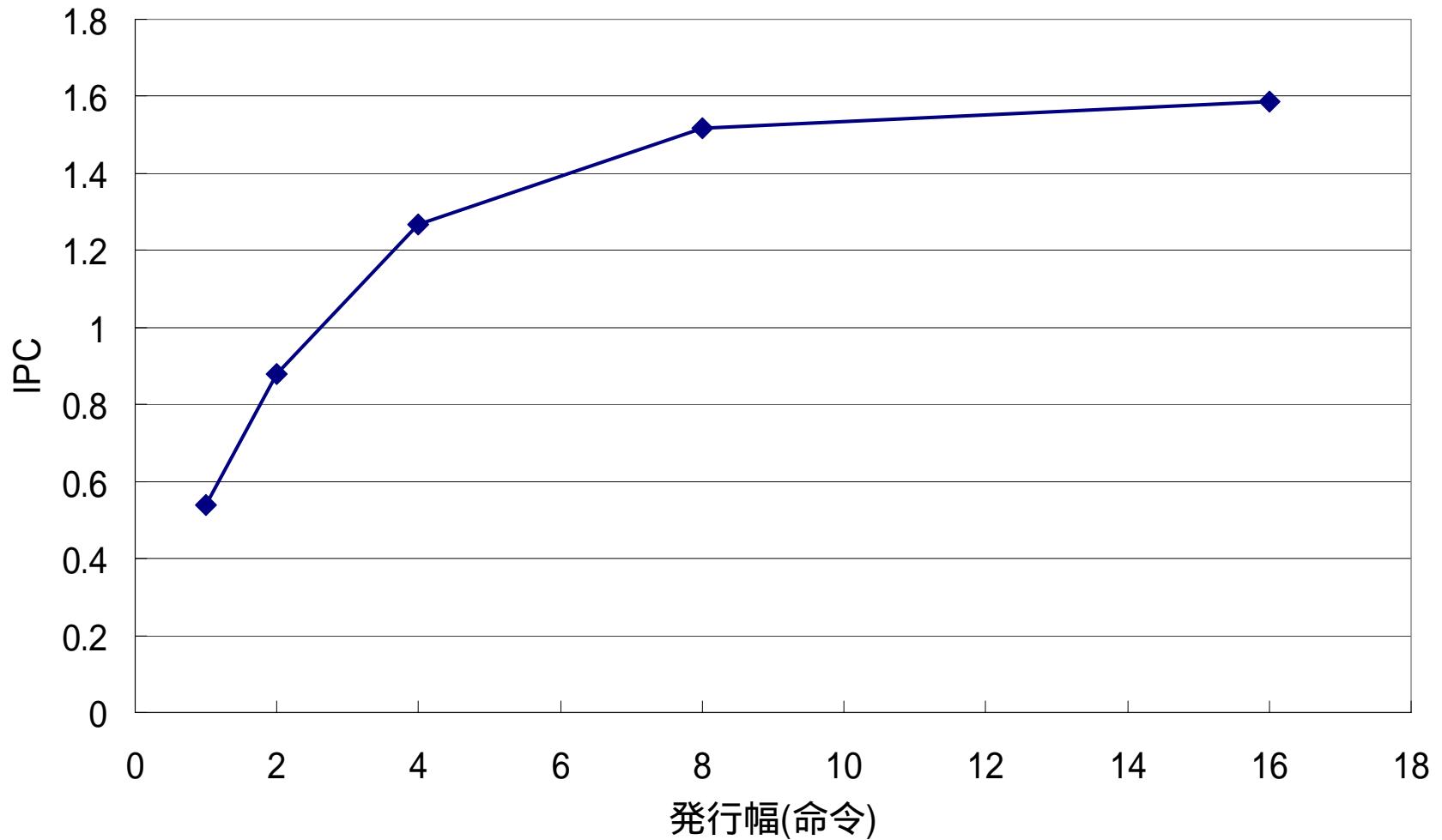

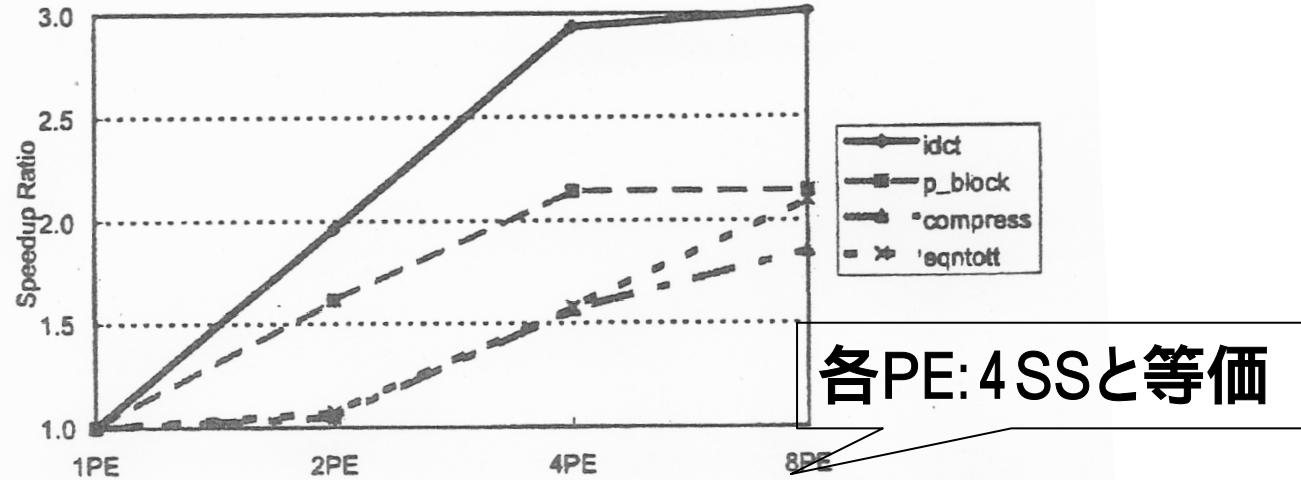

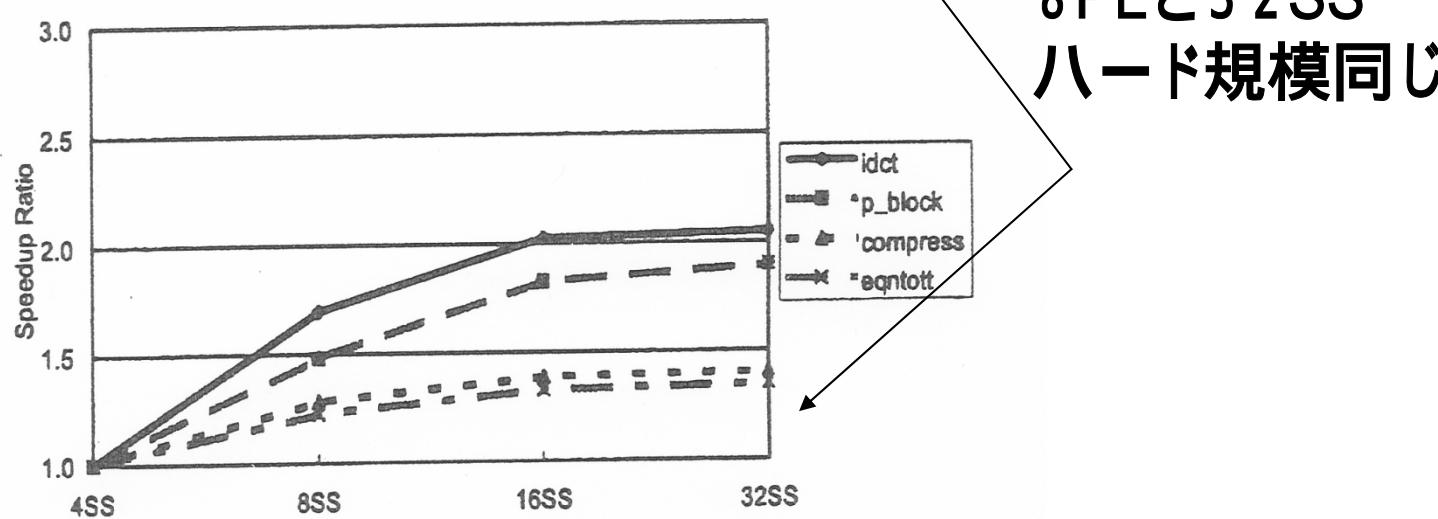

# IPC向上率の鈍化

## ベースアーキテクチャ

命令セット: SimpleScalar PISA (MIPS R10000とほぼ同じ)

発行幅: 4(フェッチ、デコード、発行、ライトバック、コミット幅)

命令ウィンドウ: 64エントリ

機能ユニット: 全ての機能ユニットを発行幅と同じだけ持つ

L1命令キャッシュ: 64KB/32B line/2-way/ヒット・レイテンシ2サイクル

L1データ・キャッシュ: 64KB/32B line/2-way/ヒット・レイテンシ2サイクル

L2キャッシュ: 2MB/64B line/4-way/ヒット・レイテンシ16サイクル

メモリ・アクセス: 128サイクル

gshare: 8Kエントリ

BTB: 2Kエントリ/4-way

分岐予測ミス・ペナルティ: 10サイクル

## 全リソース(L1キャッシュ、PHT、命令ウィンドウ、発行幅)の変更

## 発行幅のみ変更

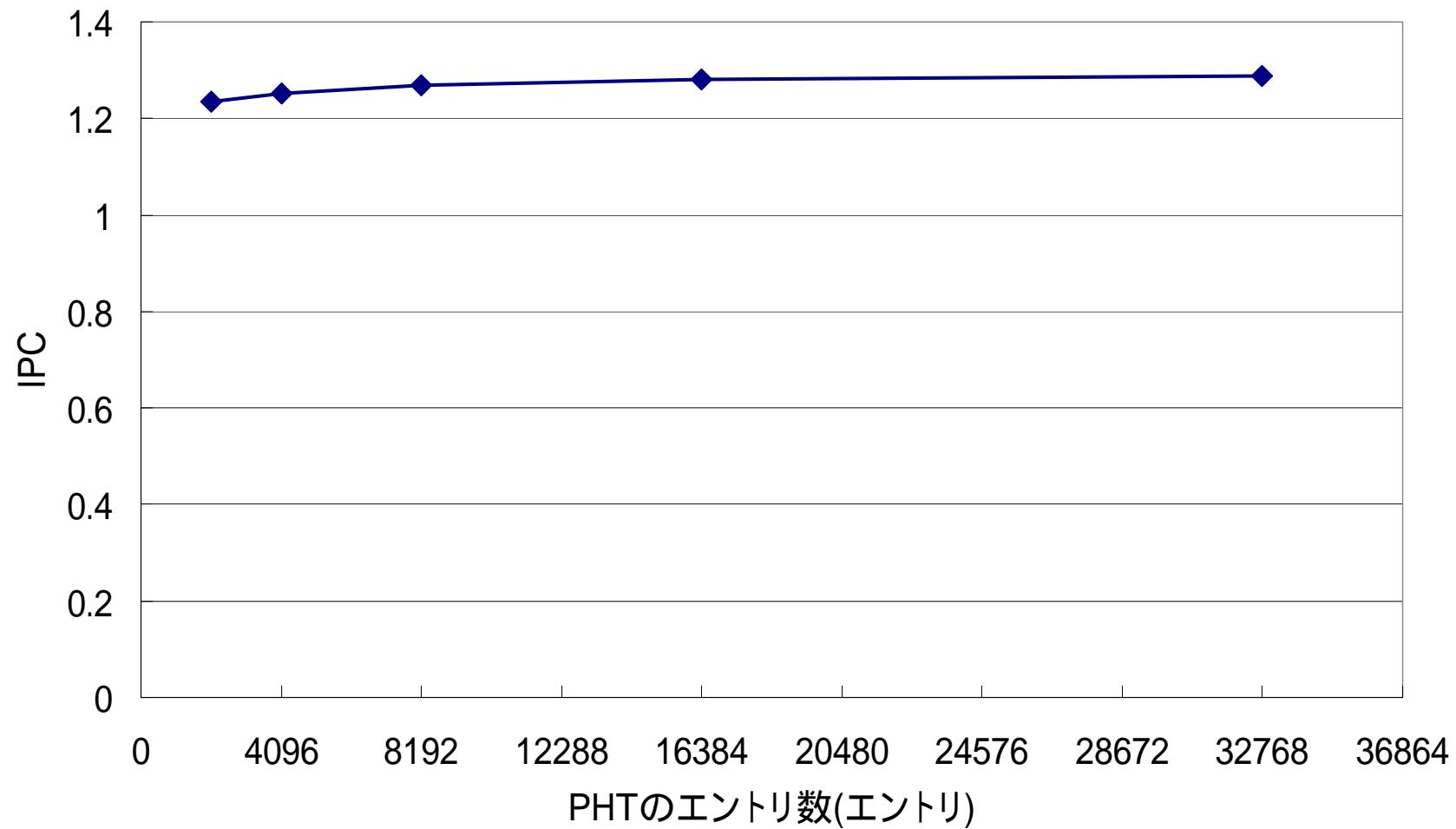

## gshareのPHTのエントリ数のみ変更

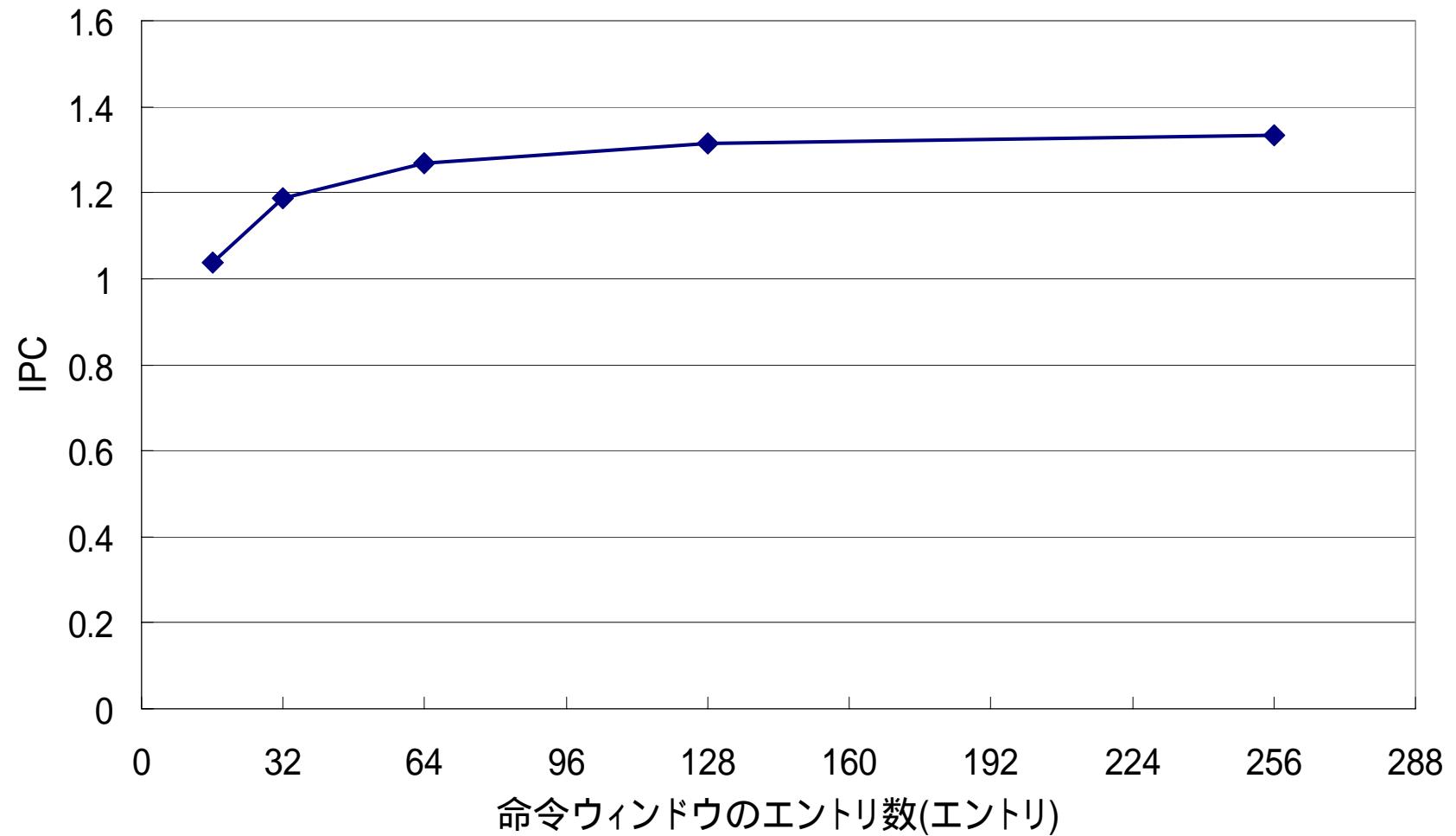

## 命令ウィンドウのエントリ数のみ変更

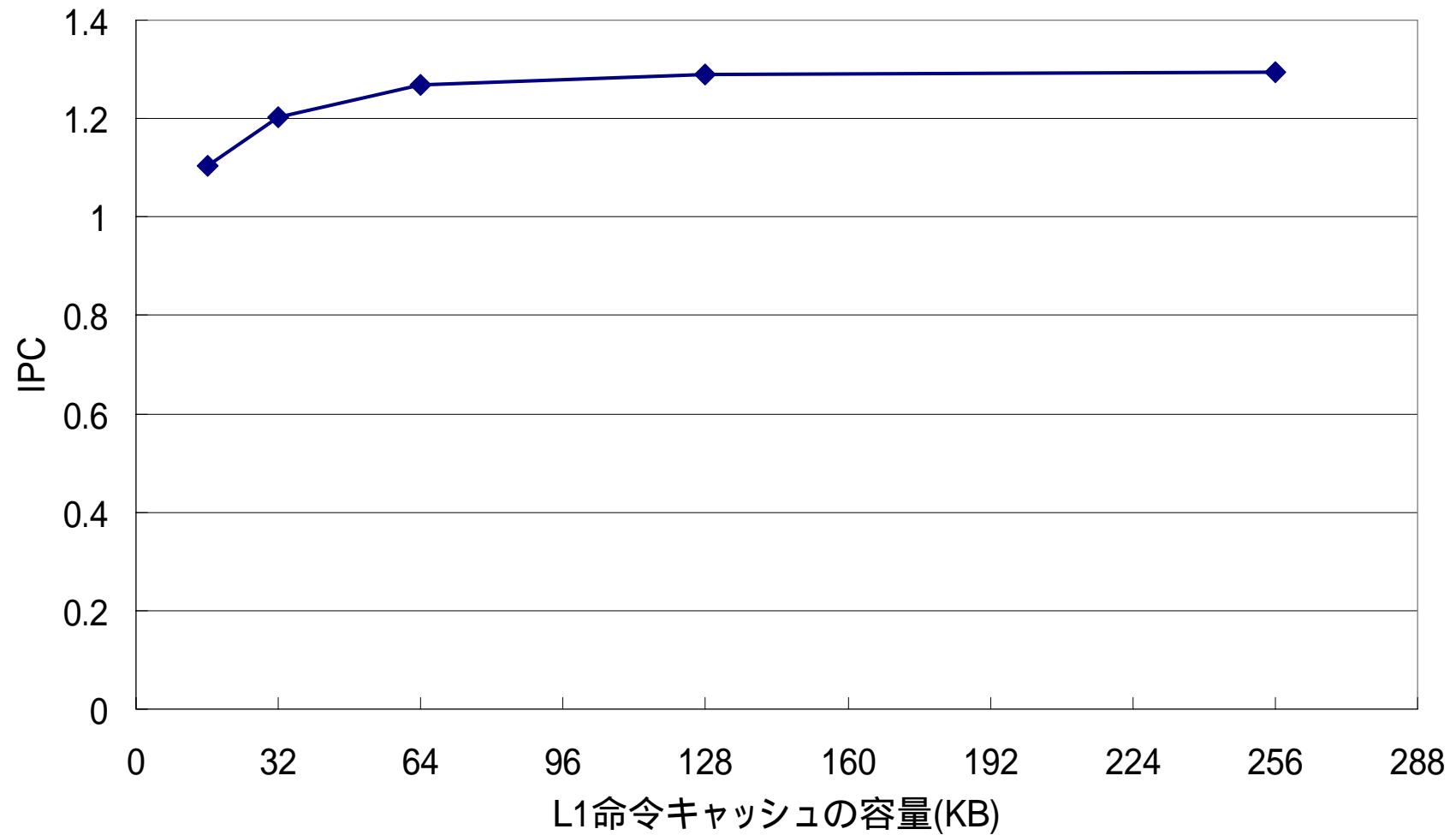

## L1命令キャッシュの容量のみ変更

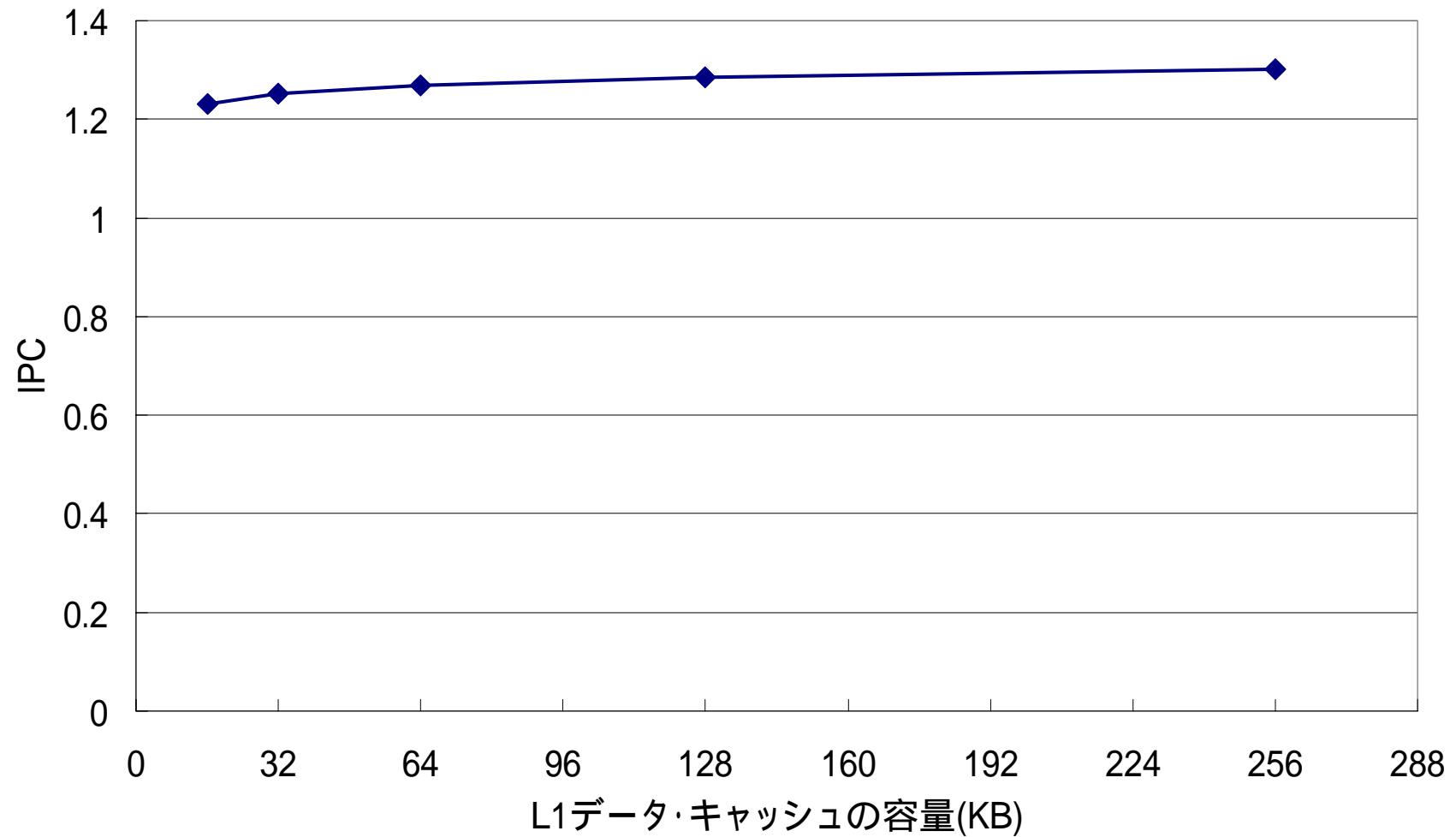

## L1データ・キャッシュの容量のみ変更

# 省電力化

## CMOSの電力消費

・動的

回路がON、OFFするとき  $fCV^2$

・漏れ電流  $V I_{\text{leak}}$

・貫通電流  $f t_{\text{st}} I_{\text{short}} V$

:ゲート動作率、 $f$ :周波数、 $C$ :ゲート総容量、

$V$ :電源電圧、 $t_{\text{st}}$ :スイッチング時間

$$P = f C_L V^2 + V I_{\text{leak}} + f t_{\text{st}} I_{\text{short}} V$$

$$F_{\max} = (V - V_{\text{threshold}})^2 / V \quad V$$

$$I_{\text{leak}} = \exp(-qV_{\text{threshold}}/kT)$$

T.Mudge: Power: A First-Class Architectural Design Constraint, IEEE Computer, pp.52-58, April 2001

# 基本的な考え方

- スイッチング回数を少なくする

- 動作をしない(と予想される)回路には

- クロック供給しない

- 電源を供給しない

- 電源電圧を制御して、必要十分な処理速度で実行

- 電源電圧、周波数を落として並列処理、パイプラインで行う

- 基盤バイアス印加による閾値制御:

- リーク電流削減(スプレッショルドリーク電流)

- 高速部分:低閾値、

- 低速部分や待機時:高閾値(バイアス印加)

- デバイスレベル

低電源電圧化、低ゲート容量化、基盤バイアス制御

- 回路レベル

パストランジスタ論理

ゲート付きクロック

グリッチの削減

動的電源遮断

非同期回路

- アーキテクチャレベル

データパスの最適化: 必要な演算幅の決定など

並列処理、パイプライン処理

キャッシュメモリ

バス: アドレスの反射2進符号化、データ圧縮

- OS、コンパイラ、アルゴリズムレベル

符号化

ビット変化の少ないコード生成

動的電源電圧制御

動的周波数制御

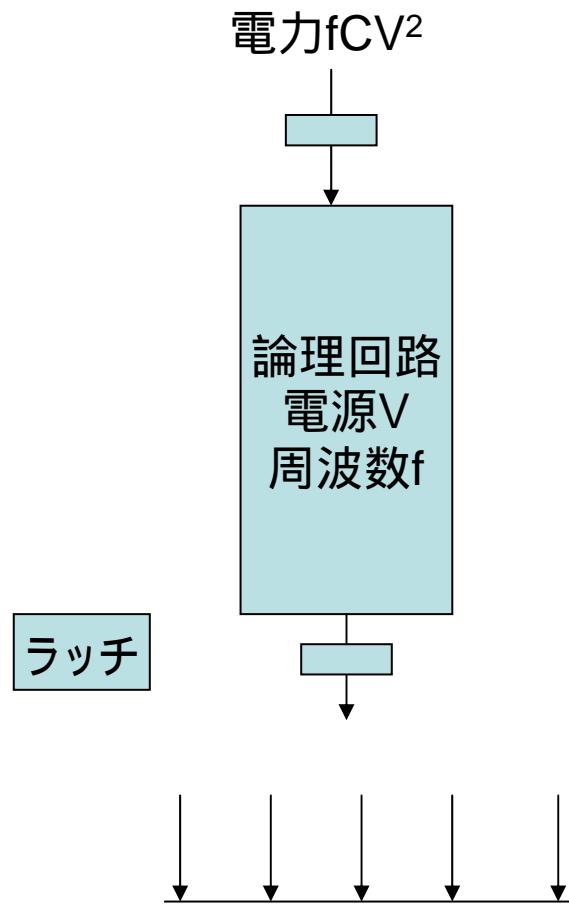

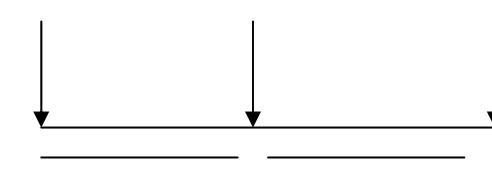

# 並列処理の導入

## 並列処理

電力  $2(f/2C(V/2)^2)$

$fCV^2/4$

論理回路

電源  $V/2$

周波数  $f/2$

1/2fごとに2つの演算

## パイプライン処理

電力  $fCV^2/2$

1/fごとに1つの結果

周波数  $f$ 、電源  $V$  : 電力 :  $fV^2$

ボルテージスケーリング

周波数  $f/2$ 、電源  $V/2$  : 電力 :  $1/8$

分岐ミスのとき

パイプラインステージ統合

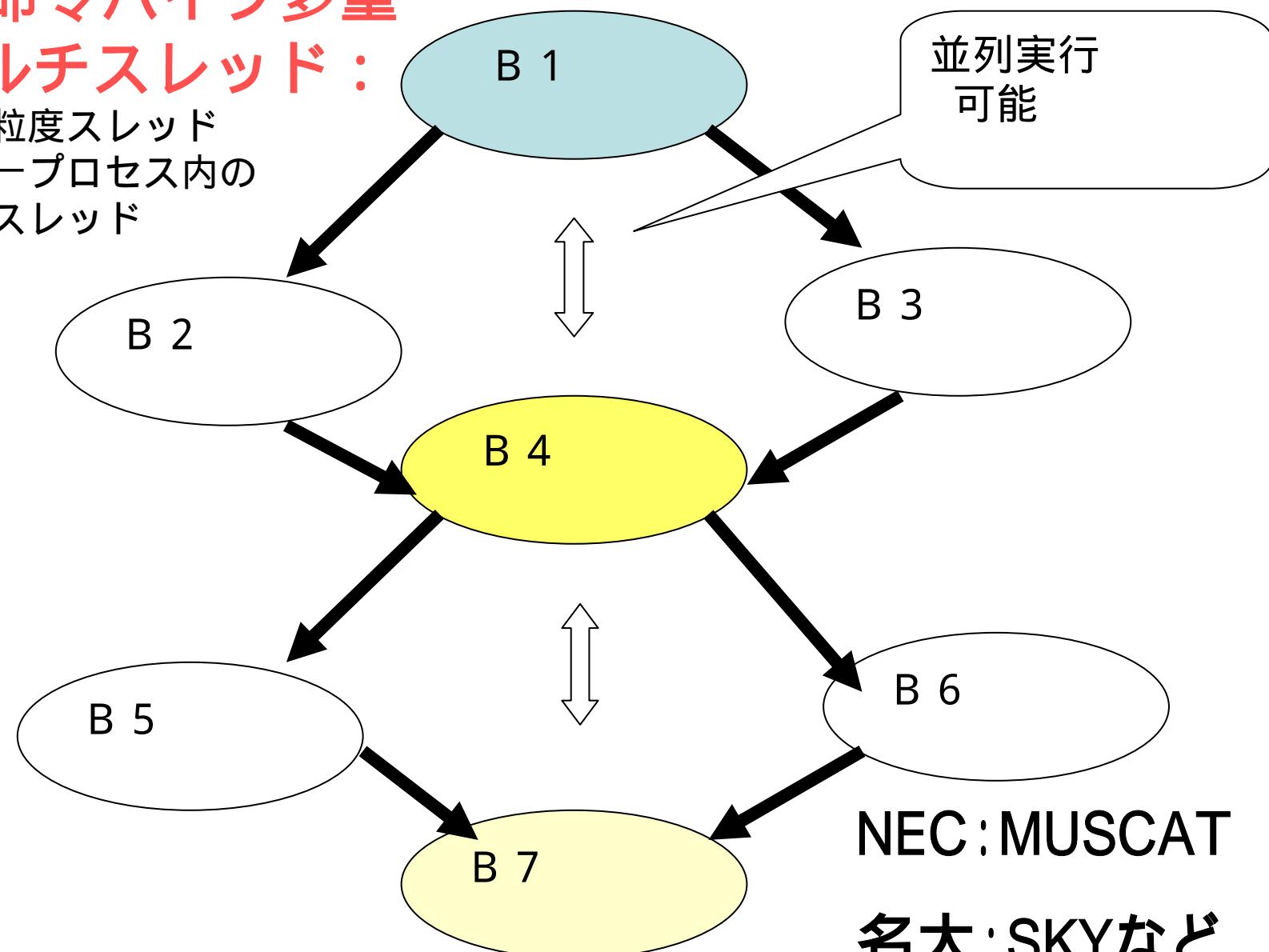

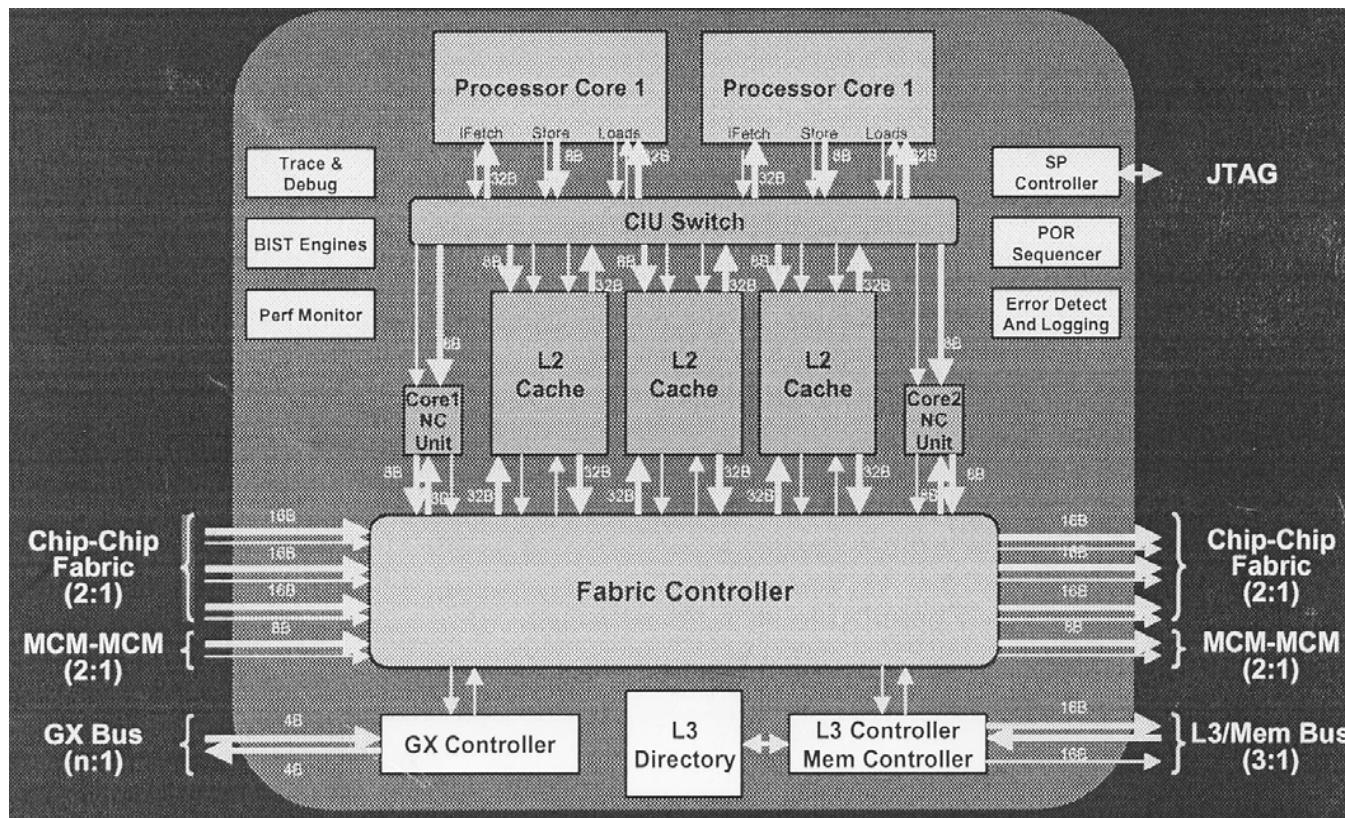

周波数  $f/2$ 、電源  $V$  : 電力 :  $1/2$