# 第3章

## SIMDコンピュータ

### 3.1 SIMD方式の原理

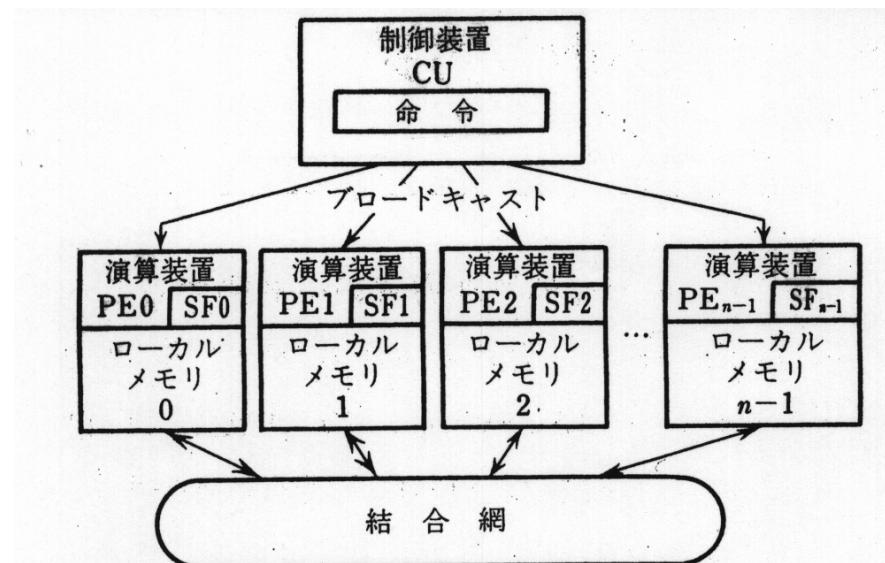

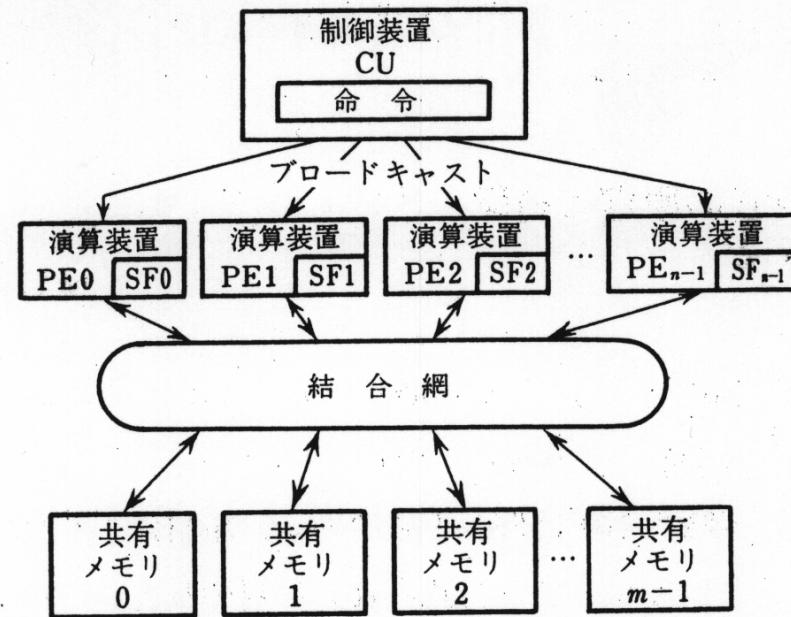

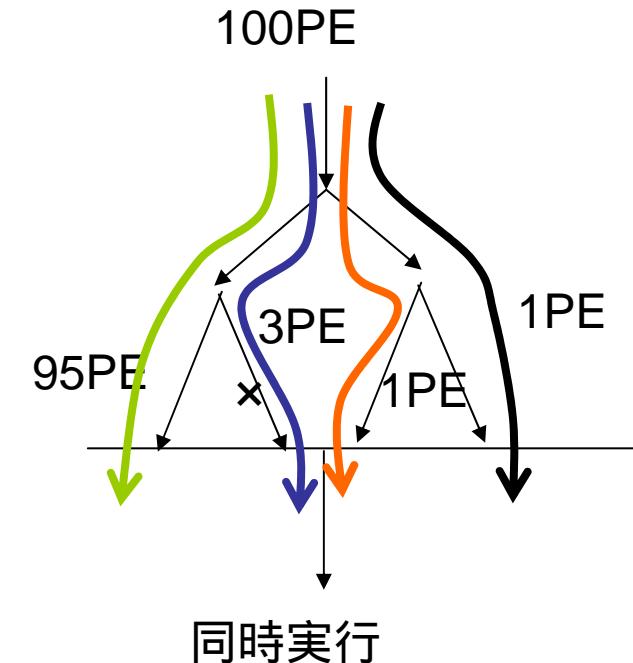

#### 3.1.1 原理

制御装置（CU）から発せられた命令：

同一構造を有する多数の演算装置（PE）に

同時にブロードキャスト

メモリ共有型とメモリ非共有型

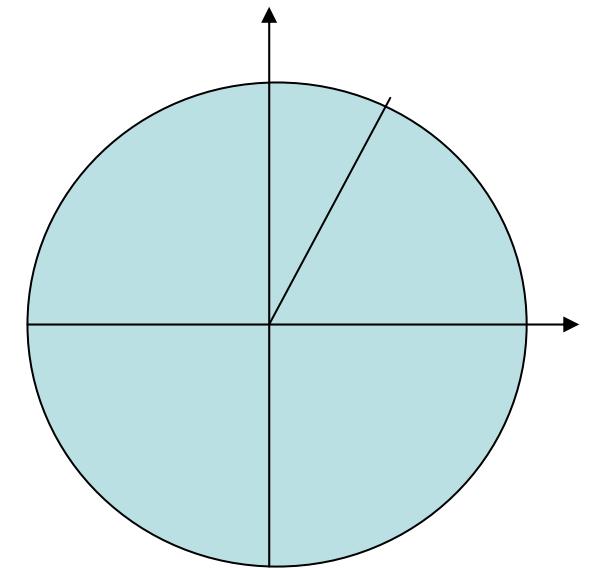

演算実行の抑止

(a) メモリ非共有

(b) メモリ共有

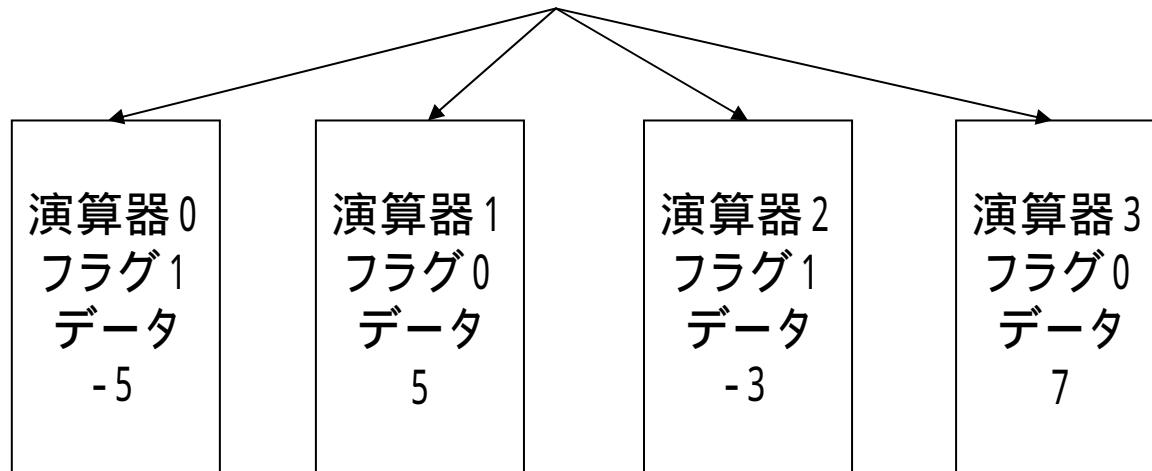

# SIMD演算の例: 絶対値の計算

正のデータを持っているもの 抑止フラグ0

負のデータを持っているもの 抑止フラグ1

0 - (データ)の一斉実行

引き算せよ

5

5

3

7

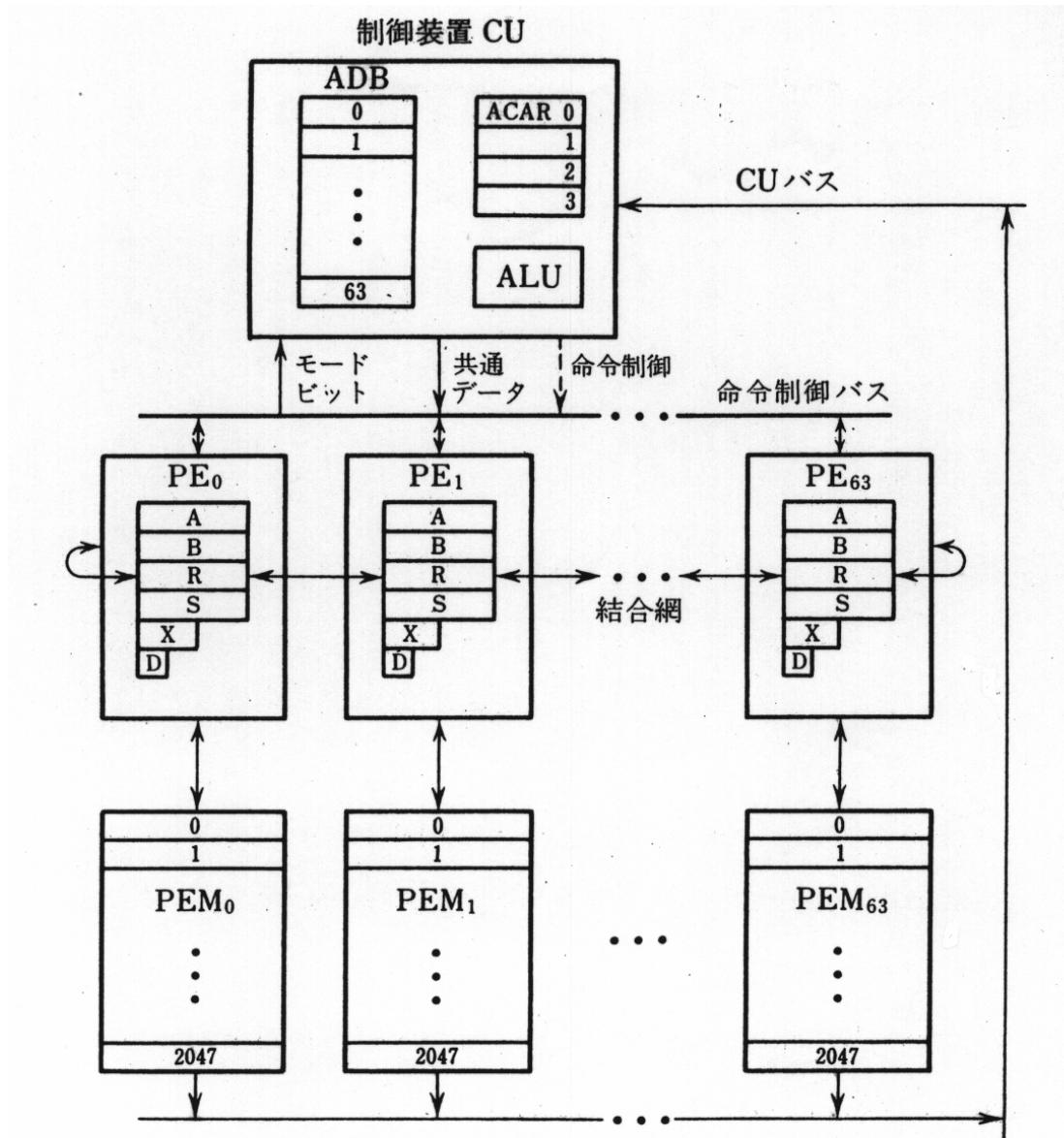

### 3.1.2特徴

演算装置の簡略化

細粒度並列処理指向

定型処理指向

分岐少ない方がよい

命令同期型プログラミング

全PE終了後次命令発行

プログラミングの制約

標準的なプログラミング

生産性が向上？

コンパイラによる最適化

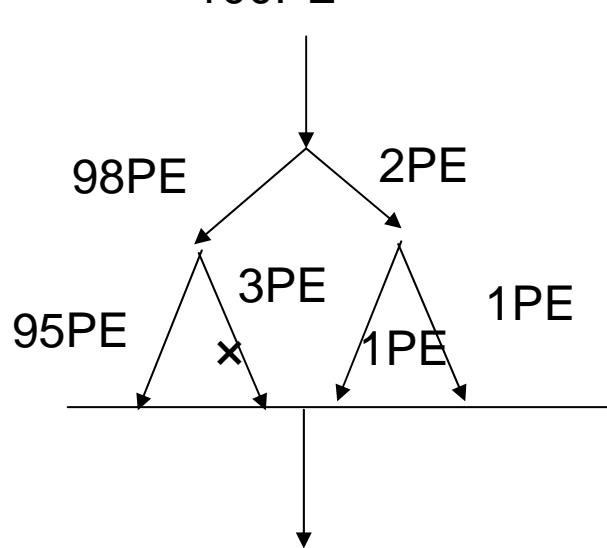

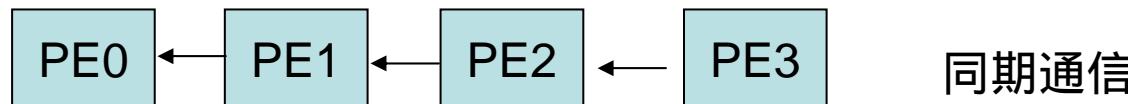

全PEが同時終了するよう，無資源競合

分岐のない

場合2演算

100PE

2PE

98PE

3PE

1PE

分岐のある

場合6演算

### 3.1.3 SIMD方式の柔構造化

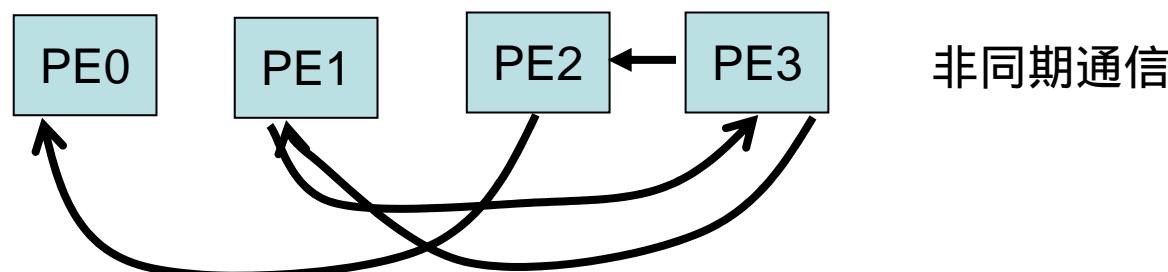

#### 通信の非同期化

SPMD化:Single Program Multiple Data

分岐点から合流点までをPEで非同期実行

MIMD化

SIMDは歴史的な役割を終えたのか？

# 3 . 2 ILLIAC IV

ILLIACIV：イリノイ大学で設計

バロース社が開発

歴史的な並列コンピュータ

元々256台のPEの予定

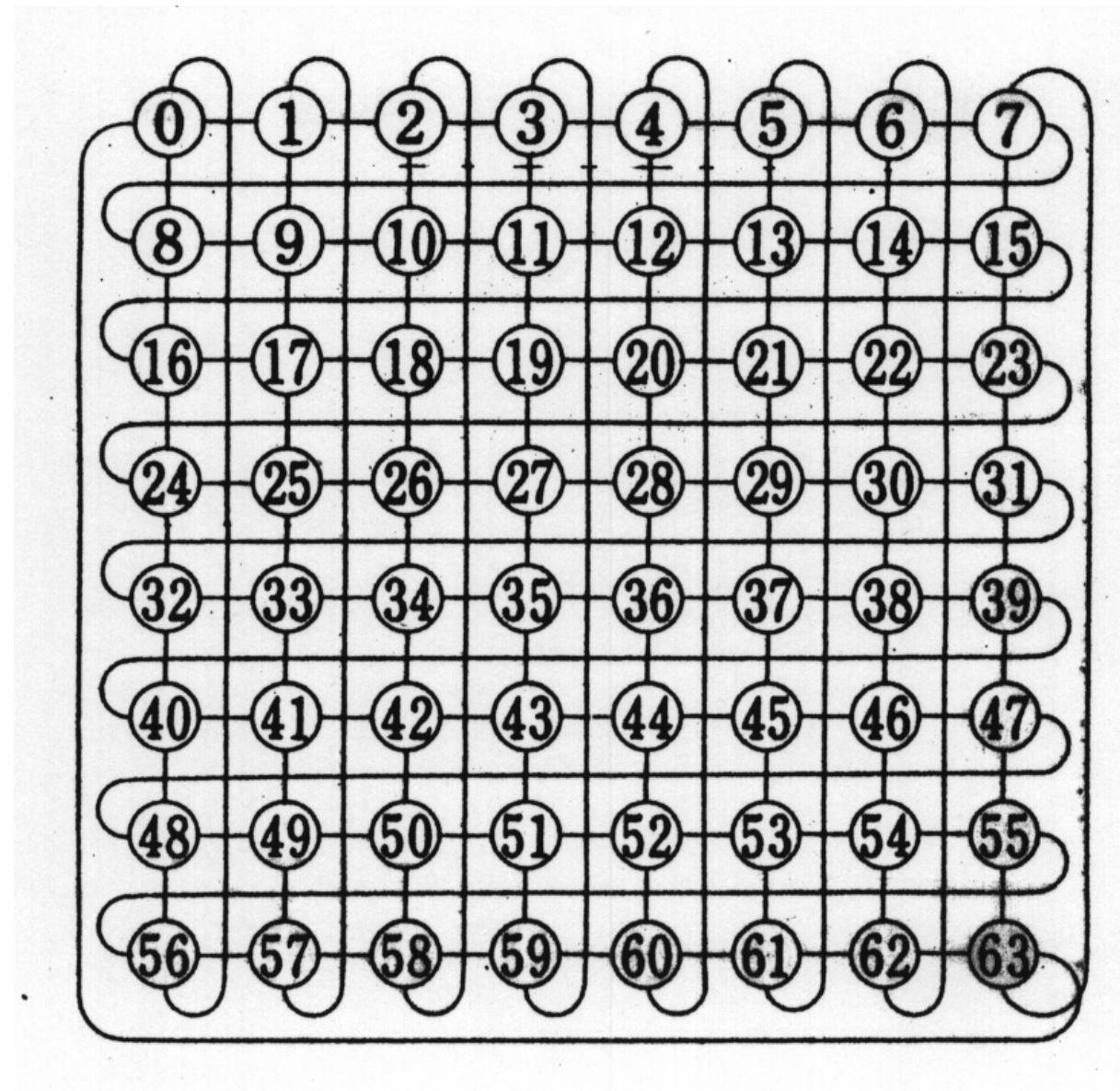

64台の演算装置（PE）

疑似トーラス

大学紛争に巻き込まれた

### 3 . 3 B S P

#### ( 1 ) BSPの基本方式

- 16台の同一構造をした演算装置PE

( 浮動小数点加算・乗算 : 320nsec、除算 :

1.28 μ sec)

#### • メモリ共有方式

16を超える最小素数 17台のメモリバンク

#### • クロスバスイッチ網

#### 計画された2号機

512台のPE, 521台のメモリバンク

行列(4行5列)

|          |          |          |          |          |

|----------|----------|----------|----------|----------|

| $a_{11}$ | $a_{12}$ | $a_{13}$ | $a_{14}$ | $a_{15}$ |

| $a_{21}$ | $a_{22}$ | $a_{23}$ | $a_{24}$ | $a_{25}$ |

| $a_{31}$ | $a_{32}$ | $a_{33}$ | $a_{34}$ | $a_{35}$ |

| $a_{41}$ | $a_{42}$ | $a_{43}$ | $a_{44}$ | $a_{45}$ |

要素

|          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| $a_{11}$ | $a_{21}$ | $a_{31}$ | $a_{41}$ | $a_{12}$ | $a_{22}$ | $a_{32}$ | $a_{42}$ | $a_{13}$ | $a_{23}$ | $a_{33}$ | $a_{43}$ | $a_{14}$ | $a_{24}$ | $a_{34}$ | $a_{44}$ | $a_{15}$ | $a_{25}$ | $a_{35}$ | $a_{45}$ |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

$a = 0 \quad 1 \quad 2 \quad 3 \quad 4 \quad 5 \quad 6 \quad 7 \quad 8 \quad 9 \quad 10 \quad 11 \quad 12 \quad 13 \quad 14 \quad 15 \quad 16 \quad 17 \quad 18 \quad 19$

$\mu = 0 \quad 1 \quad 2 \quad 3 \quad 4 \quad 5 \quad 6 \quad 0 \quad 1 \quad 2 \quad 3 \quad 4 \quad 5 \quad 6 \quad 0 \quad 1 \quad 2 \quad 3 \quad 4 \quad 5$

$\alpha = 0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 1 \quad 1 \quad 1 \quad 1 \quad 1 \quad 1 \quad 2 \quad 2 \quad 2 \quad 2 \quad 2 \quad 2 \quad 3 \quad 3$

( a )

|         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|

| PE<br>0 | PE<br>1 | PE<br>2 | PE<br>3 | PE<br>4 | PE<br>5 |

|---------|---------|---------|---------|---------|---------|

演算装置 (PE)

( b )

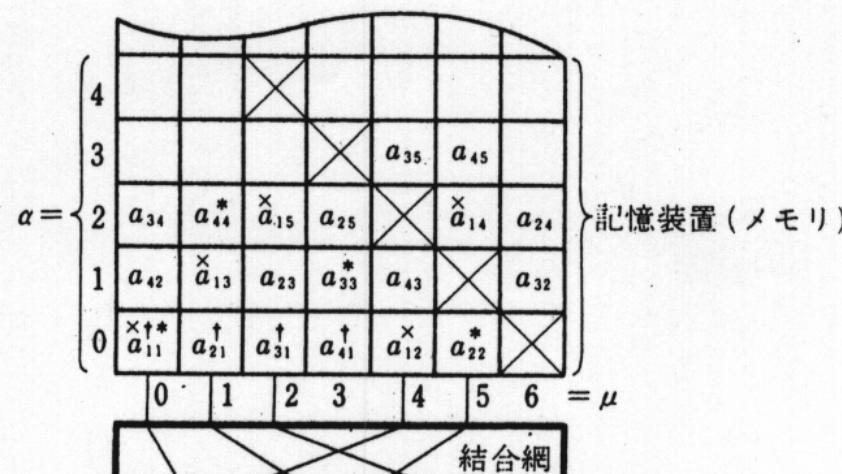

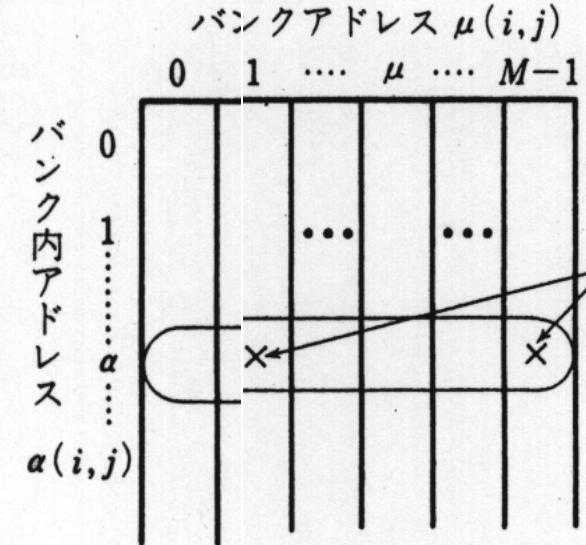

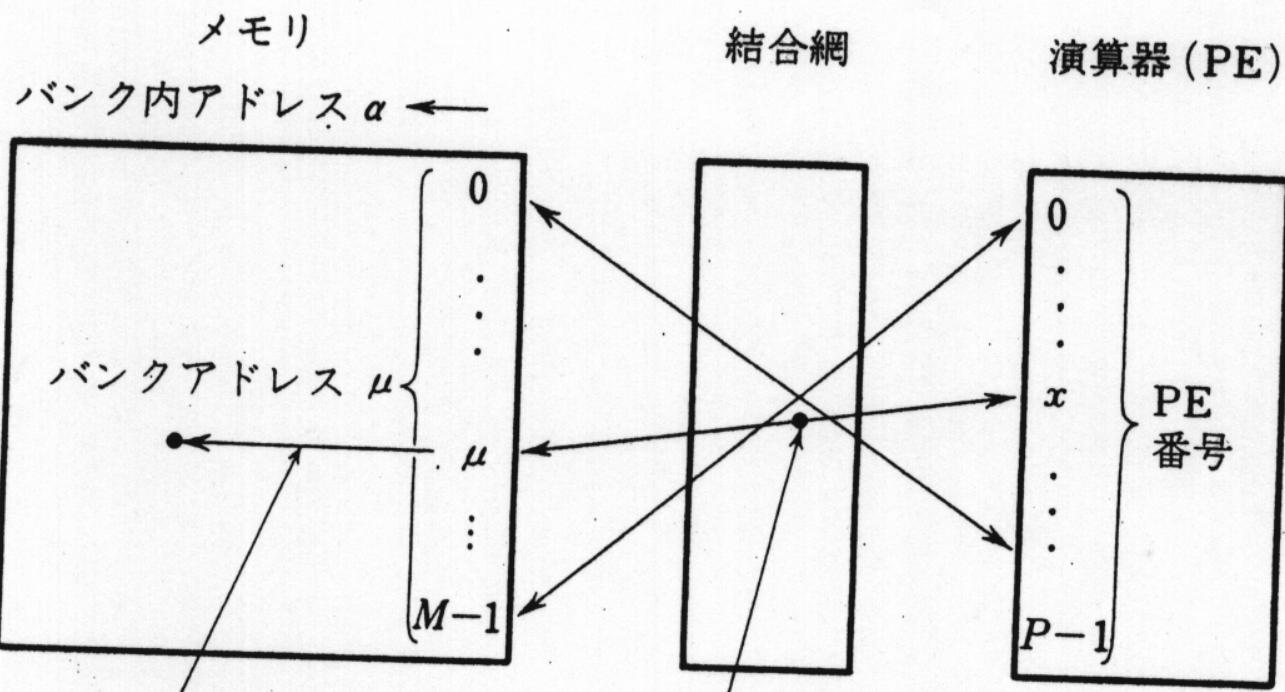

## ( 2 ) BSPのメモリ構成

I 行 J 列の 2 次元配列 A(i, j)

A の要素  $a_{i,j}$  に与える 1 次元アドレス :

$$a = j * I + i + \text{Base} \quad (1)$$

PE 台数 P を越える最小の素数 M

メモリバンク数

メモリアクセス

バンクアドレス  $\mu(i, j)$  、

バンク内アドレス  $\alpha(i, j)$

$$\mu(i, j) = (j * I + i + \text{Base}) \bmod M \quad (2)$$

$$\alpha(i, j) = \lfloor (j * I + i + \text{Base}) / P \rfloor \quad (3)$$

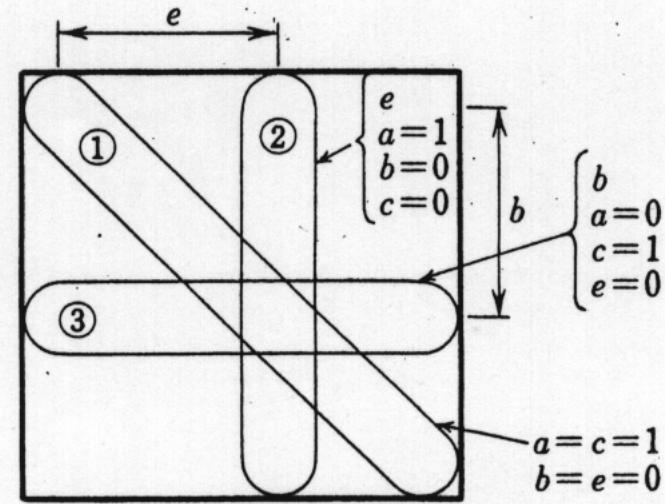

線形Pベクトル

$$V(a, b, c, e) = \{A(i, j) : i = aX + b, j = cX + e, 0 \leq X < P\} \quad (4)$$

$a=c=1, b=e=0$  : 行列Aの対角要素

$a=1, b=c=0$  : 列要素

$a=0, c=1, e=0$  : 行要素

X : 線形Pベクトルの要素番号

$$\mu(X) = (dX + B) \bmod M \quad (5)$$

$$(X) = \lfloor (dX + B) / P \rfloor \quad (6)$$

( a ) 2次元アドレス

( b ) 線形  $P$ -ベクトル

ただし、 $d=a+cI$ ,  $B=b+eI+Base$  ( 7 )

「定理」  $d$  と  $M$  が互いに素である時 ( $M$  は素数であるので、 $d$  が  $M$  の倍数でない時)、線形  $P$  ベクトルの全ての要素を  $P$  個の PE でバンク競合なしに同時にアクセスできる。

「証明」 いま、線型  $P$  ベクトルのある要素  $X_1$  と  $X_2$  が同一バンクに割り付けられたとすると、

$X_1 \quad X_2$

$$|X_1 - X_2| < P \quad ( 8 )$$

$$\mu(X_1) = \mu(X_2)$$

が成り立つ。 ( 5 ) 式より、

$$\begin{aligned}(dX_1+B) &= m_1M + \mu(X_1) \\(dX_2+B) &= m_2M + \mu(X_2)\end{aligned}\quad (9)$$

(8)、(9)より、

$$d(X_1 - X_2) = (m_1 - m_2)M \quad (10)$$

$M$ は素数でかつ $d$ 、 $M$ は互いに素であるので、

$$|X_1 - X_2| = |(m_1 - m_2)/d|M > M \quad (11)$$

となり、(8)の前提に矛盾する。

(3) メモリアクセスと演算

線形Pベクトルのパラメータ $a, b, c, e$ の値を決定

PE番号 $X$ とそれに対応する要素が格納されているメ

モリバンク  $\mu$  を対応

結合網の設定

バンク内アドレス を全てのバンク  $\mu$  について並列に

求め、

P個のデータの並列アクセスを行い、PEに転送

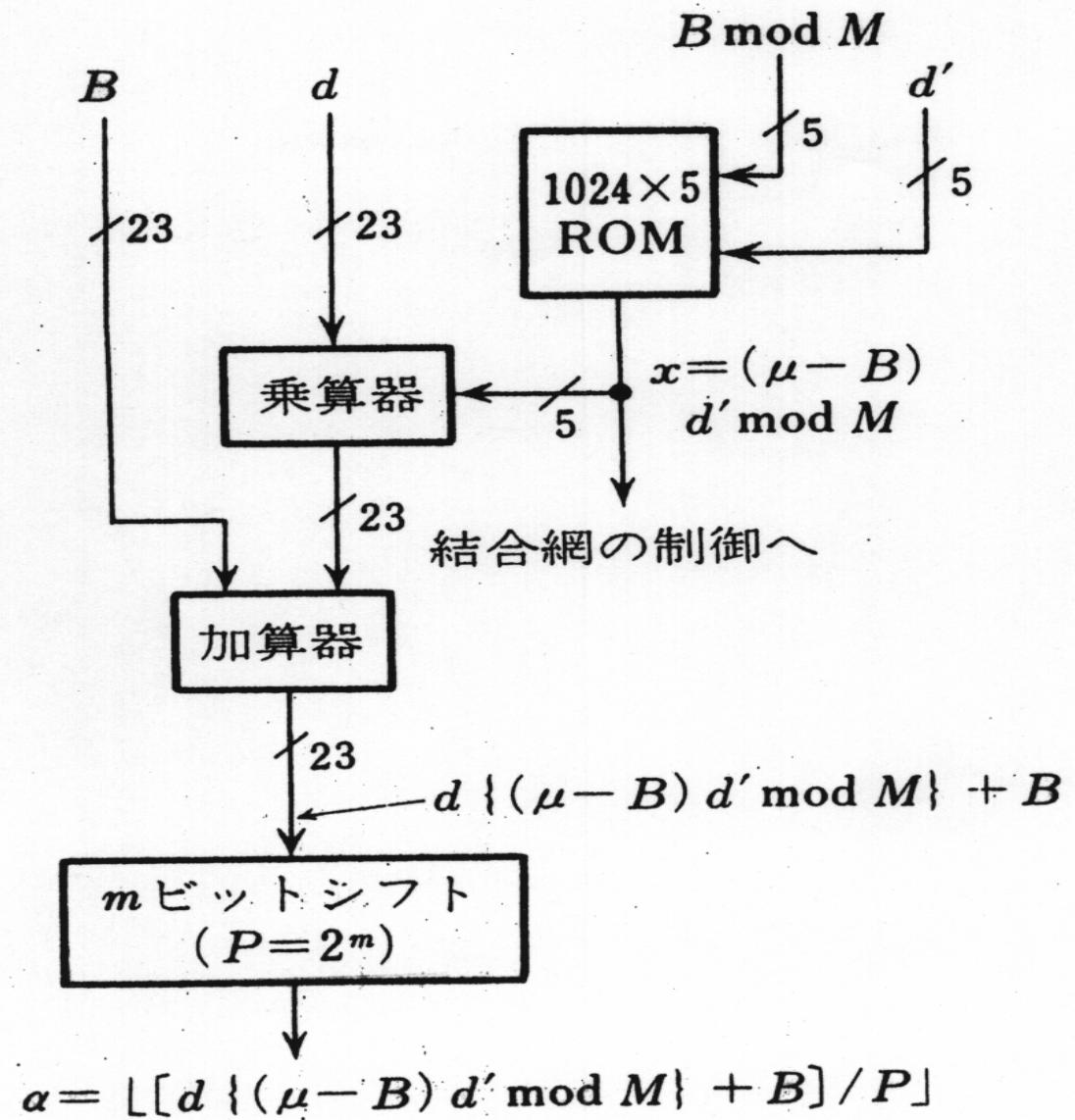

式(5)より、

$$dX + B = mM + \mu \quad (12)$$

両辺に  $d'$  (ただし、 $dd' \equiv 1 \pmod{M}$ ) を乗じて、

$$dd'X + d'B = md'M + d'\mu \quad (13)$$

これより、

$$X = d'(\mu - B) \bmod M \quad (14)$$

(14)を(6)に代入して、

$$(\mu) = \lfloor [d\{d'(\mu - B) \bmod M\} + B]/P \rfloor \quad (15)$$

$$\alpha = \lfloor [d \{(\mu - B) d' \bmod M\} + B] / P \rfloor \quad \mu(x) = (dx + B) \bmod M$$

または

$$x = (\mu - B) d' \bmod M$$

$P=4, M=5$  の時、 $4 \times 4$  行列を格納すると

|       |                                                                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|

|       | $a_{11}, a_{21}, a_{31}, a_{41}, a_{12}, a_{22}, a_{32}, a_{42}, a_{13}, a_{23}, a_{33}, a_{43}, a_{14}, a_{24}, a_{34}, a_{44}$ |

| $a$   | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15                                                                                            |

| $\mu$ | 0 1 2 3 4 0 1 2 3 4 0 1 2 3 4 0                                                                                                  |

|       | 0 0 0 0 1 1 1 1 2 2 2 2 3 3 3 3                                                                                                  |

対角要素：競合

$d = 5, M = 5 ! !$

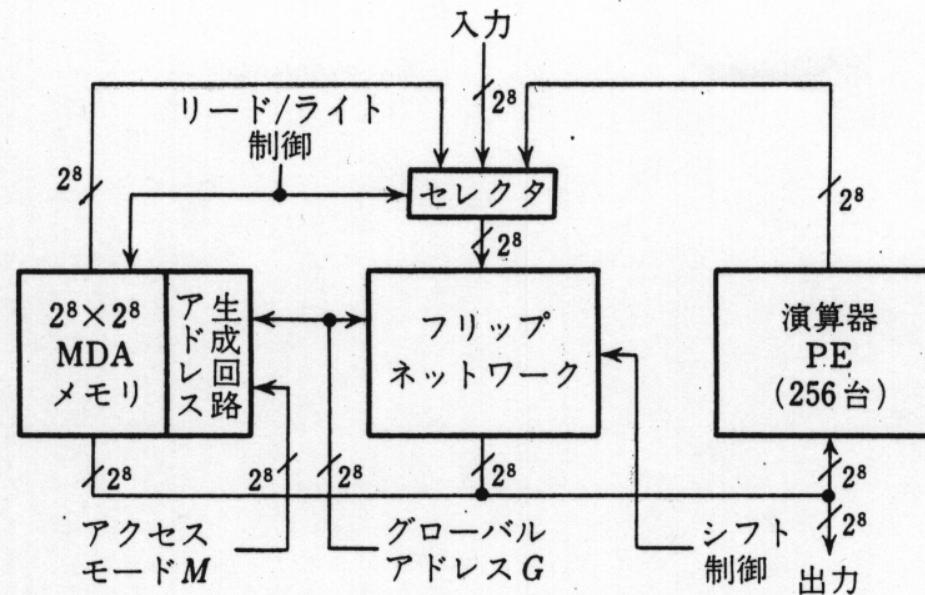

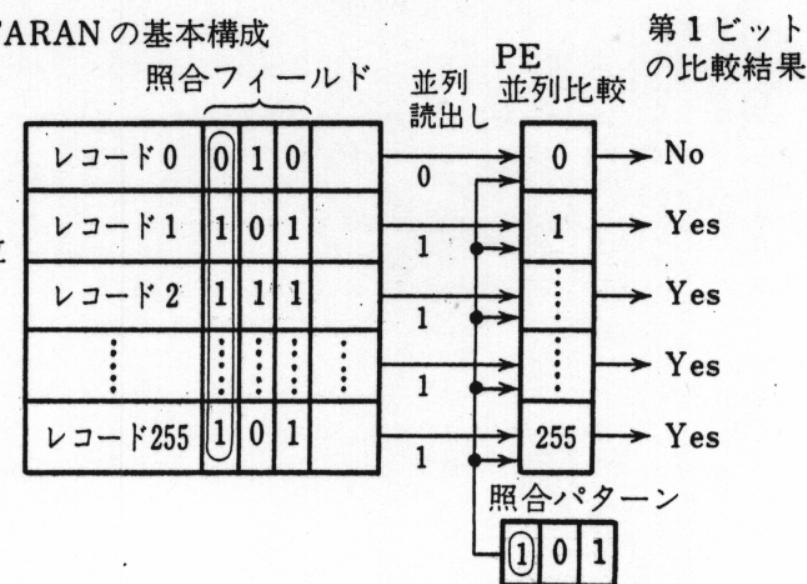

## 3 . 4 STARAN

( 1 ) STARANの基本構成

大規模連想メモリ

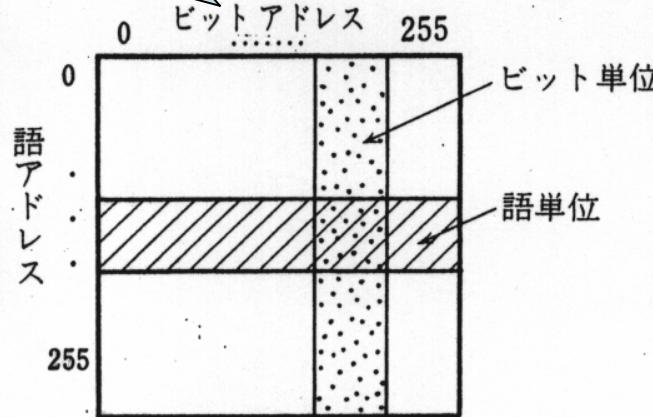

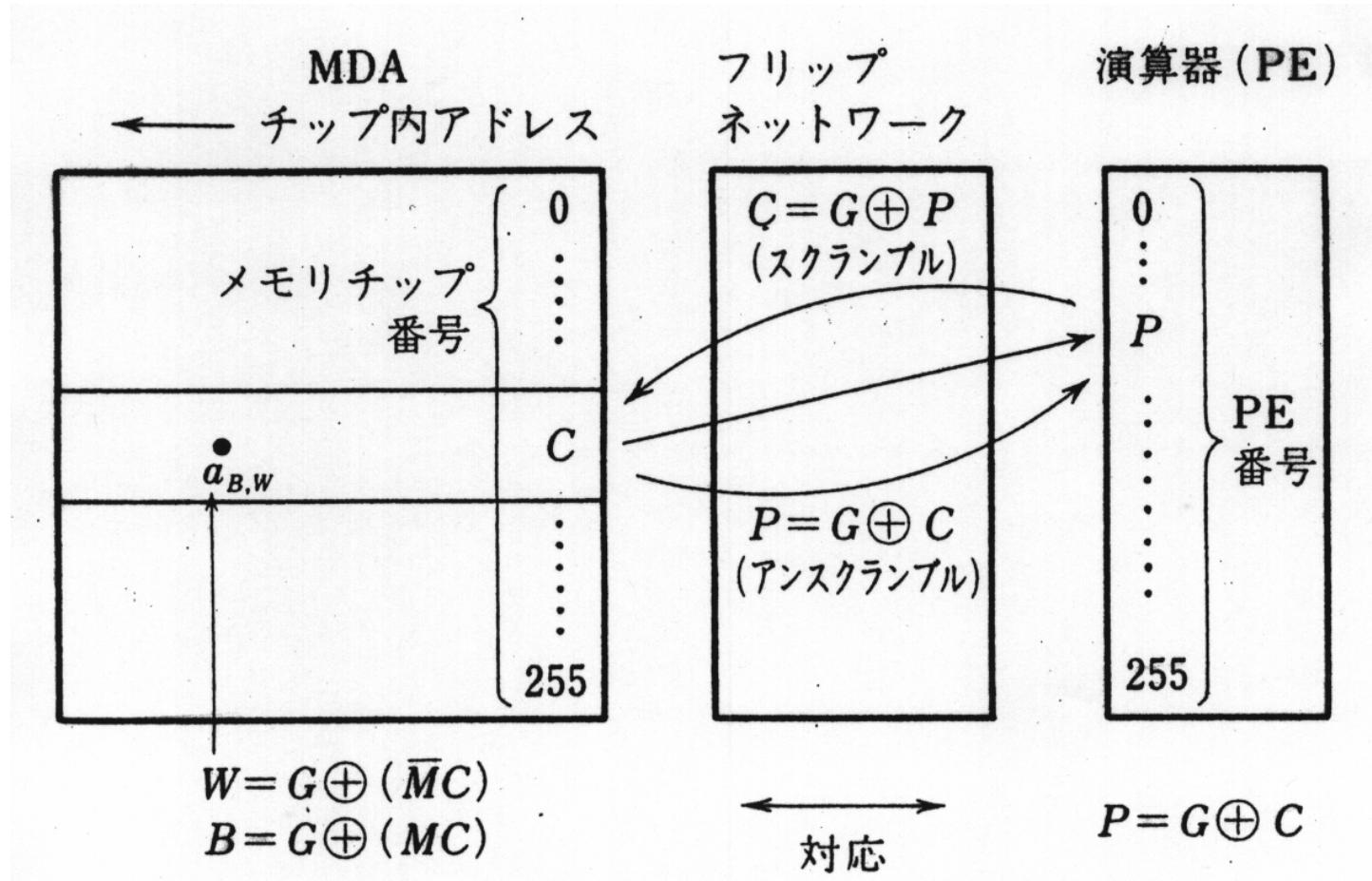

( 2 ) MDAの構成

MDA : 通常のRAMを256個用いて構成

排他的論理和を多用した直交メモリ

$$A = B \oplus C \quad B \oplus A = B \oplus (B \oplus C) = (B \oplus B) \oplus C = C$$

逆関数が容易に求められる

図3.9 : 8x8のMDA

$a_{B,W}$  : 語Wのビット B

直交メモリ

(b) MDAの構成

(a) STARANの基本構成

(c) STARANの連想処理装置としての利用

$a_{B,W}$ とメモリチップ番号Cの

チップ内アドレスBとの対応

## ストレージルール：

$$C = B \oplus W \quad (16)$$

$$W = B \oplus C \quad (17)$$

$\oplus$ ：排他的論理和

メモリチップCに対するチップ内アドレス生成規則

## アドレッシングルール：

$$B = G \oplus (MC) \quad (18)$$

M : アクセスマード

G : グローバルアドレス

メモリチップC

|   |          |          |          |          |          |          |          |          |

|---|----------|----------|----------|----------|----------|----------|----------|----------|

| 0 | $a_{00}$ | $a_{11}$ | $a_{22}$ | $a_{33}$ | $a_{44}$ | $a_{56}$ | $a_{66}$ | $a_{77}$ |

| 1 | $a_{01}$ | $a_{10}$ | $a_{23}$ | $a_{32}$ | $a_{45}$ | $a_{54}$ | $a_{67}$ | $a_{76}$ |

| 2 | $a_{02}$ | $a_{13}$ | $a_{20}$ | $a_{31}$ | $a_{46}$ | $a_{57}$ | $a_{64}$ | $a_{75}$ |

| 3 | $a_{03}$ | $a_{12}$ | $a_{21}$ | $a_{30}$ | $a_{47}$ | $a_{56}$ | $a_{65}$ | $a_{74}$ |

| 4 | $a_{04}$ | $a_{15}$ | $a_{26}$ | $a_{37}$ | $a_{40}$ | $a_{51}$ | $a_{62}$ | $a_{73}$ |

| 5 | $a_{05}$ | $a_{14}$ | $a_{27}$ | $a_{36}$ | $a_{41}$ | $a_{50}$ | $a_{63}$ | $a_{72}$ |

| 6 | $a_{06}$ | $a_{17}$ | $a_{24}$ | $a_{35}$ | $a_{42}$ | $a_{53}$ | $a_{60}$ | $a_{71}$ |

| 7 | $a_{07}$ | $a_{16}$ | $a_{25}$ | $a_{34}$ | $a_{43}$ | $a_{52}$ | $a_{61}$ | $a_{70}$ |

|   | 0        | 1        | 2        | 3        | 4        | 5        | 6        | 7        |

チップ内アドレス  $B$

$a_{B,W}$  = 語  $W$  のビット  $B$

式(17)、(18)より、

$$W = G \oplus (\sim MC) \quad (19)$$

メモリチップ番号CとPE番号Pの対応関係

スクランブルルール：  $C = G \oplus P \quad (20)$

アンスクランブルルール：  $P = G \oplus C \quad (21)$

アクセスルール：  $W = (MG) \oplus (\sim MP) \quad (22)$

$$B = (\sim MG) \oplus (MP)$$

$M = (1, 1, \dots, 1)$ 、Gとして語アドレス

語GのビットPがPE番号Pでアクセス：

語単位アクセス

# 証明

$$A \oplus B = A\bar{B} + \bar{A}B$$

$$\begin{aligned}\overline{A + B} &= \overline{\overline{AB}} \\ \overline{AB} &= \overline{A} + \overline{B}\end{aligned}$$

ドモルガンの

双対定理

$$\begin{aligned}

W &= (G \oplus MC) \oplus C = G \oplus (MC \oplus C) = \\

&\quad G \oplus (MCC\bar{C} + \bar{M}\bar{C}C) = G \oplus ((\bar{M} + \bar{C})C) \\

&= G \oplus \bar{M}C

\end{aligned}$$

$$\begin{aligned}

W &= G \oplus (\bar{M}(G \oplus P)) = \overline{\overline{GM}}(G \oplus P) + \overline{GM}(G \oplus P) \\

&= G(M + \overline{G \oplus P}) + \overline{G}(\bar{M}(G\bar{P} + \bar{G}P)) \\

&= GM + G(\overline{\bar{G}P + G\bar{P}}) + \overline{GM}P \\

&= GM + G(G + \bar{P})(\bar{G} + P) + \overline{GM}P = GM + GP + \overline{GM}P

\end{aligned}$$

$$\begin{aligned}

W &= (MG \oplus \bar{M}P) = MG(M + \bar{P}) + (\bar{M} + \bar{G})(\bar{M}P) \\

&= GM + \bar{M}P + \overline{GM}P = GM + G\bar{M}P + \overline{GM}P + \overline{GM}P

\end{aligned}$$

$M = (0, 0, \dots, 0)$ 、 $G$ としてビットアドレス

語 $P$ のビット $G$ がPE番号 $P$ でアクセス：

ビット単位アクセス

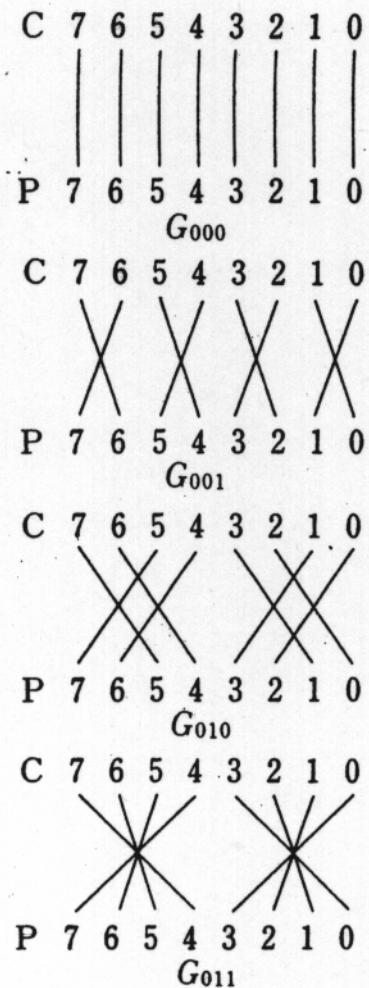

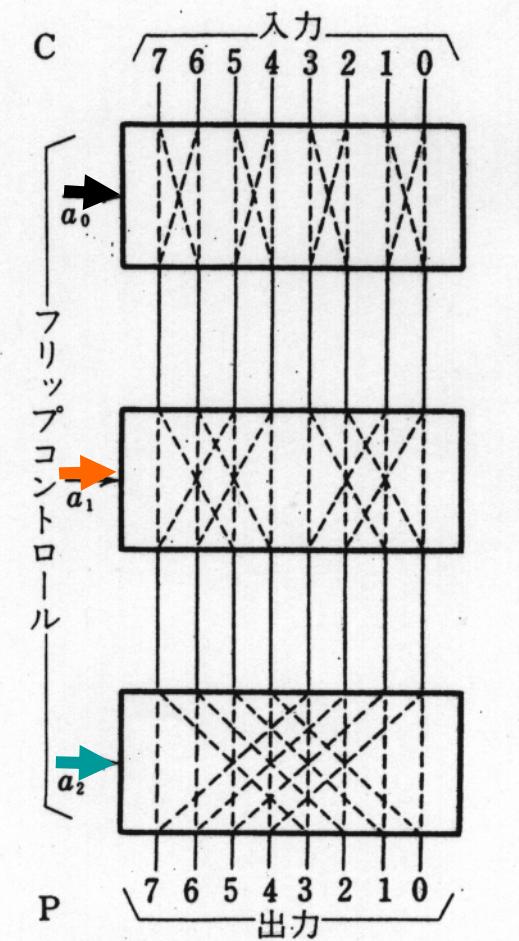

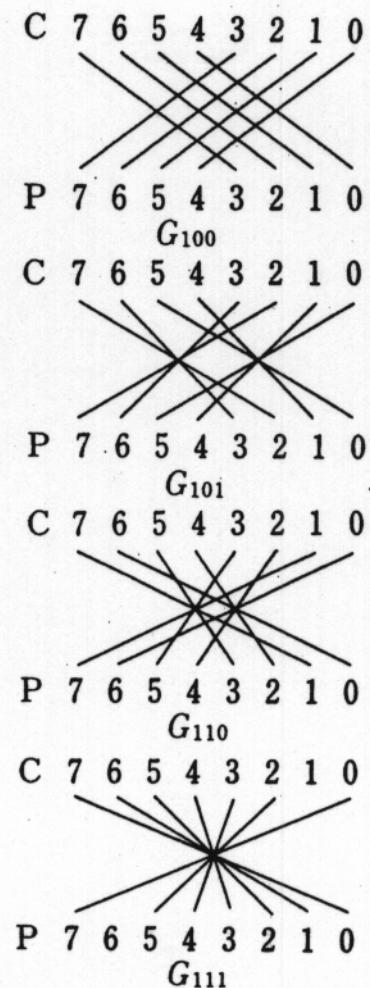

### ( 3 ) フリップネットワークの構成

写像 :  $P = G \oplus C$

$G : G_{a_2 a_1 a_0}$

$$G_{a_2 a_1 a_0} = a_2 G_{100} \oplus a_1 G_{010} \oplus a_0 G_{001}$$

$$P = G \oplus C = a_2 G_{100} \oplus a_1 G_{010} \oplus a_0 G_{001} \oplus C$$

間接 2 進  $n$  - キューブ

(a) フリップネットワークによる入出力間の論理的結合

(b) 多段結合網によるフリップネットワークの実現

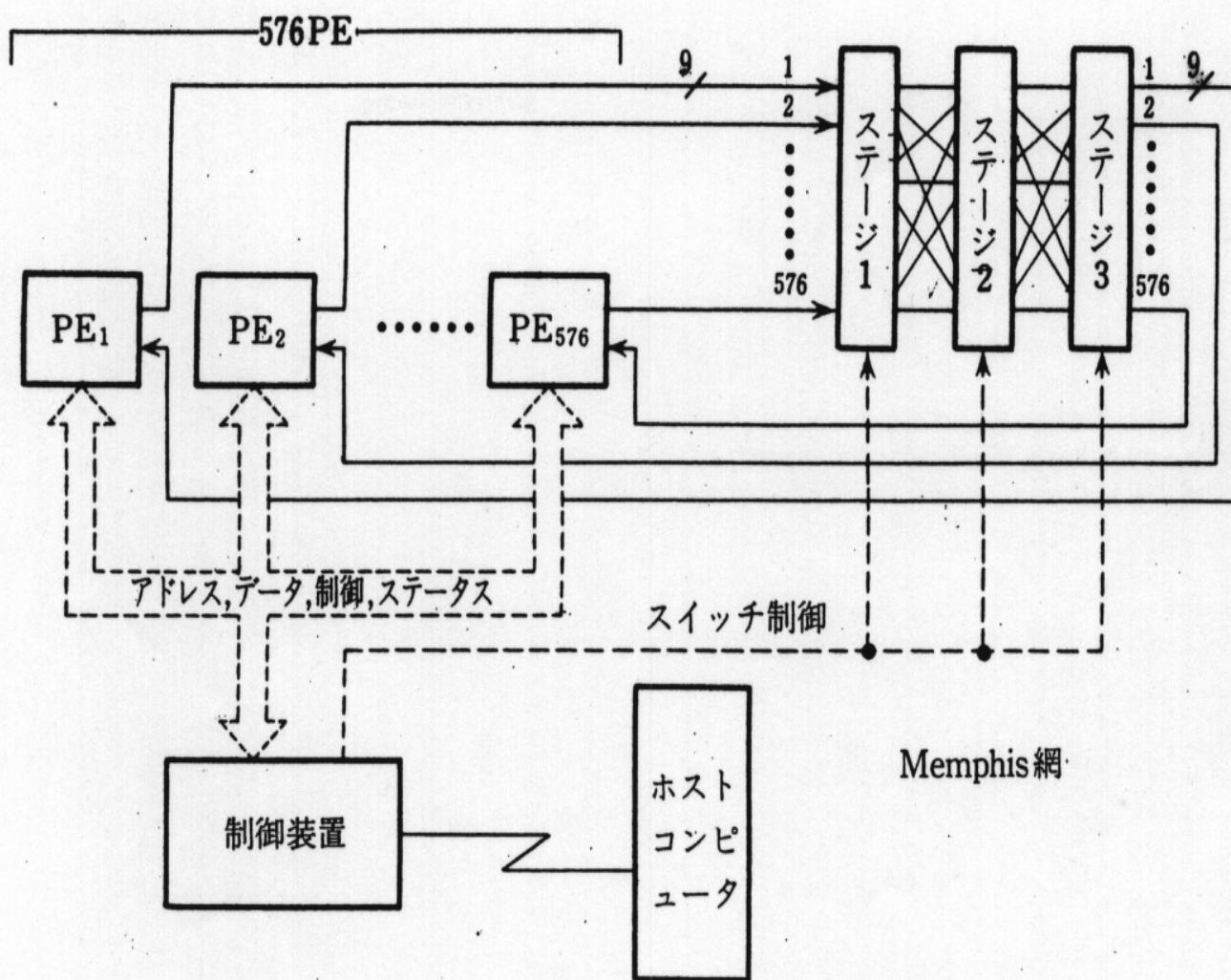

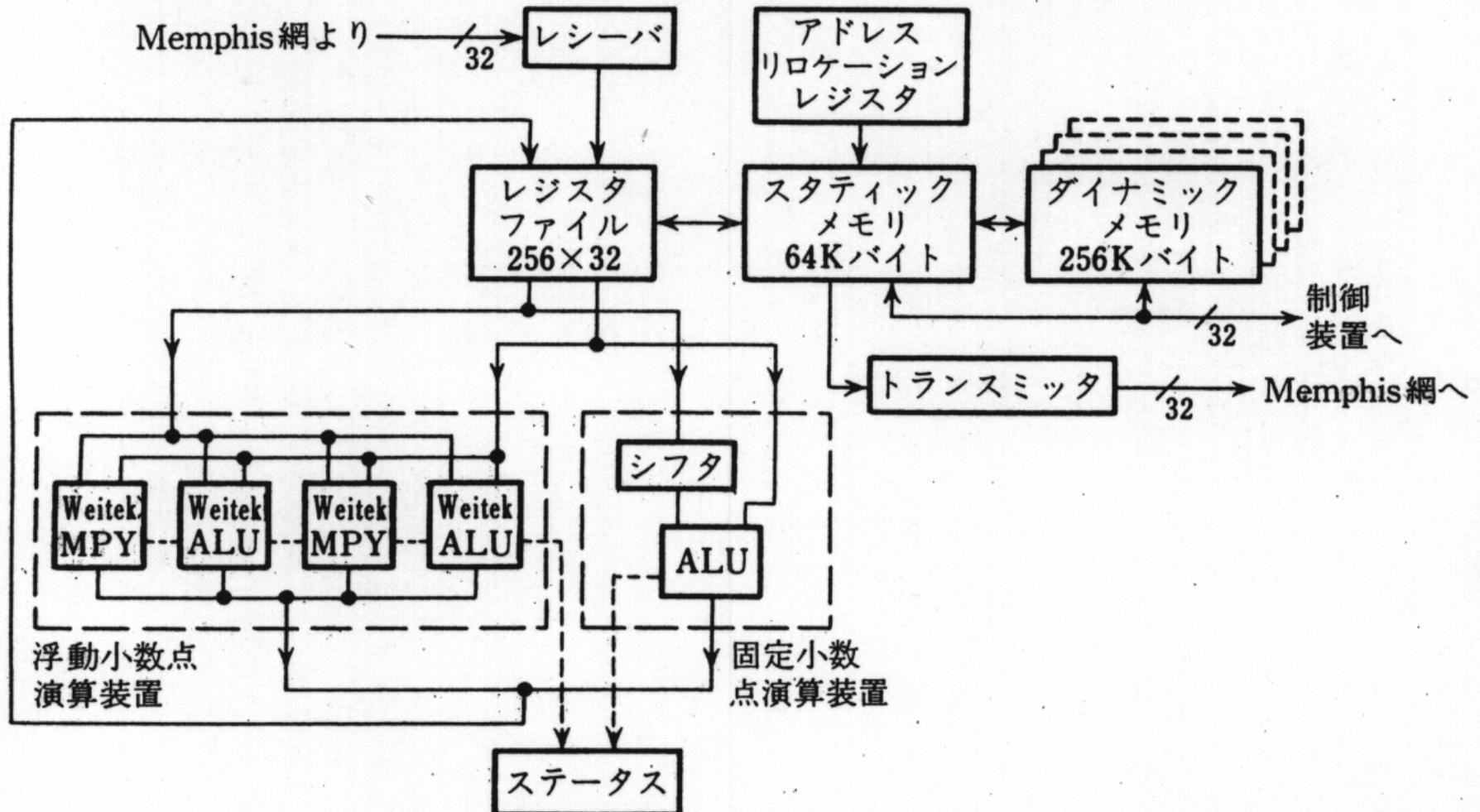

**3 . 5      G F - 1 1**

IBM社のT.J.Watson研究所

576台のPE、

Memphis網

( 1 ) 各PE :

4台の浮動小数点演算器、

1台の固定小数点演算器、

256語のレジスタファイル

180ビット長の命令によって同時に制御 ( VLIW )

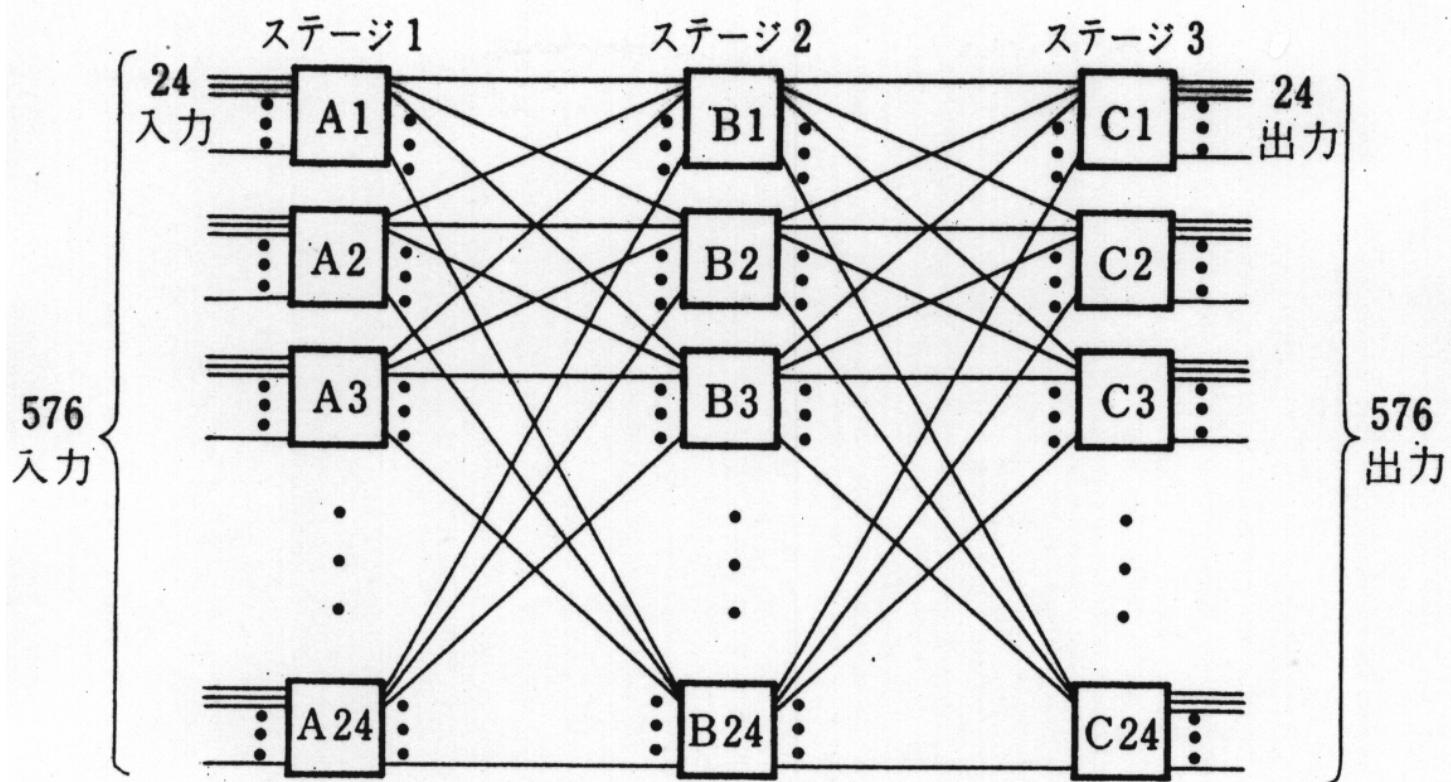

( 2 ) Memphis網

3ステージClos網 (  $n=m$  )

2 4 × 2 4 のクロスバ網を利用

( a ) GF-11の構成

(c) Memphis 網の構成

各ボックスは  $24 \times 24$  のクロスバースイッチ

各入出力線は 9 ビット幅 (8 ビットデータ, 1 ビットparity)

## 3 . 6 C M - 1

従来のコンピュータシステム：メモリは受動的

IBMのJ.Backus：フォンノイマンボトルネック

ロジックインメモリの考え方

メモリの中に論理を持ち込み、

処理をメモリ側で分担する方式

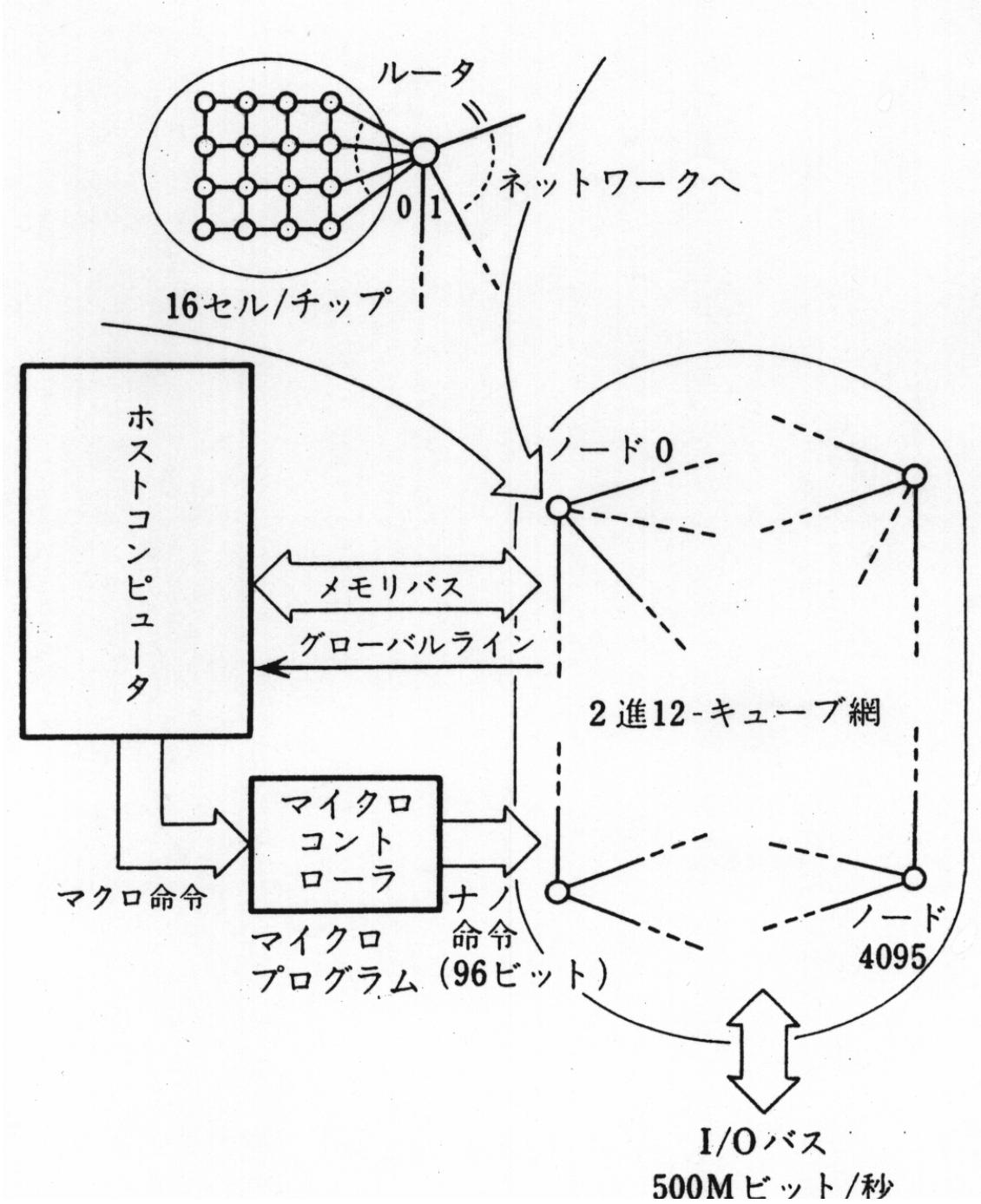

( 1 ) Connection Machine の構成

相互結合網：2進12キューブ

各ノードに1台のルータが結合

16台のセルが結合（セル総数は65536台）

## ( 2 ) Connection Machine の基本演算操作

プログラミング言語Lisp

基本データ構造 : Xector ( ゼクタ )

Xector :

( インデックス - 値 ) ペアからなる要素の集合

{ sky-blue grass-green apple-red }

並列演算 : 、 操作

操作 : 各 Xector 内の同一インデックスを

含む要素に独立に作用

( a + ' { A-1 B-2 } ' { A-3 B-3 } ) = { A-4 B-5 }

操作 : Xector要素の値に作用して、

一つの値を生成

( +' {A-1 B-2 C-3} )=6

、 操作の組み合わせ

集合演算（積集合の計算など）、木構造演算

（木構造要素の和）、バタフライ構造演算

（バイトニックソータなど）、文字列演算、

サーチ演算、配列演算（画像処理の空間フィルタ

など）

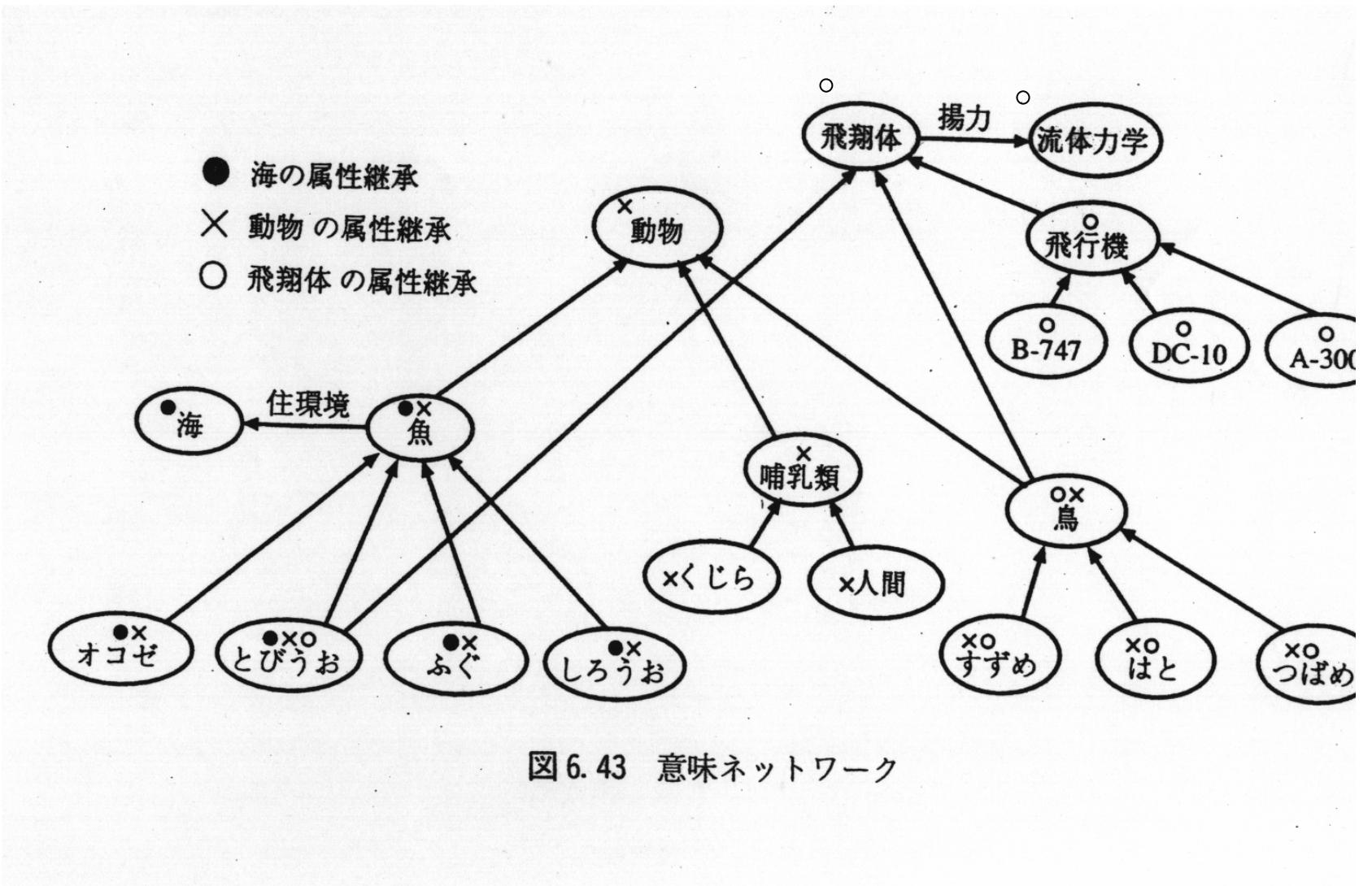

図 6.43 意味ネットワーク

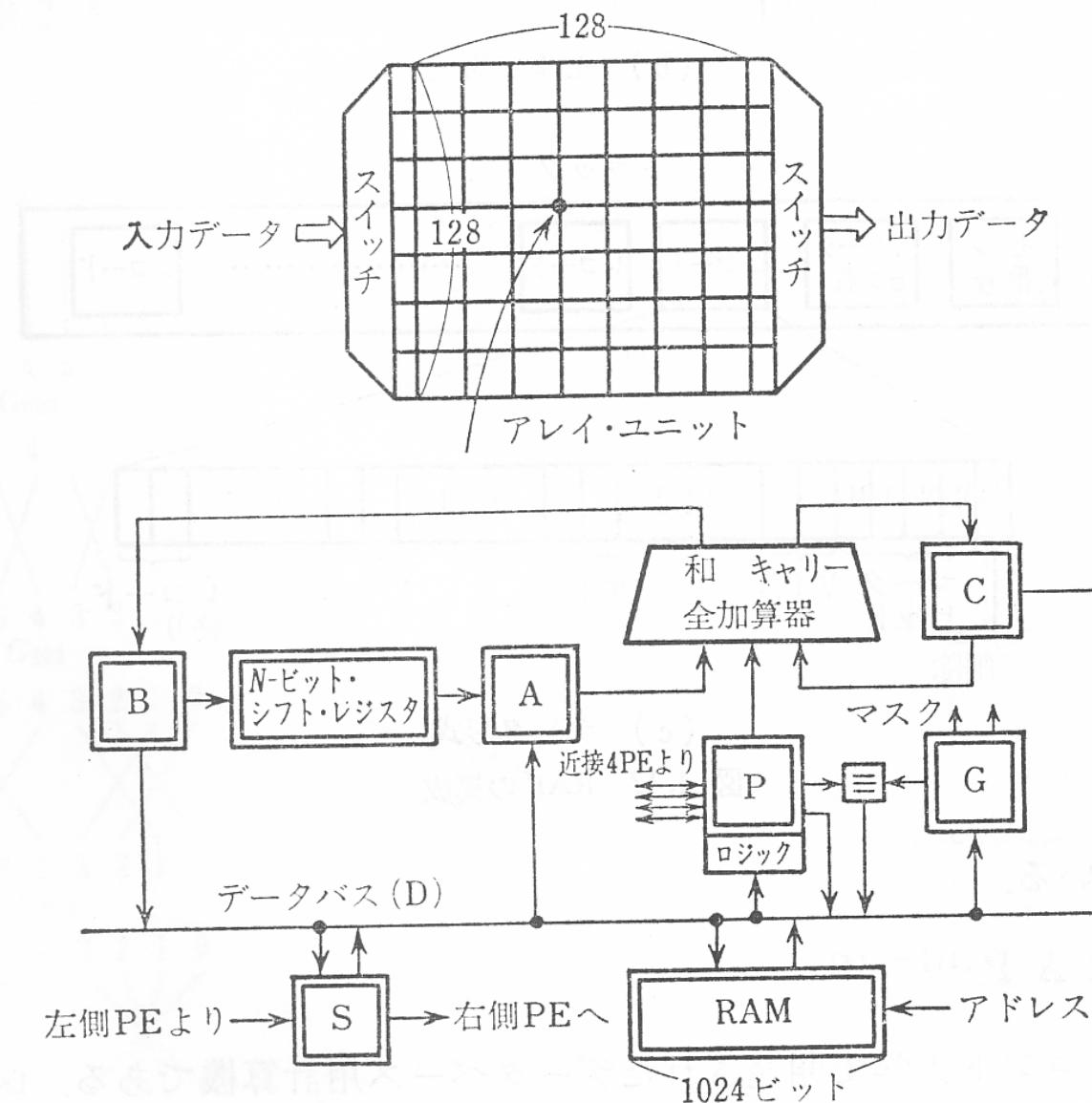

# MPP

図 4.18 MPP の構成(K. E. Batcher: Design of a Massively Parallel Processor,

IEEE Trans. C. Vol. 29, No. 9, 1980, pp. 836-840 による)

# フィルタ処理：輪郭線抽出など

## ラプラシアンオペレータ

$$\begin{aligned}\nabla^2 \varphi &= \partial^2 \varphi / \partial x^2 + \partial^2 \varphi / \partial y^2 \\&= \varphi(I+1, J) - \varphi(I, J) - \\&\quad (\varphi(I, J) - \varphi(I-1, J)) + \\&\quad \varphi(I, J+1) - \varphi(I, J) - \\&\quad (\varphi(I, J) - \varphi(I, J-1)) \\&= \varphi(I+1, J) + \varphi(I-1, J) \\&\quad + \varphi(I, J+1) + \varphi(I, J-1) \\&\quad - 4\varphi(I, J)\end{aligned}$$

|   |     |   |

|---|-----|---|

|   | 1   |   |

| 1 | - 4 | 1 |

|   | 1   |   |

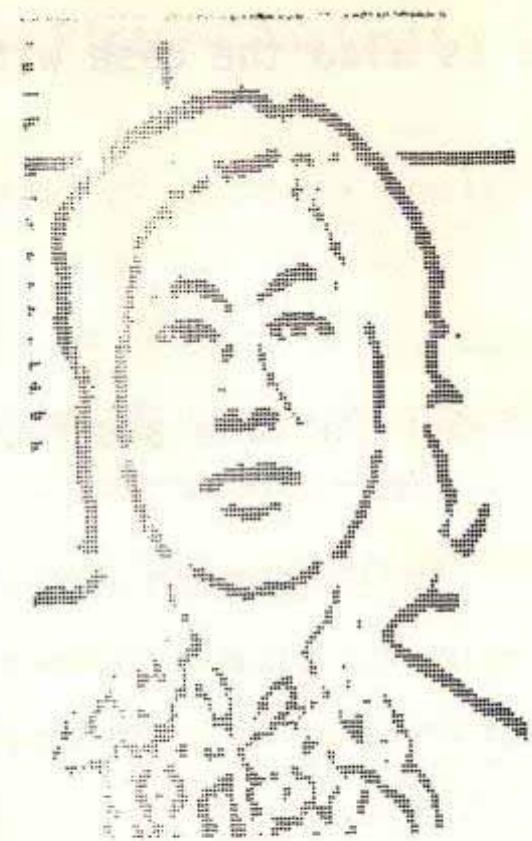

(a) Original photograph

(b) Printout of the digital gray-level picture

(c) Binary picture

Figure 3-2

Picture input and line extraction.

The dark horizontal line in the upper

part is due to the burn in the CRT

surface of the FSS used for digitization.

金出武雄博士論文

# SIMD計算機は歴史的な役割を 終えたか？

汎用並列コンピュータ: YES

マルチプロセッサが席巻

専用コンピュータ

画像処理: 光の直接入力、演算ビット幅

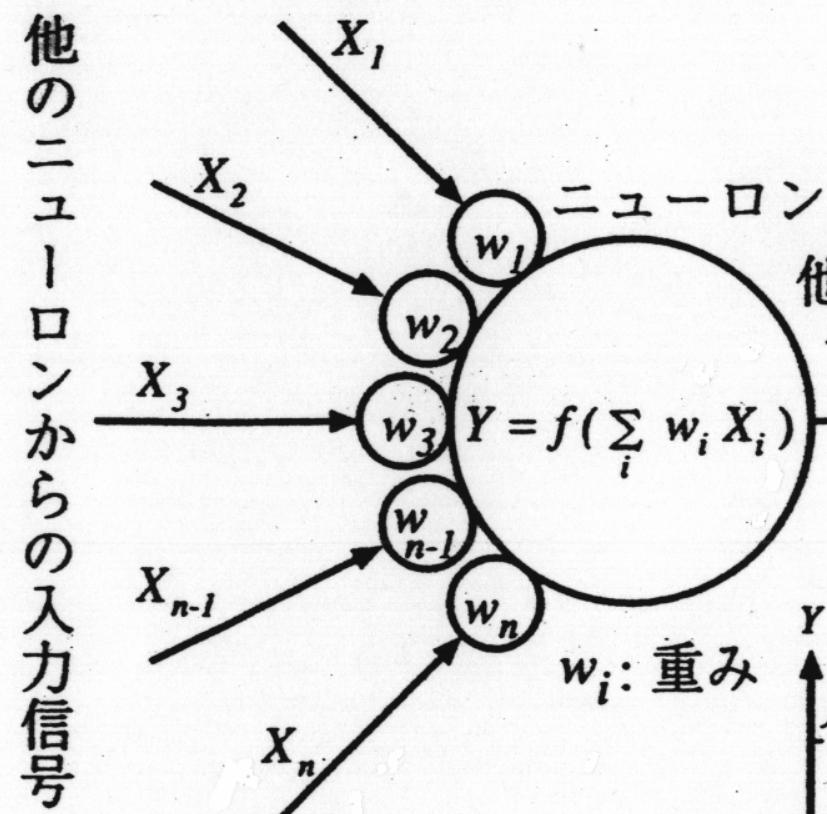

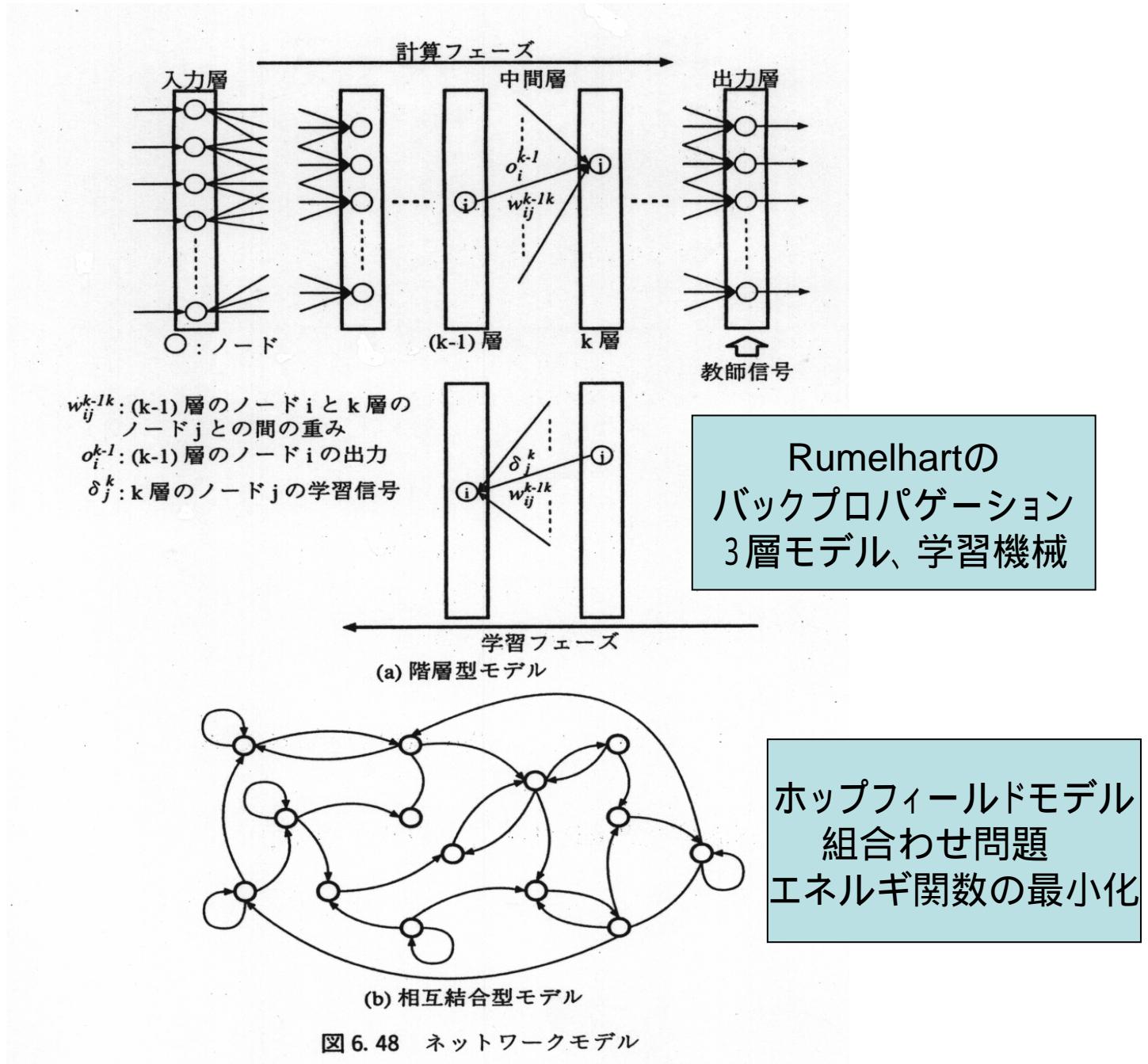

ニューラルネット: 多対多ブロードキャスト

機能メモリ

DRAMセルに演算器

MMXやSSEなどマルチメディア命令

$$f(x) = \frac{1}{1 + \exp(-x + \theta)}$$

$$f'(x) = f(x)(1 - f(x))$$

他のニューロン

への出力信号

$Y$

入出力特性関数

シグモイド状関数

$$\sum_i w_i X_i$$

図 6.47 ニューロンモデル

マルチメディア対応の機械命令

Intel社

MMX: 画像処理, 整数演算

64ビットデータに対する

サブワード演算:

8bx8, 16bx4など

飽和演算

カラー画像

R,G,B: 各8ビット

表 5.4 Intel マルチメディア向き命令 (MMX)

---

|              |                                                         |

|--------------|---------------------------------------------------------|

| Paddb など     | 8つのバイトデータ(b), 4つの16ビットデータ(w), 2つの32ビットデータ(d)に対する並列加減算   |

| Pcompeqb など  | 8つのバイトデータ, 4つの16ビットデータ, 2つの32ビットデータに対する並列比較演算           |

| Pmullw など    | 4つの16ビットデータ(w)に対する並列乗算                                  |

| Pmaddwd など   | 4つの16ビットデータについて, 2つの隣接16ビットデータの積の和                      |

| Psraw など     | 4つの16ビットデータ, 2つの32ビットデータ, 1つの64ビットデータに対する論理/算術, 左右シフト演算 |

| Punpcktbw など | パックされている8つのバイトデータ, 4つの16ビットデータ, 2つの32ビットデータをアンパックする。    |

| Pactsswb など  | 16ビットデータ, 32ビットデータを8ビットデータ, 16ビットデータにパック                |

| Pand など      | 64ビットデータの論理(and, or, xorなどを含む)操作                        |

| Movd など      | 32ビットデータまたは64ビットデータのレジスター/メモリ, レジスター/レジスタ間転送            |

---

# フィルタ処理：輪郭線抽出など

## ラプラシアンオペレータ

$$\begin{aligned}\nabla^2 \varphi &= \partial^2 \varphi / \partial x^2 + \partial^2 \varphi / \partial y^2 \\&= \varphi(I+1, J) - \varphi(I, J) - \\&\quad (\varphi(I, J) - \varphi(I-1, J)) + \\&\quad \varphi(I, J+1) - \varphi(I, J) - \\&\quad (\varphi(I, J) - \varphi(I, J-1)) \\&= \varphi(I+1, J) + \varphi(I-1, J) \\&\quad + \varphi(I, J+1) + \varphi(I, J-1) \\&\quad - 4\varphi(I, J)\end{aligned}$$

|   |     |   |

|---|-----|---|

|   | 1   |   |

| 1 | - 4 | 1 |

|   | 1   |   |

(a) Original photograph

(b) Printout of the digital gray-level picture

(c) Binary picture

Figure 3-2

Picture input and line extraction.

The dark horizontal line in the upper

part is due to the burn in the CRT

surface of the FSS used for digitization.

金出武雄博士論文

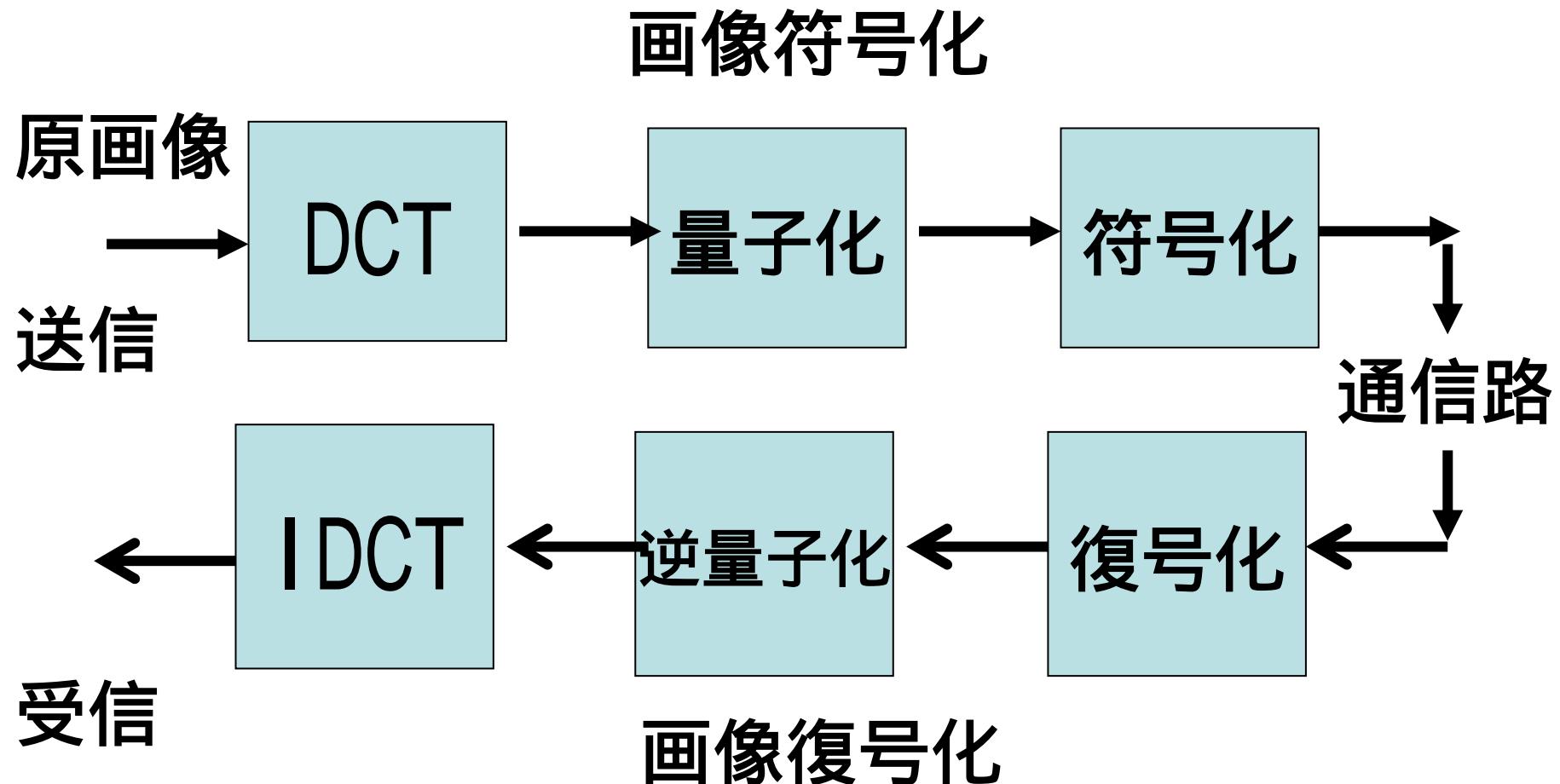

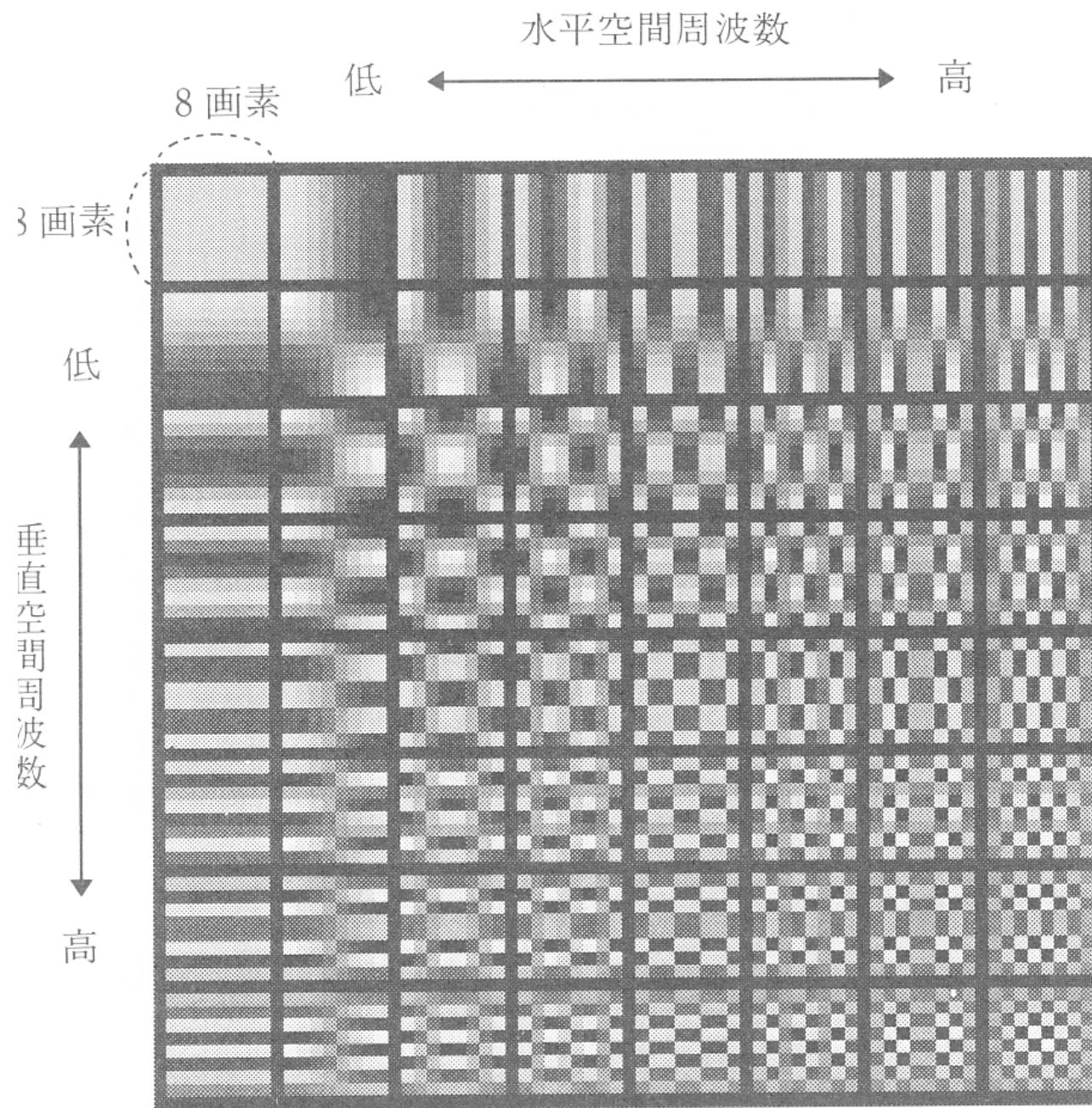

# 画像符号化・復号化

DCT：離散コサイン変換

安田、藤原監訳

# DCT変換（1次元）の証明

情報圧縮技術、bit別

冊、共立、1997

正規化 DCT

$$X^{c2}(k) = \sqrt{\frac{2}{N}} c_k \sum_{n=0}^{N-1} x(n) \cos \left[ \frac{(2n+1)k\pi}{2N} \right], \quad (5.11)$$

$$k = 0, 1, \dots, N-1$$

正規化 IDCT

$$x(n) = \sqrt{\frac{2}{N}} \sum_{k=0}^{N-1} c_k X^{c2}(k) \cos \left[ \frac{(2n+1)k\pi}{2N} \right],$$

$$n = 0, 1, \dots, N-1$$

$$\cos\{(2n+1)k/(2N)\}$$

|         | $n=0$        | $1$                    | $N/4-1$                      | $N/4$                      | $N/2-1$                    | $N/2$        | $3/4N-1$ | $3/4N$  | $N-1$      |

|---------|--------------|------------------------|------------------------------|----------------------------|----------------------------|--------------|----------|---------|------------|

| $K=0$   | 1            | 1                      | 1                            | 1                          | 1                          | 1            | 1        | 1       | 1          |

| $K=1$   | $1/(2N)$     | $3/(2N)$               | $\dots$                      | $\dots$                    | $1/2-1/(2N)$               | $1/2+1/(2N)$ | $\dots$  | $\dots$ | $1-1/(2N)$ |

| $K=2$   | $1/N$        | $3/N \cdots (1/2-1/N)$ | $(1/2 + 1/N) \cdots (1-1/N)$ | $(1+1/N) \cdots (3/2-1/N)$ | $(3/2+1/N) \cdots (2-1/N)$ | $\dots$      | $\dots$  | $\dots$ | $\dots$    |

| $K=N-1$ | $1/2-1/(2N)$ | $3/2-3/(2N)$           | $1/2-5/(2N)$                 | $3/2-7/(2N)$               |                            |              |          |         |            |

Kが小さいほど低周波領域

## 基底ベクトル

$$c(k,n) = 1/\sqrt{N} : k=0$$

$$c(k,n) = \sqrt{2/N} \cos \frac{(2n+1)k\pi}{2N} : k \neq 0$$

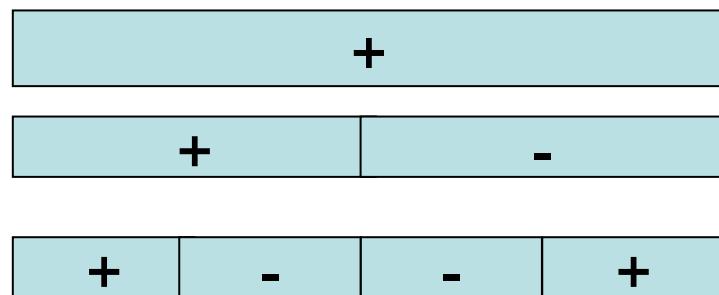

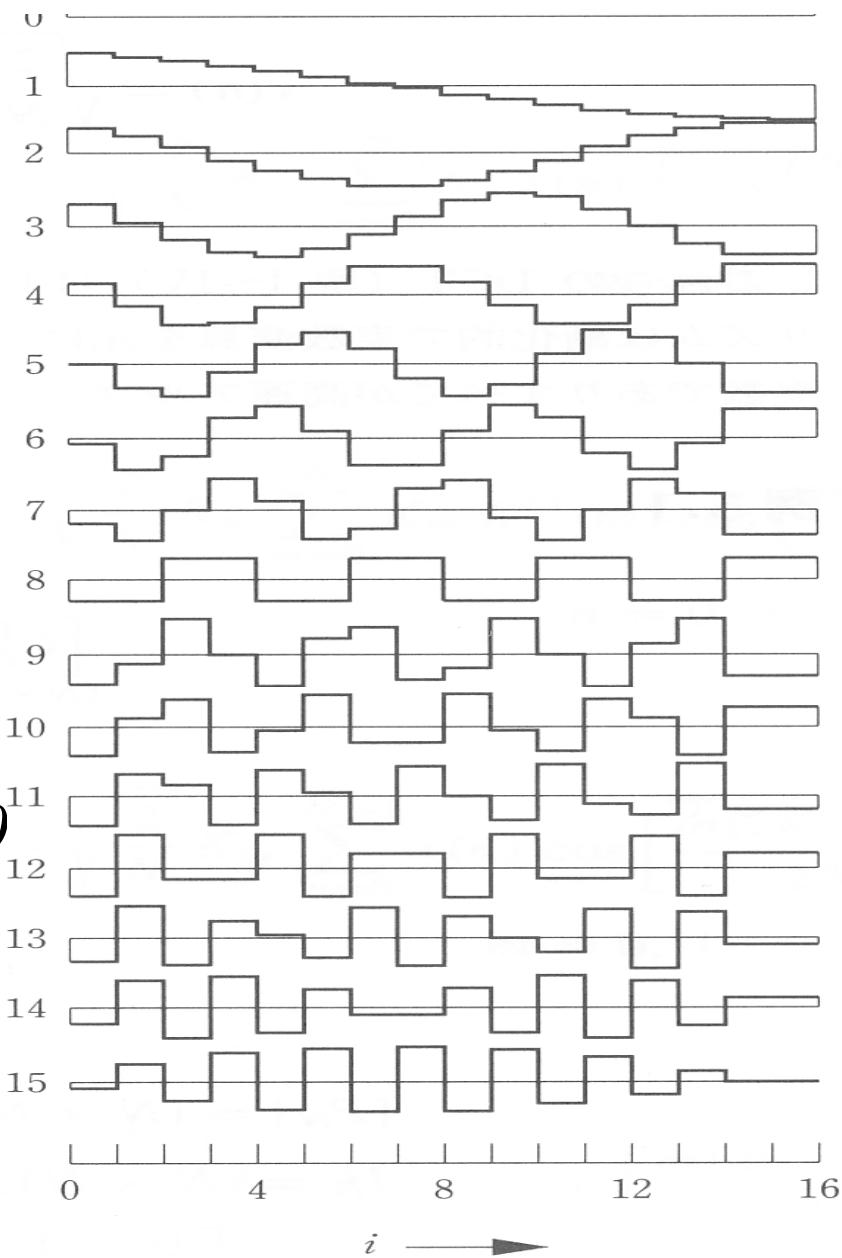

図 5.1 DCT-II の基底関数  $N = 16$

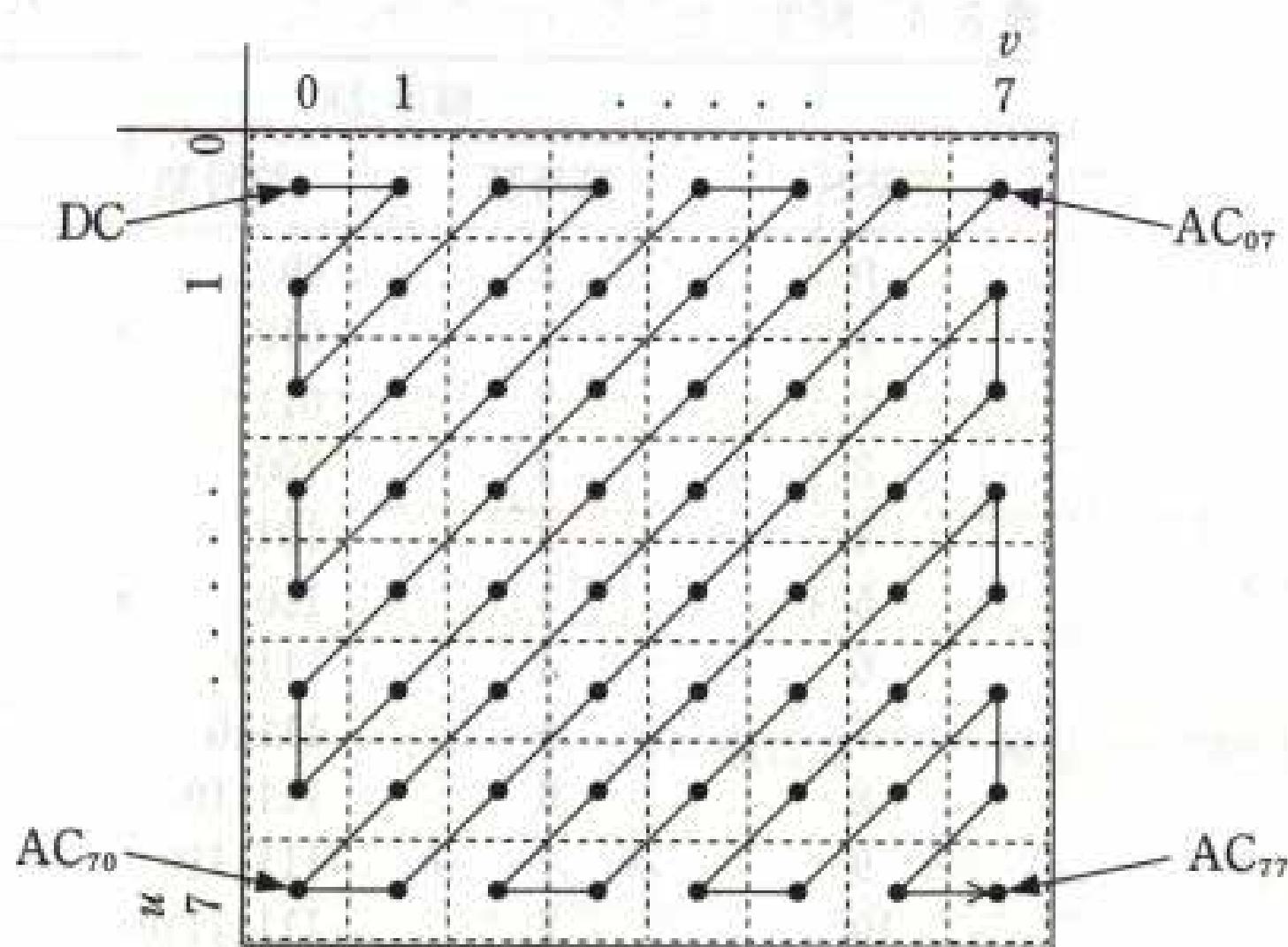

図 4.13 2 次元 DCT の基底画像パターン (8×8 の場合)

$$\begin{aligned}

x_n &= \frac{2}{N} \sum_{k=0}^{N-1} c_k^2 \sum_{m=0}^{N-1} x_m \cos \left[ \frac{(2m+1)k\pi}{2N} \right] \cos \left[ \frac{(2n+1)k\pi}{2N} \right] \\

&= \frac{2}{N} \sum_{m=0}^{N-1} x_m \sum_{k=0}^{N-1} c_k^2 \cos \theta_m \cos \theta_n

\end{aligned} \tag{5.25}$$

ただし、

$$\begin{aligned}

\theta_m &= \frac{(2m+1)k\pi}{2N}, \quad \theta_n = \frac{(2n+1)k\pi}{2N} \\

\cos \theta_m \cos \theta_n &= \frac{1}{2} [\cos(\theta_m + \theta_n) + \cos(\theta_m - \theta_n)] \\

&= \frac{1}{2} \left[ \frac{e^{j(\theta_m+\theta_n)} + e^{-j(\theta_m+\theta_n)}}{2} \right] + \frac{1}{2} \left[ \frac{e^{j(\theta_m-\theta_n)} + e^{-j(\theta_m-\theta_n)}}{2} \right]

\end{aligned}$$

ここで、 $j = \sqrt{-1}$  とおくと、式(5.25) は次のようになる。

$$\begin{aligned}

x_n &= \frac{1}{2N} \sum_{m=0}^{N-1} x_m \sum_{k=0}^{N-1} c_k^2 \left( \exp \left[ j \frac{2k\pi}{2N} (m+n+1) \right] + \exp \left[ -j \frac{2k\pi}{2N} (m+n+1) \right] \right. \\

&\quad \left. + \exp \left[ j \frac{2k\pi}{2N} (m-n) \right] + \exp \left[ -j \frac{2k\pi}{2N} (m-n) \right] \right) \tag{5.26}

\end{aligned}$$

$$c_k = \begin{cases} 1, & k \neq 0 \\ 1/\sqrt{2}, & k = 0 \end{cases}$$

$$\begin{aligned}

&= \frac{1}{2N} \sum_{m=0}^{N-1} x_m \sum_{k=0}^{N-1} c_k^2 \left( W_N^{-(m+n+1)\frac{k}{2}} + W_N^{(m+n+1)\frac{k}{2}} \right. \\

&\quad \left. + W_N^{-(m-n)\frac{k}{2}} + W_N^{(m-n)\frac{k}{2}} \right) \tag{5.27}

\end{aligned}$$

ただし、 $W_N = \exp\left(\frac{-j2\pi}{N}\right)$ =ユニタリ値の  $N$  乗根、である。

式(5.27) は以下のように変形出来る。

$$m = n \text{ and } k \neq 0 \text{ のとき } \left( \frac{1}{2N} x_n 2N \right) = x_n$$

$$m = n \text{ and } k = 0 \text{ のとき } \left( \frac{1}{2N} x_n \left( \frac{1}{\sqrt{2}} \right)^2 4N \right) = x_n$$

$$\text{ただし } \sum_{k=0}^{N-1} W_N^{kl} = N\delta(l), \quad \text{ここで } \delta(l) = \begin{cases} 0, & l \neq 0 \\ 1, & l = 0 \end{cases}$$

480 画素

720 画素

画面

ブロック

8 × 8 画素

1 画像 :

90 × 60

ブロック

正規化 2D-DCT

## 各ブロックに対して DCT ( N, M=8 )

$$\begin{aligned} X_{u,v}^{c2} &= c_u c_v \frac{2}{\sqrt{NM}} \sum_{n=0}^{N-1} \sum_{m=0}^{M-1} x_{n,m} \cos \left[ \frac{(2n+1)u\pi}{2N} \right] \cos \left[ \frac{(2m+1)v\pi}{2M} \right] \\ &= \sqrt{\frac{2}{N}} \sum_{n=0}^{N-1} c_u \left[ \sqrt{\frac{2}{M}} c_v \sum_{m=0}^{M-1} x_{n,m} \cos \frac{(2m+1)v\pi}{2M} \right] \cos \frac{(2n+1)u\pi}{2N}, \quad (5.38) \end{aligned}$$

$$u = 0, 1, \dots, N-1, \quad c_l = \begin{cases} 1/\sqrt{2}, & l=0 \\ 1, & l \neq 0 \end{cases}$$

$$v = 0, 1, \dots, M-1,$$

正規化 2D-IDCT

$$\begin{aligned} x_{n,m} &= \frac{2}{\sqrt{NM}} \sum_{u=0}^{N-1} \sum_{v=0}^{M-1} c_u c_v X_{u,v}^{c2} \cos \left[ \frac{(2n+1)u\pi}{2N} \right] \cos \left[ \frac{(2m+1)v\pi}{2M} \right], \quad (5.39) \\ n &= 0, 1, \dots, N-1, \quad m = 0, 1, \dots, M-1 \end{aligned}$$

演算量

各ブロック当たり:  $64 \times (63 + 64^*4) = 20480$

毎秒当たりのブロック数

$$5400^*30=162000$$

演算量: 3.2G演算 / 秒

総和

$X^*\cos^*\cos$

$\cos$  : テーブル参照

# 各ブロックのDC係数 $X_{uv}$ に量子化

$$X_{quv} = \text{Nearest Int} (X_{uv}/Q_{uv})$$

表8.1 輝度量子化マトリックス  $Q_{uv}$  [367]

|    |    |    |    |     |     |     |     |

|----|----|----|----|-----|-----|-----|-----|

| 16 | 11 | 10 | 16 | 24  | 40  | 51  | 61  |

| 12 | 12 | 14 | 19 | 26  | 58  | 60  | 55  |

| 14 | 13 | 16 | 24 | 40  | 57  | 69  | 56  |

| 14 | 17 | 22 | 29 | 51  | 87  | 80  | 62  |

| 18 | 22 | 37 | 56 | 68  | 109 | 103 | 77  |

| 24 | 35 | 55 | 64 | 81  | 104 | 113 | 92  |

| 49 | 64 | 78 | 87 | 103 | 121 | 120 | 101 |

| 72 | 92 | 95 | 98 | 112 | 100 | 103 | 99  |

出典：© 1993 ITU-T.

表8.2 色差量子化マトリックス  $Q_{uv}$  [367]

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 17 | 18 | 24 | 47 | 99 | 99 | 99 | 99 |

| 18 | 21 | 26 | 66 | 99 | 99 | 99 | 99 |

| 24 | 26 | 56 | 99 | 99 | 99 | 99 | 99 |

| 47 | 66 | 99 | 99 | 99 | 99 | 99 | 99 |

| 99 | 99 | 99 | 99 | 99 | 99 | 99 | 99 |

| 99 | 99 | 99 | 99 | 99 | 99 | 99 | 99 |

| 99 | 99 | 99 | 99 | 99 | 99 | 99 | 99 |

| 99 | 99 | 99 | 99 | 99 | 99 | 99 | 99 |

出典：© 1993 ITU-T.

U

↓

各ブロックDC係数をジグザクスキャンし

符号化（ハフマン符号、ランレンジス符号）

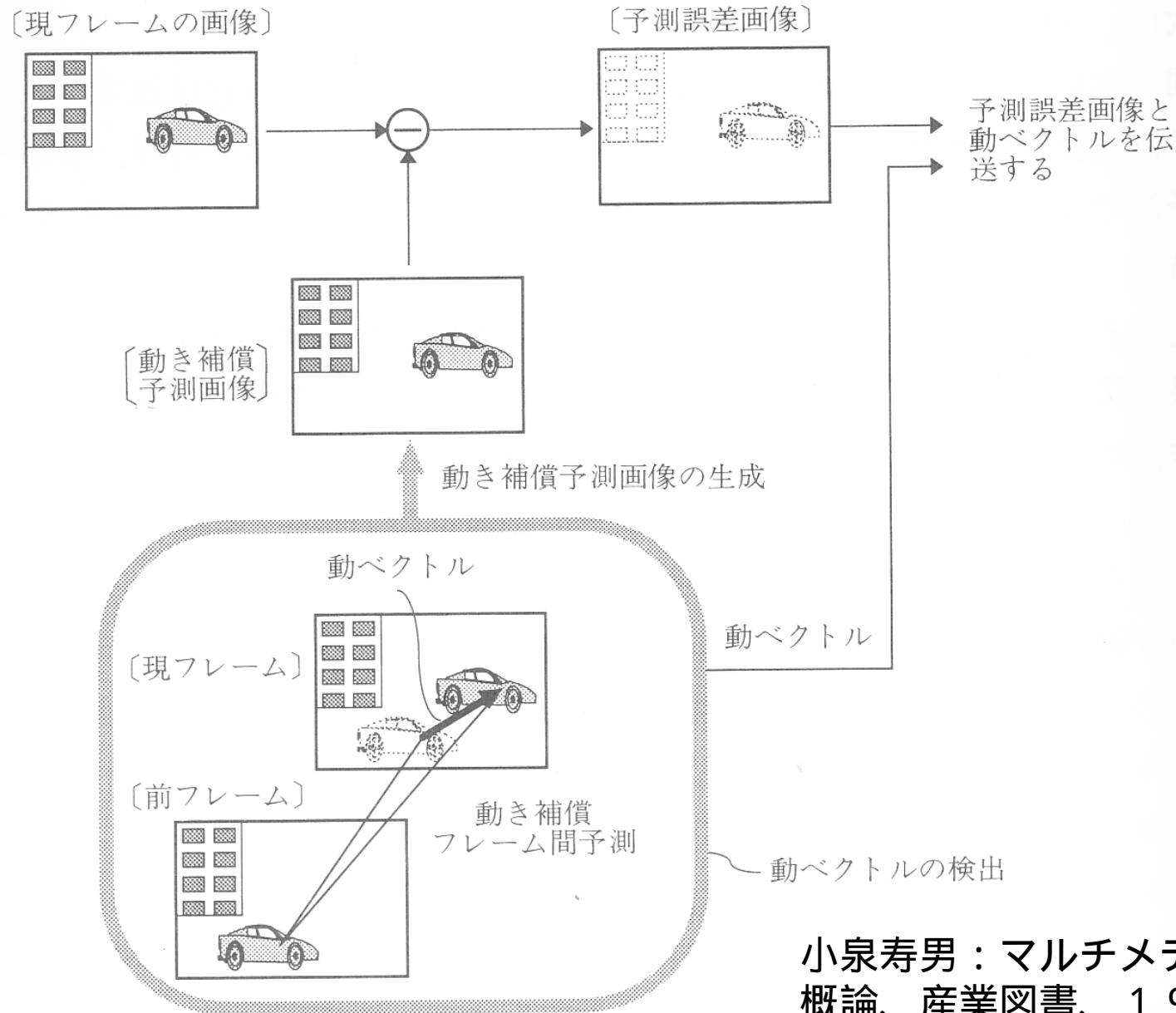

## 動き補償：フレーム間での圧縮

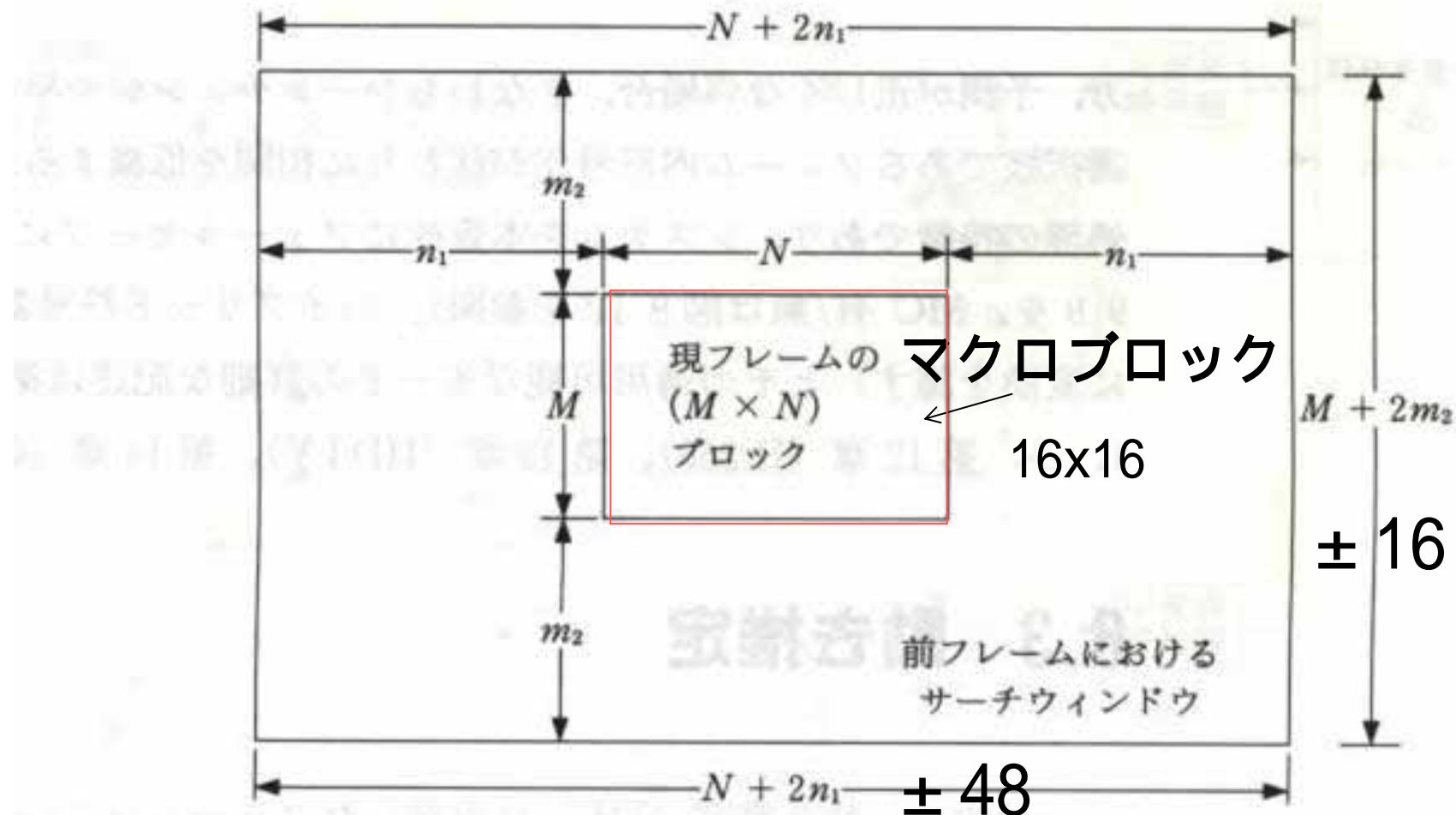

図 6.5 前フレームの  $(M + 2m_2) \times (N + 2n_1)$  のサーチウィンドウを用いた、 $(M \times N)$  ブロックの動き推定（全探索）。動きベクトル範囲はフレーム間距離あたり水平  $\pm n_1$  画素、垂直  $\pm m_2$  ラインである。

動き補償での演算量

マクロブロック当たり: ± 48,16画素領域

$$16 \times 16 \times 97 \times 33 \times 3 = 2458368 \text{演算}$$

マクロブロックサイズ

比較演算数

毎秒当たりのマクロブロック処理数:

$$45 \times 30 \times 30 = 40500$$

演算量: 1000億: 100G演算

フレーム数/秒

SSE (Streaming SIMD

Extension) :

128ビットデータに対する

単精度浮動小数点演算 × 4

グラフィックス処理

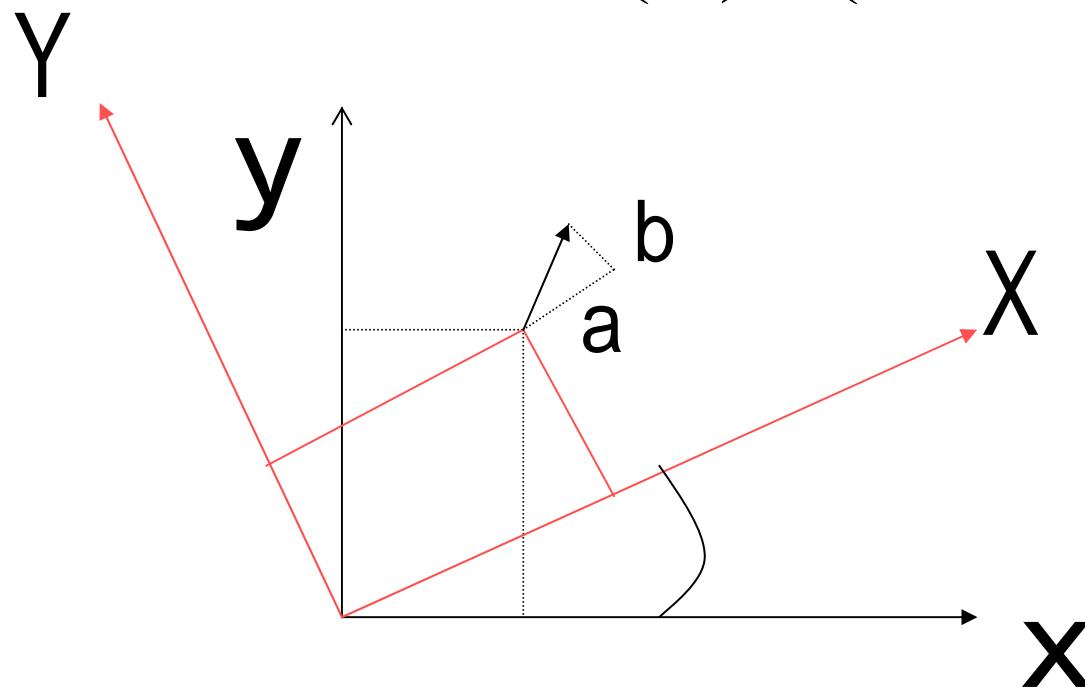

座標変換

$$(X, Y, Z, 1) = (x, y, z, 1) A$$

A: 4 × 4 行列

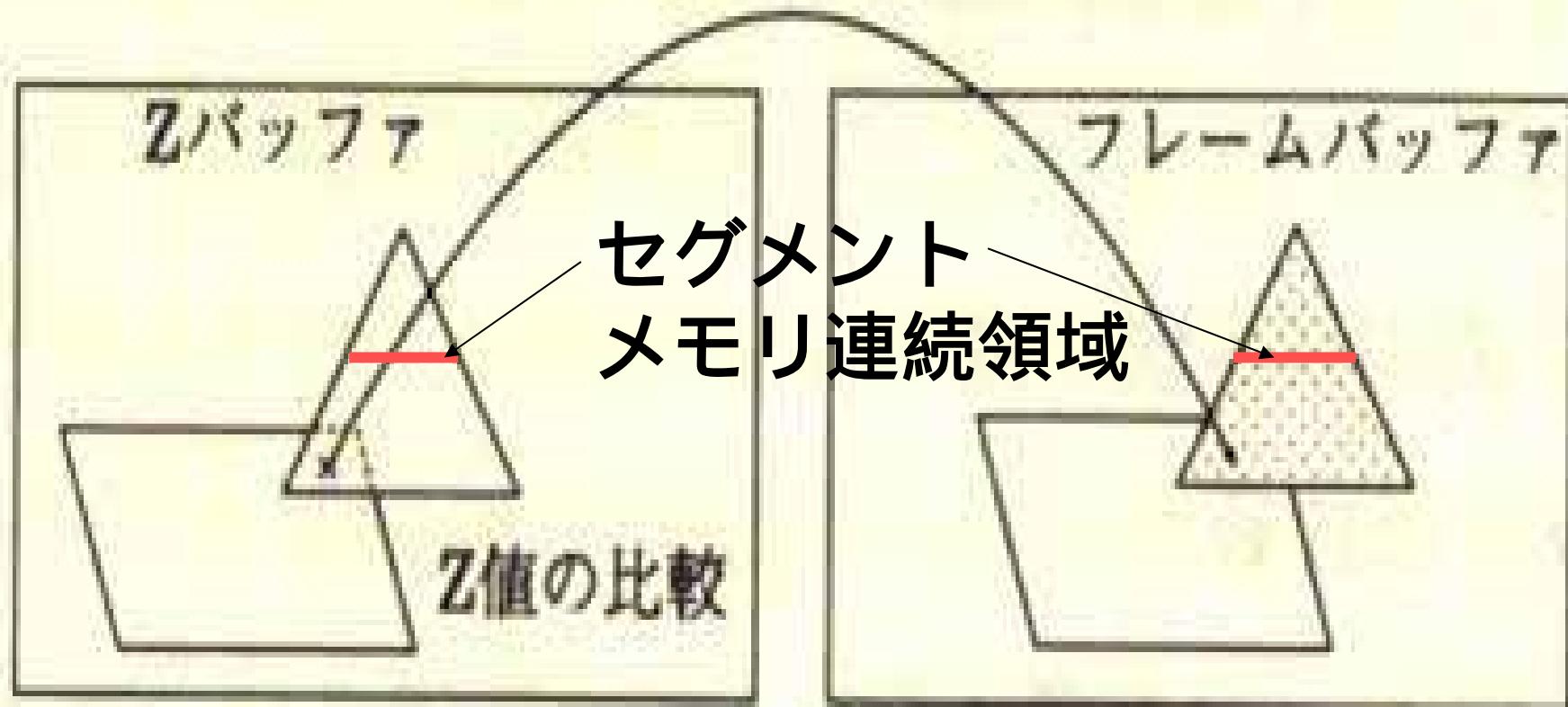

Zバッファによる隠れ面処理

# 座標変換

$$\begin{pmatrix} X \\ Y \\ 1 \end{pmatrix} = \begin{pmatrix} \cos\theta & \sin\theta & a \\ -\sin\theta & \cos\theta & b \\ 0 & 0 & 1 \end{pmatrix} \begin{pmatrix} x \\ y \\ 1 \end{pmatrix}$$

## 三角形のZ値 < 平行四辺形のZ値

隠れ面消去

図 6.15 Zバッファ法